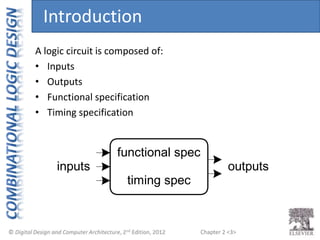

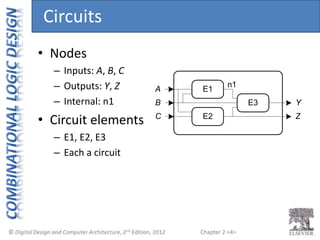

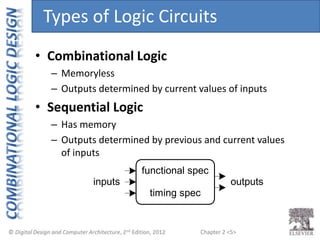

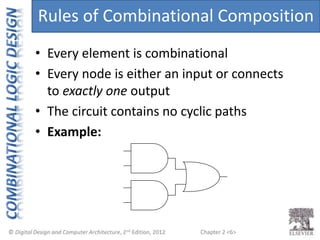

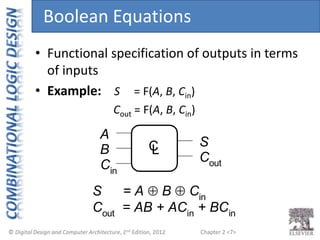

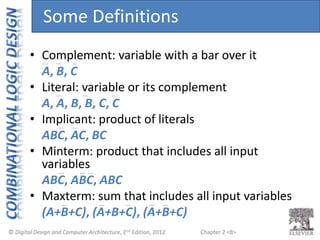

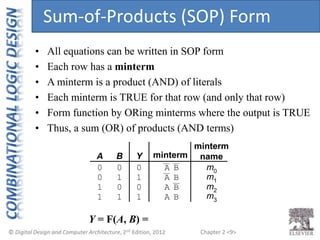

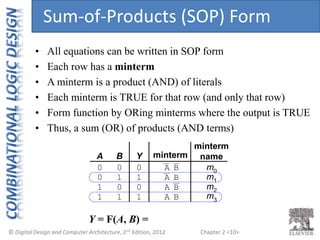

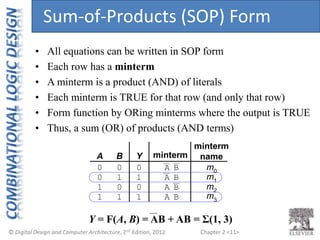

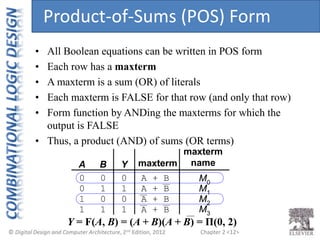

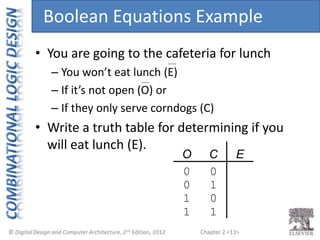

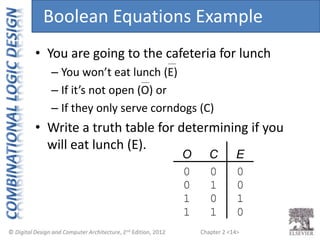

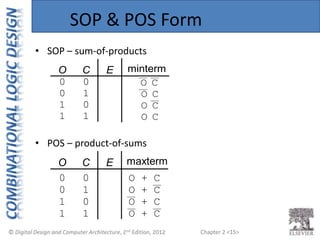

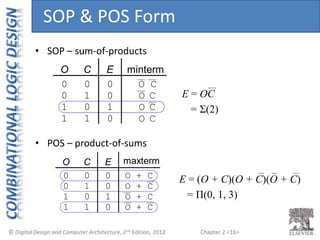

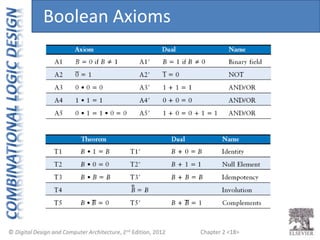

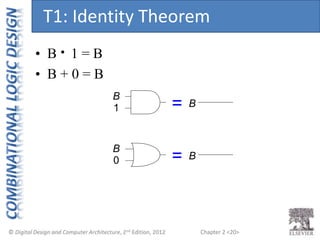

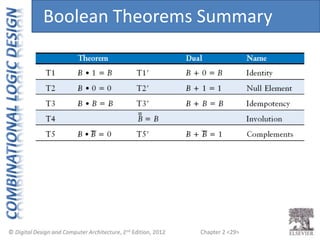

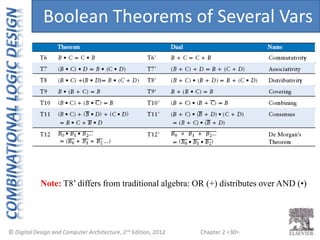

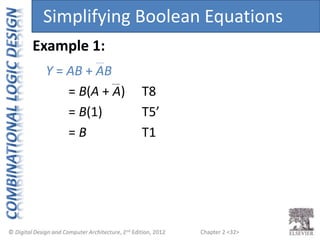

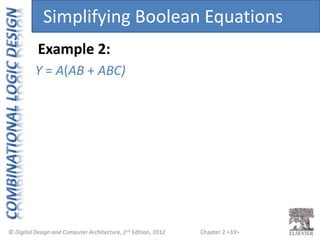

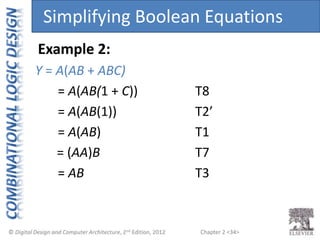

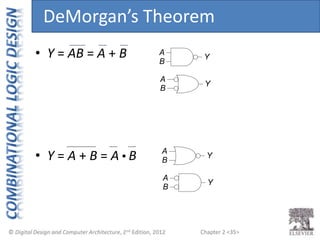

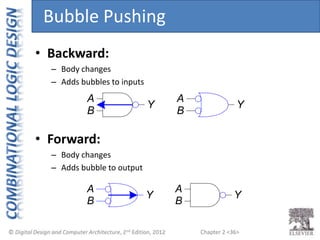

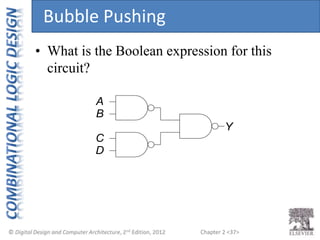

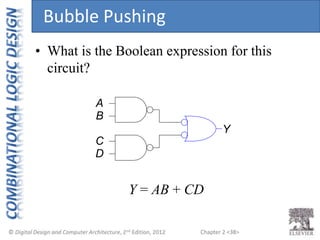

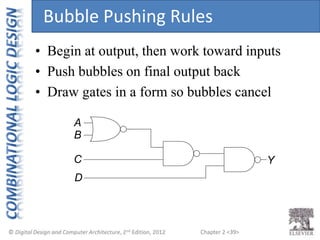

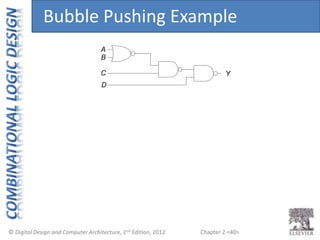

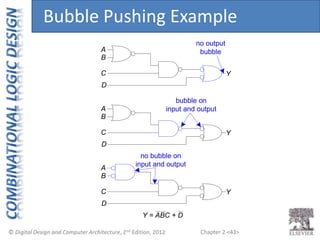

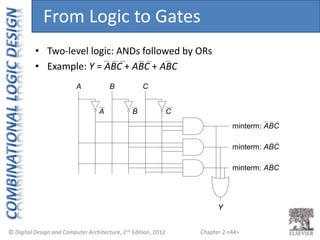

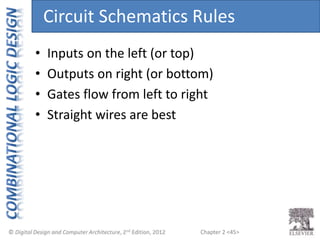

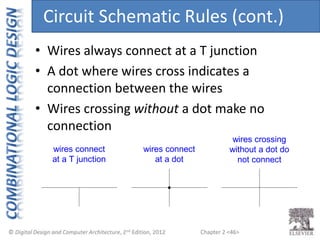

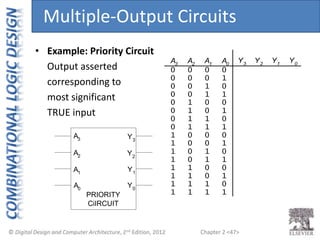

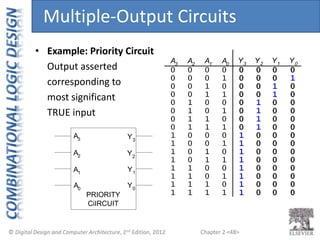

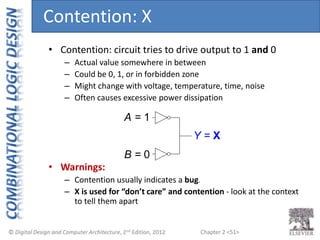

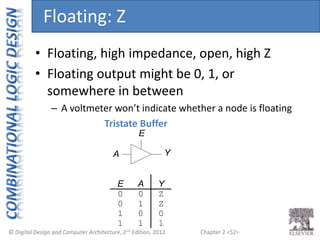

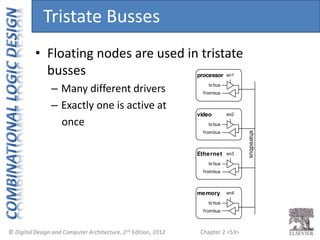

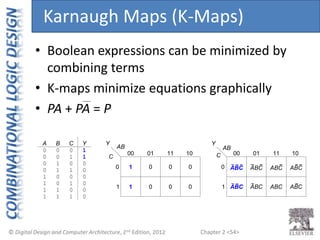

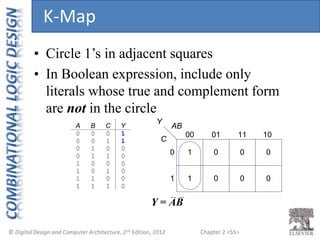

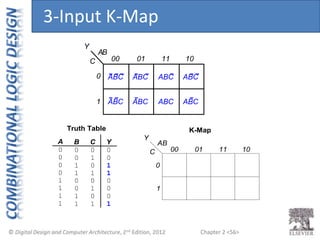

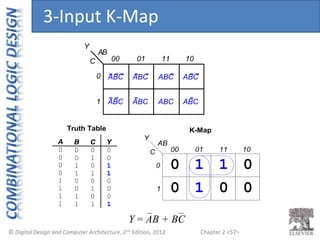

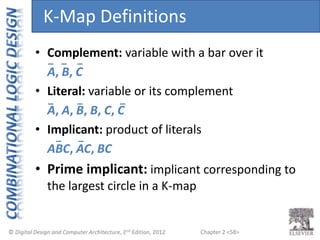

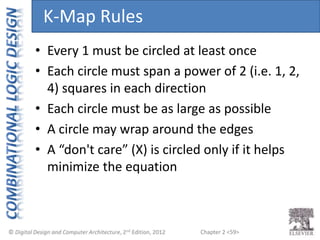

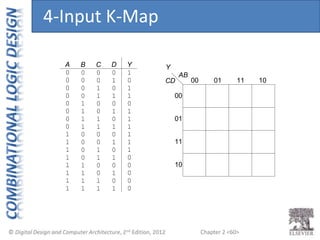

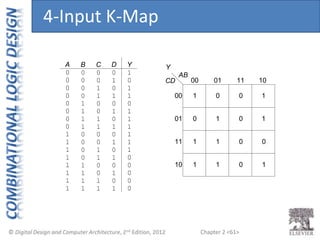

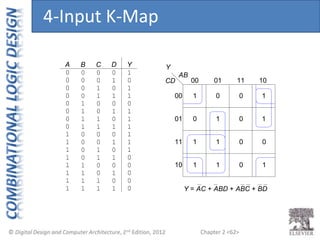

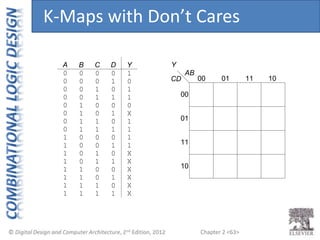

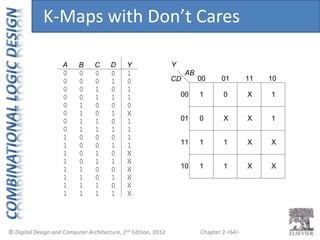

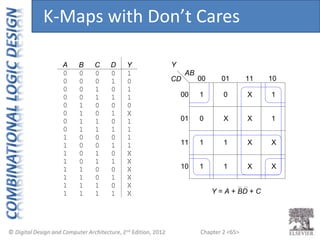

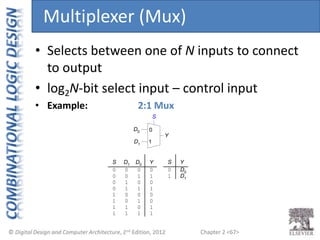

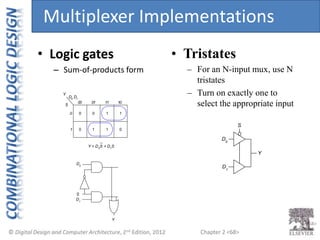

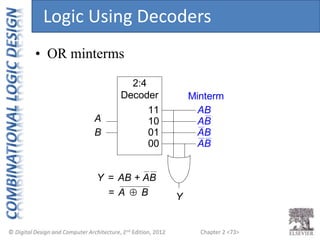

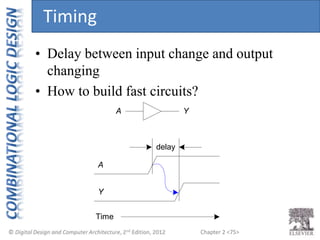

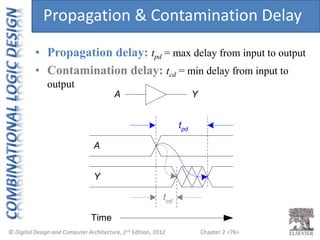

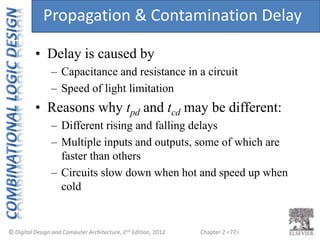

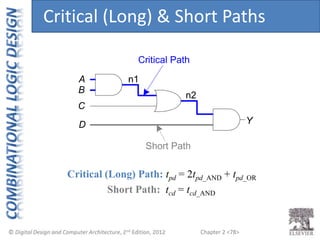

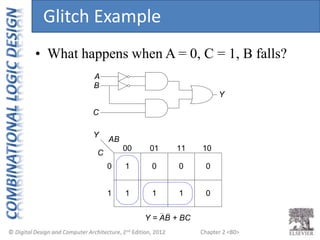

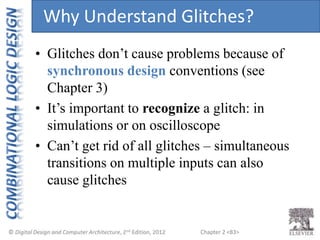

This document provides an overview of topics covered in Chapter 2 of the textbook "Digital Design and Computer Architecture". The chapter introduces basic concepts of logic circuits including inputs, outputs, functional specification and timing specification. It covers types of logic circuits such as combinational and sequential logic. The chapter also describes Boolean equations, Boolean algebra, Karnaugh maps and how to simplify Boolean expressions. It discusses implementing logic functions using logic gates and designing combinational logic circuits.