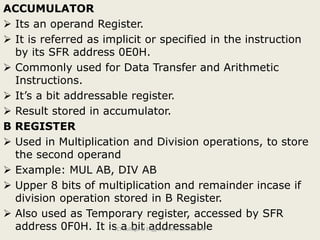

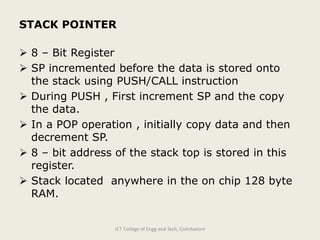

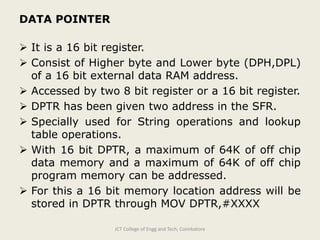

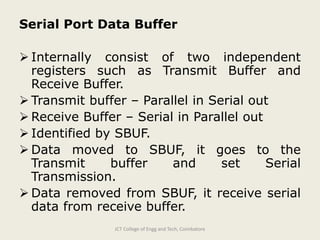

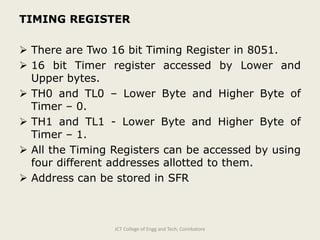

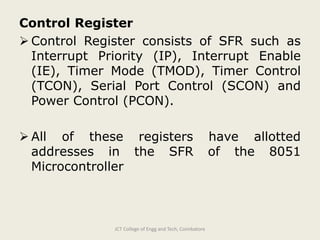

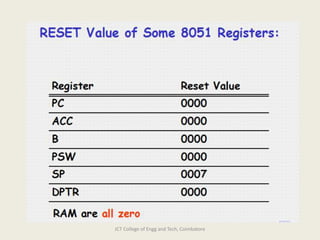

The document discusses the hardware architecture of the 8051 microcontroller. It describes the accumulator, B register, program status word, stack pointer, data pointer, ports 0-3, serial port data buffer, timing registers, and control registers. These components are special function registers that allow the 8051 to perform arithmetic operations, data transfer, program flow control, I/O interfacing, timing, and serial communication. The pin diagram and descriptions of the 8051 microcontroller are also provided.