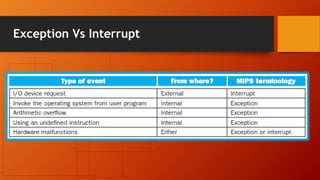

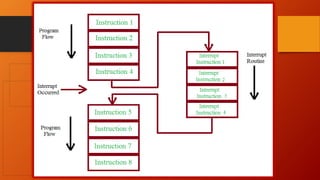

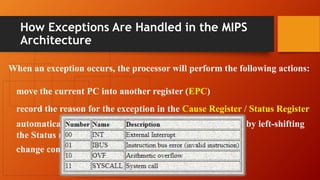

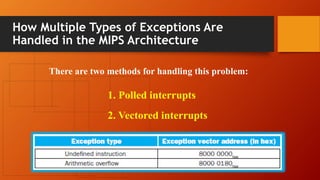

An exception is an unexpected event that occurs internally in the processor and disrupts program execution, while an interrupt is an external event that causes an exception. There are three types of exceptions: arithmetic overflow, undefined instruction, and system call. When an exception occurs, the processor saves the program counter, sets the cause register, disables further exceptions, and jumps to an exception handler. To return, the handler restores the program counter and reenables exceptions. Multiple exceptions can be handled with polled or vectored interrupts.