This document presents a design for an FPGA-based heart arrhythmia detection algorithm using Verilog HDL, which focuses on QRS complex detection within ECG signals. The approach employs the Ahlstrom and Tompkins method, validated through simulation with the MIT-BIH arrhythmia database, showcasing performance near the MATLAB output. The study emphasizes the practical implementation on FPGA hardware and the ability to analyze various arrhythmias based on heart rate intervals.

![Full Paper

ACEEE Int. J. on Information Technology, Vol. 3, No. 1, March 2013

FPGA based Heart Arrhythmia’s Detection Algorithm

Sheikh Md. Rabiul Islam, A. F. M. Nokib Uddin, Md. Billal Hossain, Md. Imran Khan

Dept. of Electronics and Communication Engineering

Khulna University of Engineering &Technology

Khulna, Bangladesh

E-mail: robi@ece.kuet.ac.bd,nokib.ece@gmail.com, billal.0709018@gmail.com, imrankhankuet@gmail.com.

Abstract- Electrocardiogram (ECG) signal has been widely used a human heart for detection of diseases [6]. To acquire the

for heart diagnoses .In this paper, we presents the design of signal, ECG devices with varying number of electrodes (3–

Heart Arrhythmias Detector using Verilog HDL based on been 12) can be used. Multi lead systems exceeding 12 and up to

mapped on small commercially available FPGAs (Field 120 electrodes are also available [7].

Programmable Gate Arrays). Majority of the deaths occurs

The QRS complex is the largest deflection voltage of about

before emergency services can step in to intervene. In this

research work, we have implemented QRS detection device 10 - 20 mV but may vary in size depending on age and sex of

developed by Ahlstrom and Tompkins in Verilog HDL. The the human. The amplitude of the voltage of the QRS complex

generated source has been simulated for validation and tested may also give information on heart disease [8]. Duration of

on software Verilogger Pro6.5. We have collected data from the QRS complex indicates the time for the ventricles to

MIT-BIH Arrhythmia Database for test of proposed digital depolarize and can provide information on problems

system and this data have given MIT-BIH data as an input of conduction in the ventricles as the bundle branch block.

our proposed device using test bench software. We have The MIT-BIH [9] arrhythmia database is used for

compared our device output with MATLAB output and performance evaluation based on the study. The MIT-BIH

calculating the error percentage and got desire research key

database contains 48 disks, each containing two channels of

point of RR interval between the peaks of QRS signal. The

proposed system also investigated with different database of ECG signals for 30 min duration of 24 hours selected from the

MIT-BIH for detect different heart Arrhythmias and proposed recordings of 47 individuals. There are also data numbers

device give output exactly same according to our QRS detection 116.137 QRS complexes in the database [10]. The database

algorithm. record contains both timing information and class information

heartbeat checked by independent experts [11].

Index Terms -Verilog HDL, QRS, ECG, MIT-BIH, Heart Xilinx ISE [12],[13] is a software tool produced by Xilinx

Arrhythmia. for synthesis and analysis of HDL designs, which enables

the developer to synthesize designs, examine RTL diagrams,

I. INTRODUCTION simulate a design’s reaction to different stimuli, and configure

Heart arrhythmias occurs when the electrical impulses in the target device with the programmer. The building block

heart that coordinate your heartbeats don’t work properly, were designed, tested and evaluated using the ISE tool

causing your heart to beat too fast, too slow or irregularly available from Xilinx & VeriloggerPro6.5 (TestBencher

[1]. Arrhythmias can take place in a healthy heart and be of pro)[14].

minimal consequence but they may also indicate a serious This paper is structured as follows. Section II describes

problem that may lead to stroke or sudden cardiac death [2- the QRS detection algorithm. Section III part A describes

3]. Heart arrhythmia treatment can often control or eliminate about the Ahlstrom and Tompkins algorithm and section B

irregular heartbeats. There are hundreds of different types of for Arrhythmias detection process. In Section IV part A

heart arrhythmias among them common arrhythmias are atrial describes the bus architecture and section B is for describing

fibrillation (AF), Premature Atrial Contractions (PAC), Atrial modules. Section V shows simulation and synthesized result.

Tachycardia, Atrial Fibrillation, Atrial Flutter, Premature Finally Section VI for conclusion.

Ventricular Contractions (PVC), Ventricular Tachycardia (VT),

Ventricular Fibrillation. II. QRS DETECTION ALGORITHM

Electrocardiogram (ECG) is a diagnosis tool that reported Till now, various methods have been reported by researchers

the electrical activity of heart recorded by skin electrode. for detection of QRS complex [15-18], Algorithms [19-21] are

The morphology and heart rate meditates the cardiac health based amplitude and the first derivative .In [20] a point is

of human heart beat [4]. It is a noninvasive technique [5]. classified as QRS candidate when three consecutive points

Any disorder of heart rate change in the morphological of the first derivative exceed a positive threshold (ascending

pattern is a reading of cardiac arrhythmia, after measure could slope) followed within the next 100ms by two consecutive

be detected by analysis of ECG waveform. Whatever the points which exceed a negative threshold (descending slope).

magnitude and duration of the P-QRS-T wave contains useful Algorithms [22] and [23] are based on the first derivative

information about the nature of the disease that affects the only. Algorithms [24-26] are based on the first and second

heart in this regard the electric wave is due to depolarization derivatives. Ahlstrom and Tompkins in [24] proposed that

and polarization king of Na + and blood of the body ions the absolute values of the first derivative are smoothed and

human [5].The ECG signal provides important information of added with the absolute values of the second derivative.

© 2013 ACEEE 9

DOI: 01.IJIT.3.1. 4](https://image.slidesharecdn.com/4-130304222440-phpapp01/85/FPGA-based-Heart-Arrhythmia-s-Detection-Algorithm-1-320.jpg)

![Full Paper

ACEEE Int. J. on Information Technology, Vol. 3, No. 1, March 2013

Balda [25] suggested searching values exceeding the TABLE I. HEART RATE AND R-R I NTERVAL FOR D IFFERENT HEART ARRHYTHMIA.

threshold in a weighted summation of the first and second

derivative, later this method was developed by Ahlstrom and

Tompkins [24]. Friesen [27] and Tompkins [28] also

investigated similar methods based on sensitivity of QRS

complex to noise. There is several QRS detection method

based on the digital filter [29-33], filter banks [34-35].

III. METHODOLOGY

A. Basic QRS Complexes Detection Algorithm

Among the so many algorithms we select first and second functions of a data bus to carry information and address bus

derivative based scheme developed by Ahlstrom and to determine where it should be sent and a control bus to

Tompkins [24] the rectified first derivative is calculated from determine its operation .The Bus architecture of the proposed

the ECG: digital system is shown in Figs.1-3.

Y0(n)=ABS[X(n+1)-X(n-1)] 3<n<8188

the rectified first derivative is then smoothed:

Y1(n)=[Y0(n-1)+2Y0(n)+Y0(n+1)]/4 3<n<8188

The rectified second derivative is calculated:

Y2(n)=ABS[X(n+2)-2X(n)+X(n-2)] 3<n<8188

The rectified smoothed first derivative is added to the

rectified second derivative:

Y3(n)=Y1(n)+Y2(n) 3<n<8188

The maximum value of this array is determined and scaled

to serve as primary and secondary thresholds:

Primary threshold=0.8*max[Y3(n)] 3<n<8188

Secondary threshold=0.1*max[Y3(n)] 3<n<8188

The array of the summed first and second derivative is

scanned until a point exceeds the primary thresholds. In order

to be classified as a QRS candidate, the next consecutive

point must all meet or exceed the secondary threshold. That

is the threshold and QRS detection algorithm is just like bellow: Fig. 1. Block diagram of the system including data bus.

Y3(i) >= primary threshold, and

Y3(i+1), Y3(i+2) . . . . . . Y3(i+6) > secondary threshold

After detecting the QRS complex we detect the R peak

and R-R interval. There are several types of noise (i.e. muscle

artifact, electrode motion artifact, white noise etc.) may

hamper the ECG signal as well as the performance also.

Performance of first and second derivative based method is

much better than the first derivative methods [36].

B. Arrhythmias Detection

For detection of Arrhythmias at first we need to know the

heart rate of different Arrhythmias. Bellow table shows the

heart rate for different arrhythmias. If the sampling frequency

Fs Hz then, Time for one sample Ts= second

If R-R interval (in sample) is N samples then,

R-R interval (in time) = Ts N second Fig. 2. Block diagram of the system including control bus and

After calculating R-R interval we can detect heart internal structure

Arrhythmia from Table. I. In our system input and output is unidirectional to data

bus. Input block take input data from data source and send it

IV. PROPOSED ARCHITECTURE to data bus. Output block take data from data bus and show

A. Bus Architecture the output data.RAM, register A, register B and ALU are

bidirectional that is it can send and receive data from data

A system bus is a single computer bus that connects the

bus. In control bus architecture shown in Fig.2, control block

major components of a computer system. It combines the

determines the operation of rest of the block using control

© 2013 ACEEE 10

DOI: 01.IJIT.3.1. 4](https://image.slidesharecdn.com/4-130304222440-phpapp01/85/FPGA-based-Heart-Arrhythmia-s-Detection-Algorithm-2-320.jpg)

![Full Paper

ACEEE Int. J. on Information Technology, Vol. 3, No. 1, March 2013

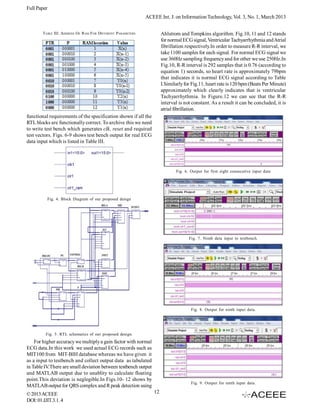

TABLE IV. C OMPARE BETWEEN VERILOG T ESTBENCH AND MATLAB O UTPUT The proposed model is loaded on XILINX FPGA board. It is

implemented upon XILINX SPARTAN XC2S150 FPGA board

processor. When it is implemented on FPGA board processor

then the clock frequency of the processor is 1MHZ. The

proposed model has the same power consumption, signal

bandwidth and CMOS technology is used on the XC2S150

processor.

CONCLUSIONS

We have coded the equations of Ahlstrom and Tompkins

method using Verilog Hardware Description Language. Try

to detect the peak of two consecutive ECG waveform, found

the time interval of R-R is detected. Compare with the time

interval of R-R of normal cardiac conditions, the abnormalities

of heart rate is determined. Some heart arrhythmias depends

not only the R-R interval but also P, T wave. Our system

can’t detect those kinds of arrhythmias. We use

VeriloggerPro6.5 (Test Bencher pro) demo version which has

a limitation that it cannot simulate over 1225 line and show

more than 26 consecutive outputs correctly. In future we will

try to update our system for calculating floating point data

and also use licence version of VHDL.

REFERENCES

[1] Sandoe E, Sigurd B. Arrhythmia–—a guide to clinical

electrocardiology. Bingen: Publishing Partners Verlags GmbH,

1991.

[2] Goldberger L, Goldberger E. Clinical electrocardiography. Saint

Louis: The Mosby Company, 1977.

Fig. 10. R peak detection for normal ECG signal

[3] Sideris DA, Primary cardiology. Athens: Scientific Editions

Grigorios K Parisianos, 1991 (in Greek).

[4] J. Pan, W. J. Tompkins, “A real time QRS detection algorithm,”

IEEE Trans. Biomed. Eng., vol. 32, pp. 230–236, 1985.

[5] Y.C. Yeha, and W. J. Wang, “QRS complexes detection for ECG

signal The Difference Operation Method (DOM),” Computer

methods and programs in biomedicine, vol. 9, pp. 245–254,

2008.

[6] P.de Chazal, M.O. Duyer, and R.B. Reilly, “Automatic

classification of heartbeat using ECG morphology and heart

beat interval features,” IEEE Trans. Biomed. Eng. vol. 51, pp.

1196-1206, 2004.

[7] P. Zarychta, F. E. Smith, S. T. King, A. J. Haigh, A. Klinge, D.

Zheng, S. Stevens, J. Allen, A. Okelarin, P. Langley, and A.

Fig. 11. R peak detection for Ventricular Tachyarrhythmia Murray, “Body surface potential mapping for detection of

myocardial infarct sites,” in Proc. IEEE Comput. Cardiol.,

Sep./Oct. 2007, pp. 181–184.

[8] P. de Chazal, R.B. Reilly, “A patient-adapting heartbeat classifier

using ECG morphology and heartbeat interval feature,” IEEE

Trans. Biomed. Eng. vol. 53, pp. 2535-2543, 2006.

[9] D. A. Coast, R. M. Stern, G. G. Vano and S. A. Biller, “An

approach to cardiac arrhythmia analysis using Hidden Markov

Model, “ IEEE Trans. Biomed. Eng., vol. 37, no. 9, Sep. 1990.

[10] R. J. Schalkoff, “Pattern Recognition: Statistical, Structural,

and Neural Approaches”, JOHN WILEY & SONS, INC., 1992.

[11] T. H. Yeap, F. Johnson, and M. Rachniowski, “ECG beat

classification by a neural network,” in Proc. Annu. Int. Conf.

IEEE Engineering Medicine and Biology Society, 1990, pp.

1457–1458.

Fig. 12. R peak detection for atrial fibrillation. [12] Samir palnitkar; ‘Verilog HDL.’ SUNSOFT PRESS 1996.

© 2013 ACEEE 13

DOI: 01.IJIT.3.1. 4](https://image.slidesharecdn.com/4-130304222440-phpapp01/85/FPGA-based-Heart-Arrhythmia-s-Detection-Algorithm-5-320.jpg)

![Full Paper

ACEEE Int. J. on Information Technology, Vol. 3, No. 1, March 2013

[13] XILINX, Internet site address: http://www.xilinx.com [30] W. A. H. Engelse and C. Zeelenberg, “A single scan algorithm

[14] TestBencher pro Internet site address: http:// for QRS detection and feature extraction,” IEEE Comput.

www.syncad.com. Cardiology. Long Beach, CA: IEEE Computer Society, pp.

[15] M. Benmalek, A. Charef, “Digital fractional order operators 37-42, 1979.

for R-wave detection in electrocardiogram signal,” IET Signal [31] P. S. Hamilton and W .J. Tompkins, “Quantitative investigation

Processing, vol. 3, no. 5, pp. 381-391, Sept. 2009. of QRS detection rules using the MIT/BIH arrhythmic

[16] Q. Z. Xie, Y. H. Hu, and W. J. Tompkins, “Neural-network database”, IEEE Trans. Biomed. Eng., vol. 33, pp. 1157-1165,

based adaptive matched filtering of QRS detection,” IEEE 1986.

Trans. Biomed. Eng., vol. 39, pp. 317-329, 1992. [32] L. Keselbrener, M. Keselbrener, and S. Akselrod, “Nonlinear

[17] J. Pan and W. J. Tompkins, “A real-time QRS detection high pass filter for R-wave detection in ECG signal”, Med.

algorithm”, IEEE Trans. Biomed. Eng., vol. 32, pp. 230-236, Eng. Phys., vol. 19, no. 5, pp. 481-484, 1997.

1985. [33] S. Suppappola and Y. Sun, “Nonlinear transforms of ECG

[18] Fei Zhang, Yong Lian, “QRS Detection based on multiscale signals for digital QRS detection: A quantitative analysis”,

mathematical morphology for wearable ECG devices in body IEEE Trans. Biomed. Eng., vol. 41, pp. 397-400, 1994.

area networks,” IEEE Trans. on Biomed. Circuits and Systems, [34] V. X. Afonso, W. J. Tompkins, T. Q. Nguyen and S. Luo,

vol. 3, no. 4, pp. 220-228, Aug. 2009. “ECG beat detection using filter banks,” IEEE Trans. Biomed.

[19] J. Fraden and M. R. Neumann, “QRS wave detection”, Med. Eng., vol. 46, pp.192-202, 1999.

Biol. Eng. Comput., vol. 18, pp 125-132, 1980. [35] Stéphane Mallat, “A Wavelet Tour of Signal Processing”, 3rd

[20] P.M.Mahoudeaux,” Simple microprocessor-based system for ed., Academic Press, 2008.

on-line ECG analysis, “Med. Bio. Eng. Comput.,vol.19,pp [36] Gary M., Friesen, Thomas C. Jannett, Manal Afify Jadallah,

497-500,1981 Stanford L.Yates, Stephen R. Quint, H. Troy Nagle,” A

[21] D.Gustafson, “Automated VCG Interpretation studies using Comparison of the Noise Sensitivity of Noise QRS Detection

signal analysis techniques,” R-1044 Charles Stark Draper Algorithms,” IEEE TRANSACTIONS ON BIOMEDICAL

Lab.,Cmabridge,MA,1977 ENG.,VOL.37,PP.95-96.

[22] A. Menred, “Dual microprocessor system for cardiovascular

data acquisition, processing and recording, “in Proc.1981 IEEE AUTHOR BIOGRAPHIES

Int. Conf. Industrial Elect. Contr. Instrument.,1981,pp.64-69

[23] W.P. Holsimger , “A QRS pre-processor based on digital Sheikh Md. Rabiul Islam received the B.Sc.in Engg.

differentiation” IEEE Trans. Biomed. Eng.,vol.BME- (ECE) from Khulna University, Khulna, Bangladesh

18,pp.212-217,1971 in December 2003, and M.Sc. in Telecommunication

[24] M.L. Ahlstrom and W J. Tompkins, “Automated high-speed Engineering from the University of Trento, Italy, in

analysis of holter taps with microcomputers,” IEEE Trans.

Biomed. Eng., vol. BME-30,pp.651-657,Oct.1983 October 2009. He joined as a Lecturer in the department of Elec-

[25] BALDA R. A. “The HP ECG analysis program” in tronics and Communication Engineering of Khulna University of

VANBEMNEL J. H. and WILLEMS J.L. (Ed): ‘Trends in Engineering & Technology, Khulna, in 2004, where he is currently

Computer- Process Electrocardiograms’ , (North Holland), pp. an Assistant Professor in the same department in the effect of

197-205, 1977 2008. He has published 15 Journals and six international confer-

[26] R. M. Rangayyan, “Biomedical signal analysis: a case-study ences.. His research interests include Numerical analysis, VLSI,

approach”, IEEE Press, 2001. wireless communications , signal & image processing, and biomedi-

[27] G. M. Friesen, T. C. Jannett, M. A. Jadallah, S. L. Yates, S. R. cal engineering.

Quint and H. T. Nagle, “A comparison of the noise sensitivity A. F. M. Nokib Uddin received a B.Sc. Engg. (ECE) of

of nine QRS detection algorithms”, IEEE Trans. Biomed. Eng., department of Electronics and Communication Engineering at

vol. 37, pp. 85-97, 1990. Khulna University of Engineering & Technology, Khulna_9203,

[28] W. J. Tompkins, “Biomedical digital signal processing”, Bangladesh.

Prentice-Hall, Upper Saddle River, NJ, 1995. Md.Billal Hossain received a B.Sc. Engg.(ECE) of department

[29] M. Okada, “A digital filter for the QRS complex detection,” of Electronics and Communication Engineering at Khulna University

IEEE Trans. Biomed. Eng., vol. 26, pp. 700-703, Dec. 1979. of Engineering & Technology, Khulna_9203, Bangladesh.

Md. Imran Khan received a B.Sc. Engg. (ECE)of department of

Electronics and Communication Engineering at Khulna University

of Engineering & Technology, Khulna_9203, Bangladesh

© 2013 ACEEE 14

DOI: 01.IJIT.3.1. 4](https://image.slidesharecdn.com/4-130304222440-phpapp01/85/FPGA-based-Heart-Arrhythmia-s-Detection-Algorithm-6-320.jpg)