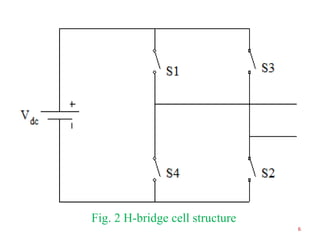

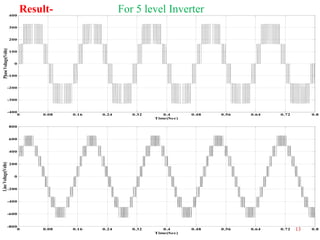

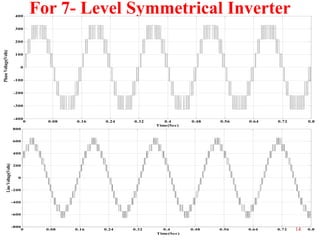

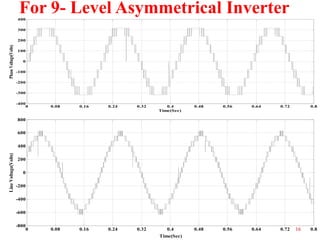

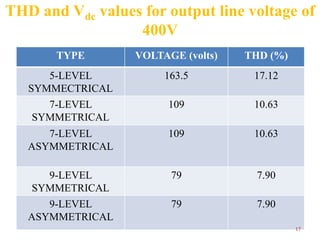

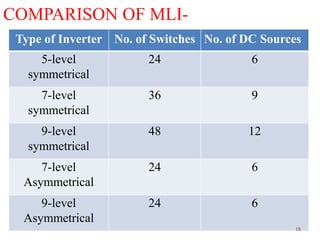

The document presents research on asymmetrical cascaded H-bridge multilevel inverters. It summarizes the structure and operation of 5-level, 7-level symmetrical, and 7-level and 9-level asymmetrical configurations. Simulation results show that asymmetrical configurations reduce harmonics without increasing components compared to symmetrical configurations. The conclusion is that asymmetrical multilevel inverters can produce more output levels without adding components by using different progression factors.