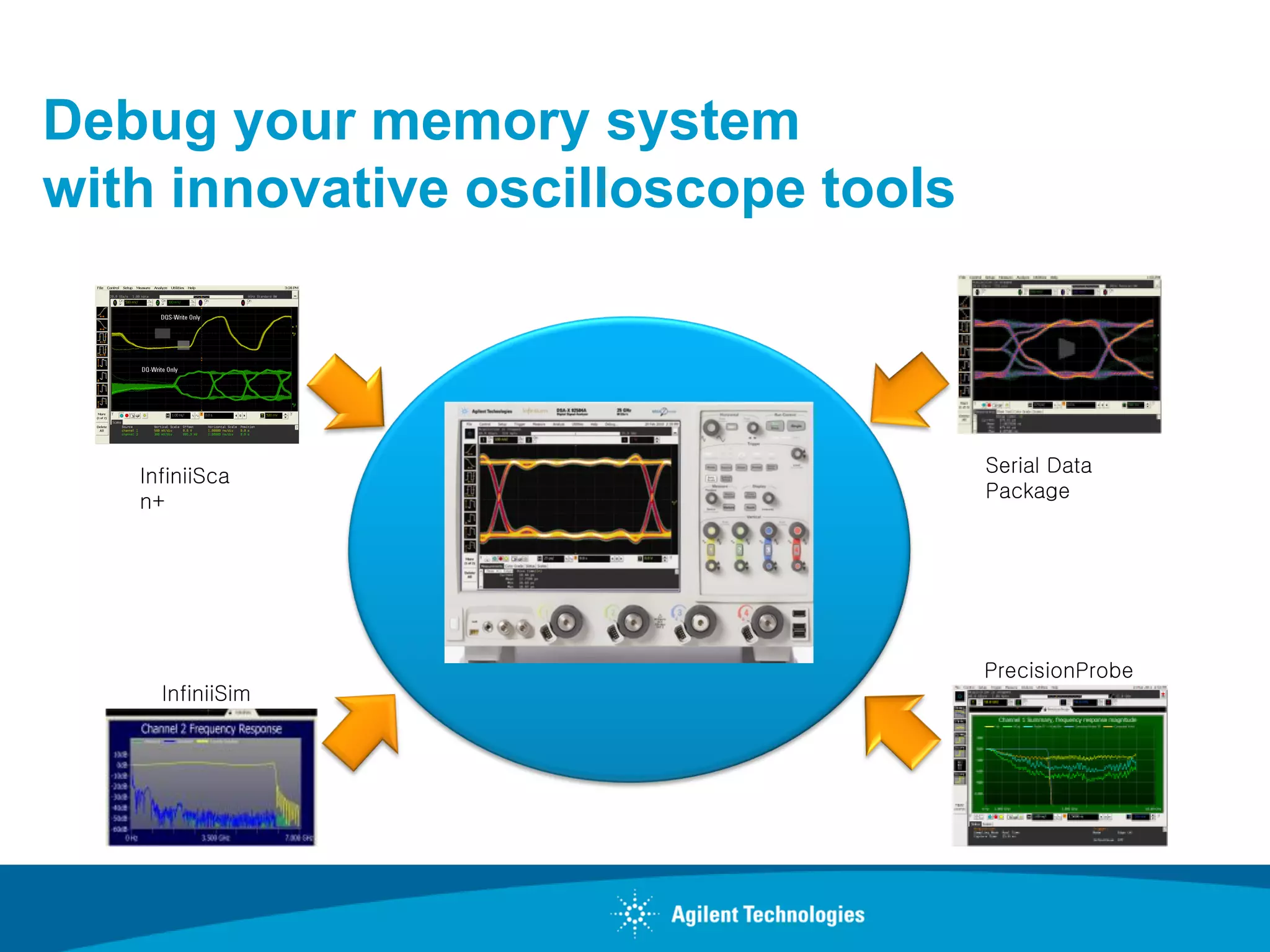

The document discusses challenges in probing memory systems and introduces tools like PrecisionProbe fixtures and de-embedding software to maximize probe performance and provide accurate measurements by removing probing effects. It covers probing DDR memory at different design phases, how to trigger and measure signals, and techniques for analyzing measurements against JEDEC specifications.