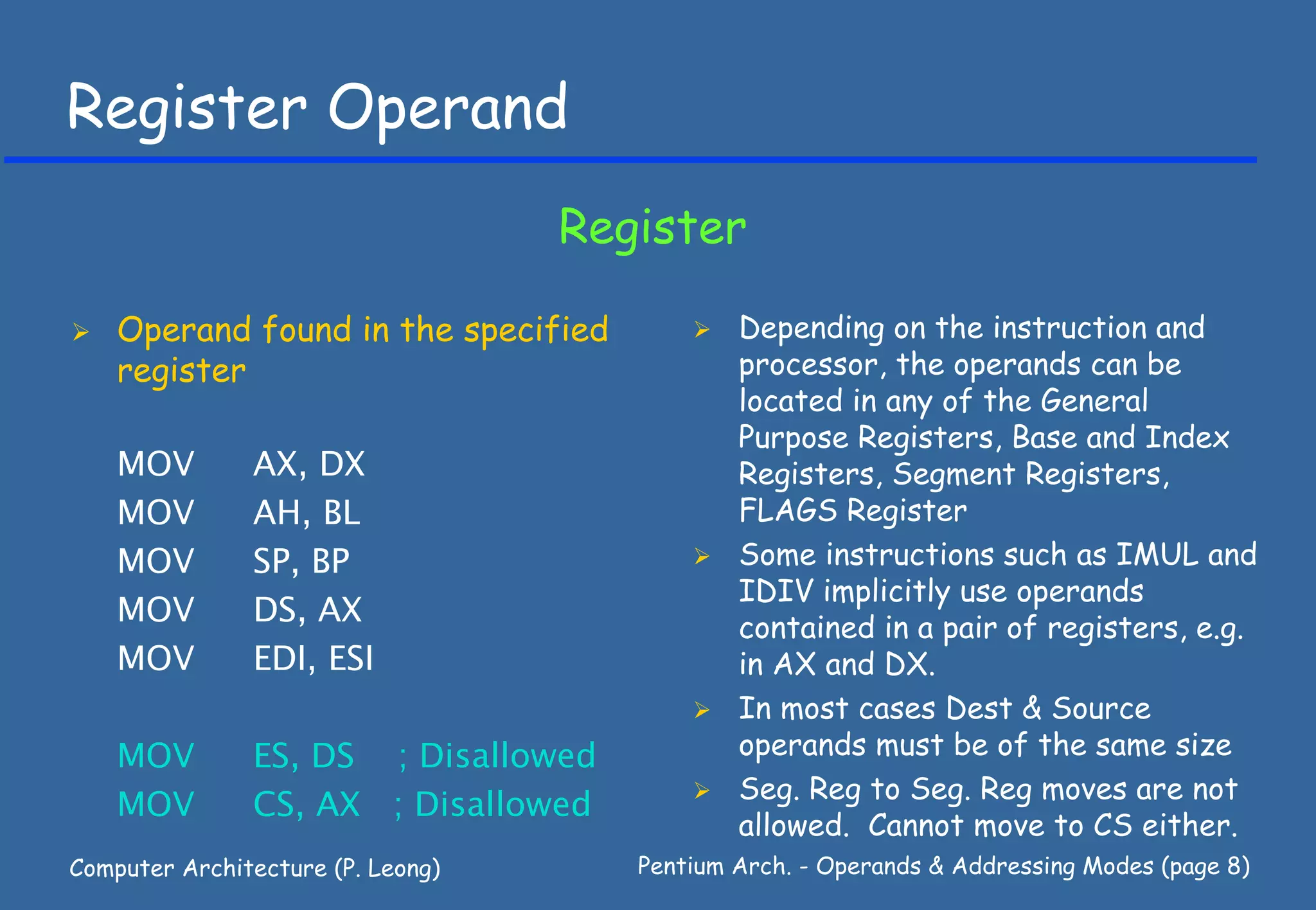

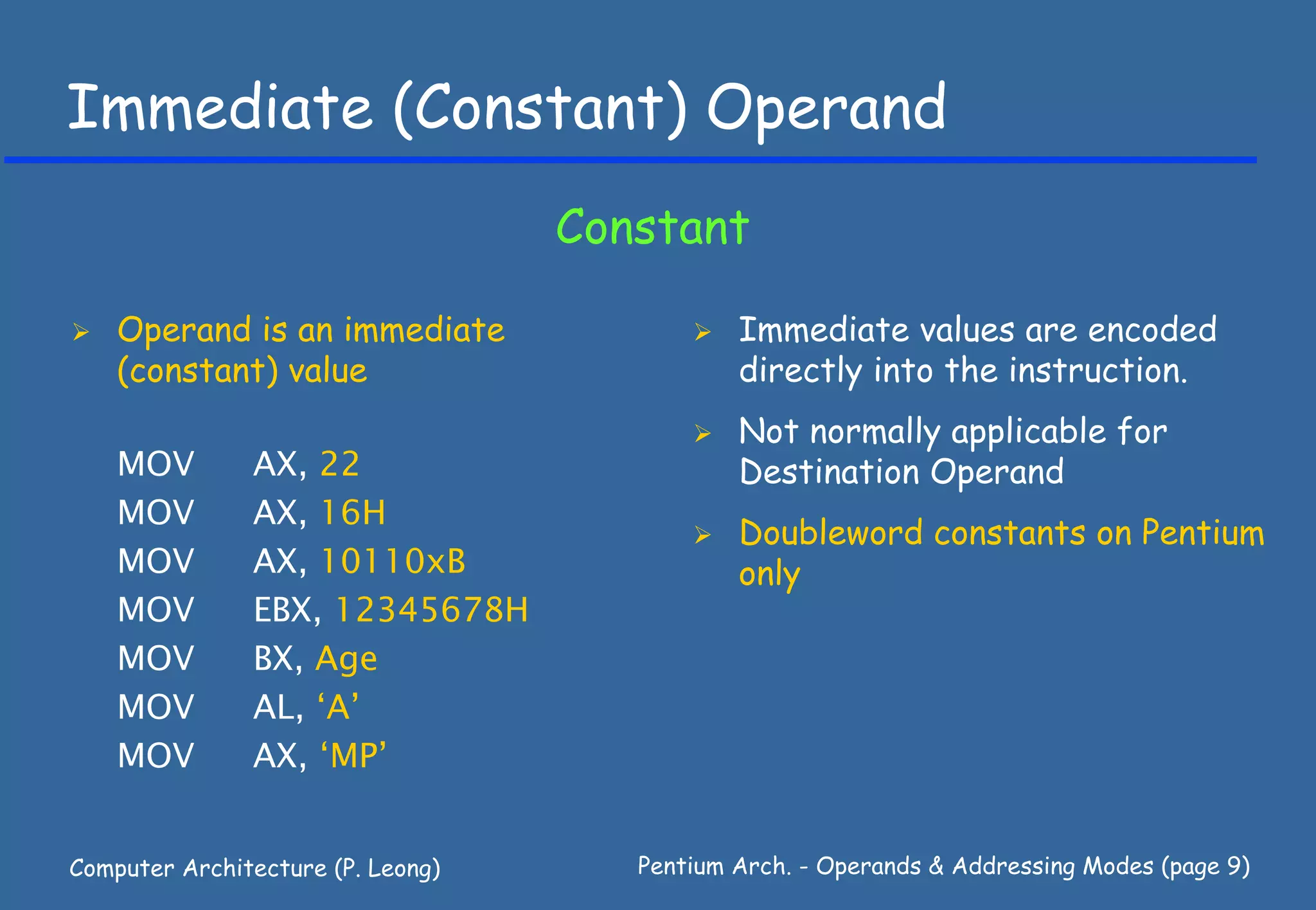

This document discusses operands and addressing modes in computer architecture. It describes different types of operands including register operands that specify a register, immediate operands that specify a constant value, and memory operands that specify an address using a base register, index register, scale, and displacement. It also describes different addressing modes like direct addressing that uses a displacement and register indirect addressing that uses the contents of a base register as an offset.

![Addressing modes

addr is address field of instruction

Immediate addr is operand

Register addr is register number in CPU

– operand := [ addr ]

Direct addr is address in primary (main) memory

– operand := [ addr ]

Indirect addr is register number (or memory address)

– operand_address := [ addr ]

operand [ operand_address ]

Indexed addr is base address, index is a register

– operand := [ addr + [ index ] ]

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 2)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-2-2048.jpg)

![Operands (Addressing Modes)

Register Operands

e.g. EAX, DX, AL, SI, BP, DS

Immediate Operands (Constants)

e.g. 23, 67H, 101010xB, ‘R’, ‘ON’

Memory Operands

[ BaseReg + Scale * IndexReg + Displacement ]

e.g. [24], [BP], [ESI+2], [BP + 8 * DI + 16]

Source and Destination operands cannot both be a memory operand.

Note: Some instructions use particular registers implicitly.

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 4)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-4-2048.jpg)

![Examples

Label Instruction Comment

MOV AH, CL ; AH := CL

ADD AX, [BX] ; AX := AX + Memory [DS:BX]

MOV AX, [BP+4] ; AX := Memory[SS:BP+4]

ADD AX, ES:[BX] ; AX := AX + Memory [ES:BX]

SUB EAX, 45 ; EAX := EAX - 45

MOV BYTE PTR [BX] , 45 ; Memory [DS:BX] := 45

ADD CH, [22] ; CH := CH + Memory [DS:22]

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 6)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-6-2048.jpg)

![Memory Operands

Specify an address offset (effective address) using expressions of the

form (different parts of expression are optional):

[ Base Register + Scale * Index Register + Displacement ]

1) Base Register (EAX, EBX, ECX, EDX, ESP, EBP, EDI, ESI)

(only BX or BP on 8086)

2) Index Register (EAX, EBX, ECX, EDX, EBP, EDI, ESI)

(only SI or DI on 8086)

Scale 2 or 4 or 8 (Pentium only)

3) Displacement (constant value)

Size of operand is normally inferred from Instruction or 2nd operand if

register. We can explicitly prefix operand with BYTE PTR or WORD PTR

or DWORD PTR.

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 10)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-10-2048.jpg)

![Default Segments

Type of Default Default Selection Rule

Reference Segment

Data Data (DS) All data references, except

stack references & string instruction

destination references

Stack Stack (SS) All stack pushes & pops (via ESP)

References which use EBP

as Base Register

String Dest Extra (ES) Destination operand of string

instructions.

Instructions Code (CS) All instruction fetches

Default Segments can usually be overridden e.g. ES:[EBP+2]

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 11)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-11-2048.jpg)

![Displacement (Direct Addressing)

[ Displacement ]

Specified constant value (called Displacements are encoded

the displacement) gives offset. directly into the instruction.

Allows global variables with fixed

MOV AX, [22] offset values to be addressed

MOV AX, ES:[22] directly.

MOV [16H] , AX

MOV BYTE PTR [22] , 98

MOV EBX, [12345678H]

MOV CX, Users

MOV [MyPointer], AH

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 12)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-12-2048.jpg)

![Example 1: MOV AX, [22]

AX

-637

Data Segment

(e.g. DS * 16) 0

+22 2 ...

22

22 -637

Instruction

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 13)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-13-2048.jpg)

![Example 2: MOV AX, ES:[22]

AX

+738

Extra Segment

(e.g. ES * 16) 0

+22 2 ...

22

22 +738

Instruction

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 14)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-14-2048.jpg)

![Example 3: MOV BYTE PTR [22], 98

Instruction

98

Data Segment

(e.g. DS * 16) 0

+22 2 ...

22

22 98

Instruction

24 MOV WORD PTR [26], 99

26 99

99

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 15)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-15-2048.jpg)

![Base (Register Indirect)

[ Base ]

Contents of specified Base Pentium: EAX, EBX, ECX, EDX,

Register gives offset. ESP, EBP, EDI, ESI

8086: BX, BP, DI, SI

MOV AX, [BX]

MOV [BP], AL Since the value in the Base

MOV AX, [DI] Register can be updated, it can

MOV [SI] , AH be used to dynamically address

(point to) variables in memory,

MOV EBX, [ESI]

e.g. array elements, linked lists,

MOV [EAX], ECX trees.

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 16)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-16-2048.jpg)

![Example 1: MOV AX, [BX]

AX

-100

Data Segment

0

2

+66 ...

BX 66 -100

66

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 17)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-17-2048.jpg)

![Example 2: MOV [BP], AL

AL

55

Stack Segment

(e.g. SS * 16) 0

2

+12 ...

BP 12 55

12

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 18)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-18-2048.jpg)

![Base + Displacement (Register Relative)

[ Base + Displacement ] or Displacement [ Base ]

Sum of specified Base Register Pentium: EAX, EBX, ECX, EDX,

and Displacement gives offset. ESP, EBP, EDI, ESI

Displacement can be negative. 8086: BX, BP, DI, SI

Can be used to access record

MOV AX, [BX+4] fields, e.g. Base Register = start of

MOV [BP+2] , DH record, Displacement = position of

MOV AX, [DI–6] field.

MOV DL, [SI+Age] Can be used to access array

elements, e.g. Displacement = start

MOV AH, [EAX+12] of array, Base Register = position

MOV List [BX] , CX of element

MOV DX, List [BP–2] Can be used to access parameters

& local variables.

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 19)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-19-2048.jpg)

![Example 1: MOV AX, [BX+4]

AX

2244

Data Segment

0

BX 2

+12 ...

12 BX points to Start

of a Record with

+4 12 X fields X, Y & Z

Y

4 +4 selects field Z

16 2244

Instruction

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 20)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-20-2048.jpg)

![Example 2: MOV AX, [BX+4]

AX

Data Segment

-99

+4 0

2

Instruction

4 A[0]

+4 6 A[1]

+12 8 A[2] +4 points to start of

10 A[3] an Array

BX 12 A[4]

14 A[5] BX holds “index” to

12 array element

16 -99

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 21)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-21-2048.jpg)

![Base + Index (Based Indexed)

[ Base + Index ] or [ Base ] [ Index ]

Sum of specified Base Register Pentium: EAX, EBX, ECX, EDX,

and Index Register gives offset ESP, EBP, EDI, ESI

MOV CX, [BX + DI] 8086: Base Reg = BX, BP

MOV [EAX + EBX] , ECX Index Reg = DI, SI

MOV CH, [BP] [SI]

Can be used to access array

MOV [BX] [SI] , SP

elements, e.g. Base Register =

MOV CL, [EDX] [ EDI] start of array, Index Register =

MOV [EAX] [EBX] , ECX position of element.

MOV [BP + DI] , CX

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 22)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-22-2048.jpg)

![Example: MOV AX, [BX+DI]

AX

-27

Data Segment

0

BX +12 2 ...

12

Start of Array

12 A[0]

DI +6 14 A[1]

6 16 A[2]

DI is index to 18 -27

array element

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 23)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-23-2048.jpg)

![Base + Index + Displacement (Based Relative Index)

[ Base + Index + Displacement]

Sum of specified Base Register Pentium: EAX, EBX, ECX, EDX,

and Index Register and EBP, EDI, ESI

Displacement gives offset

8086: Base Reg= BX, BP

Alt Syntax: Index Reg = DI, SI

Disp1 [Base] [Index+Disp2]

Displacement = Disp1+Disp2

Also known as Relative Based

MOV AX, [BP+DI+10] Index

MOV DH, [BX][DI-6] Can be used to access local

MOV AX, List [BX][DI] (stack) arrays, arrays of

MOV List [BP][DI–64], DX records, 2D arrays.

MOV EAX, List [EBX][ECX+2]

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 24)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-24-2048.jpg)

![Example: MOV AX, [BP+DI+10]

Stack Segment AX

0

BP +12 +67

...

12

12

+10

+10

Instruction 22 A[0] BP+10 points to start

+6 24 A[1] of array on stack

26 A[2]

6 28 +67 DI holds “position” of

array element

DI

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 25)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-25-2048.jpg)

![(Scale*Index) + Displacement (Scaled Index)

[ Scale * Index + Displacement]

Product of Index Register and a Only Pentium

constant scaling factor (2, 4 or

8) added to specified Supports efficient access to

Displacement to give offset. array elements when the element

size is 2, 4 or 8 bytes, e.g.

MOV EAX, [4 * ECX + 4] Displacement = offset to

MOV List [2 * EBX], CX beginning of array.

MOV List [2 * EBX+32], DX Index Register = position of

MOV AX, [2 * EDI+Age] desired element,

Scale = element size in bytes

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 26)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-26-2048.jpg)

![Example: MOV AX, ES:[2*ECX+4]

AX

Extra Segment

-99

+4 0

2

Instruction

4 A[0]

+4 6 A[1]

8 A[2]

+(2*6) 10 +4 points to start of

A[3] a Array

ECX 12 A[4]

14 A[5] ECX holds position of

6 array element

16 -99

Elements = 2 bytes

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 27)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-27-2048.jpg)

![Base + (Scale * Index) + Displacement

[ Base + Scale * Index + Displacement]

Product of Index Register and a Known as Based Scaled Index

constant scaling factor (2, 4 or

8) added to specified Base Only Pentium

Register and Displacement to

give offset.

Supports efficient access to

MOV EAX, [EBX][4*ECX] local arrays on the stack when

the element size is 2, 4 or 8

MOV [EAX][2*EBX] , CX

bytes.

MOV AX, [EBP][2*EDI+Age]

MOV List[EAX][2*EBX+32], DX

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 28)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-28-2048.jpg)

![Example: MOV EAX, [EBX+4*EDX+10]

Data Segment EAX

0

EBX +12 12349908H

...

12

12 EBX points to start

+10 of record

+10

EBX+10 points to

Instruction 22 A[0] start of array within

+(4*2) 24 A[0] record

26 A[1] EDX holds “position”

2 28 A[1] of array element.

EDX 30 9908H Elements = 4 bytes

32 1234H

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 29)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-29-2048.jpg)

![Think about

1. Why zero, single and two operand instructions occur in the

8086 instruction set.

2. The difference between a directive and an assembly

language statement

3. The difference between all of the addressing modes

4. How high level language statements like a = b[5]+c are

translated to assembly language and what addressing modes

are used

5. The machine organisation required to handle the addressing

modes

Computer Architecture (P. Leong) Pentium Arch. - Operands & Addressing Modes (page 30)](https://image.slidesharecdn.com/05operand-110602105517-phpapp01/75/05operand-30-2048.jpg)