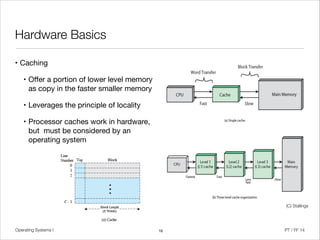

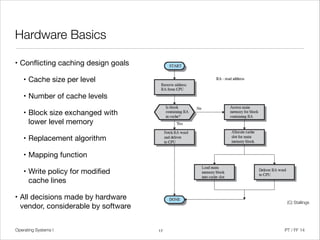

The document discusses the basics of hardware and operating systems, including various classes of operating systems such as embedded and real-time systems. It covers key concepts like processes, memory management, I/O operations, and multiprocessor architectures, emphasizing the importance of efficiency and the organization of memory in a hierarchy. Additionally, it outlines the role of interrupts and the challenges modern operating systems face with evolving hardware technology.