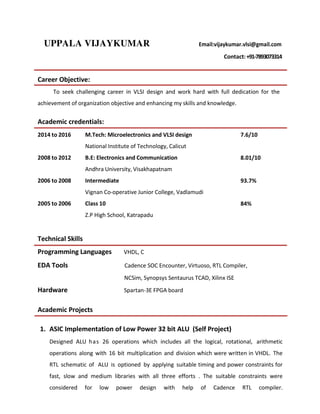

Uppala Vijaykumar Resume

- 1. UPPALA VIJAYKUMAR Email:vijaykumar.vlsi@gmail.com Contact:+91-7893073314 Career Objective: To seek challenging career in VLSI design and work hard with full dedication for the achievement of organization objective and enhancing my skills and knowledge. Academic credentials: 2014 to 2016 M.Tech: Microelectronics and VLSI design National Institute of Technology, Calicut 2008 to 2012 B.E: Electronics and Communication Andhra University, Visakhapatnam 2006 to 2008 Intermediate Vignan Co-operative Junior College, Vadlamudi 2005 to 2006 Class 10 Z.P High School, Katrapadu 7.6/10 8.01/10 93.7% 84% Technical Skills Programming Languages VHDL, C EDA Tools Cadence SOC Encounter, Virtuoso, RTL Compiler, NCSim, Synopsys Sentaurus TCAD, Xilinx ISE Hardware Spartan-3E FPGA board Academic Projects 1. ASIC Implementation of Low Power 32 bit ALU (Self Project) Designed ALU has 26 operations which includes all the logical, rotational, arithmetic operations along with 16 bit multiplication and division which were written in VHDL. The RTL schematic of ALU is optioned by applying suitable timing and power constraints for fast, slow and medium libraries with all three efforts . The suitable constraints were considered for low power design with help of Cadence RTL compiler.

- 2. The ASIC design was implemented using 180 nm technology, and completed full RTL – GDSII flow and power analysis, STA, and verified area, DRC, Antenna, Connectivity with 0 violations. The VHDL design is tested on Spartan-3E FPGA kit with UART communication. HDL Language: VHDL EDA Tools: Cadence RTL Compiler, SOC Encounter, Xilinx ISE Hardware: Spartan-3E FPGA kit 2. Implementation of Low On-resistance 4H-SiC Power VD-MOSFET by Device Optimization (Main Project) Implementation of 4H-SiC power vertical double implanted MOSFET with structural modifications to reduce the specific on-resistance without compromising on breakdown voltage and cell size. Optimized 4H-SiC power VD-MOSFET structure offers a specific on- resistance of 2.457 mΩ-cm2 and breakdown voltage of 1.2 kV, with peak electric field around 4 MV/cm at breakdown. Optimized 4H-SiC power MOSFET has a figure of merit of 586 MW/cm2 EDA Tools: Synopsys Sentaurus TCAD 3. ASIC Implementation of High speed Multiplier (2n x 2n ) (n=7) on Cadence SOC Encounter and also tested 8 x 8 Multiplication based on Karatsuba Algorithm (Mini Project) HDL Language: VHDL EDA Tools: NCSIM, Cadence RTL Compiler and SOC Encounter Hardware: Spartan-3E kit 4. VHDL implementation of Band Pass Filter (14 Tap) and also tested on Spartan-3E FPGA kit (Course Project) HDL Language: VHDL Hardware: Spartan-3E kit 5. ASIC implementation of vending machine on Cadence SOC Encounter (Mini Project) HDL Language: VHDL EDA Tools: NCSIM, Cadence RTL Compiler and SOC Encounter Hardware: Spartan-3E kit 6. Low power design of Dual Edge Triggered Flip Flop on Cadence virtuoso (Course Project) EDA Tools: Cadence Virtuoso Date: Place: (UPPALA VIJAYKUMAR)