session two hardware description language

•Download as PPTX, PDF•

0 likes•2 views

A hardware description language enables a precise, formal description of an electronic circuit that allows for the automated analysis and simulation of an electronic circuit. It also allows for the synthesis of an HDL description into a netlist (a specification of physical electronic components and how they are connected together), which can then be placed and routed to produce the set of masks used to create an integrated circuit.

Report

Share

Report

Share

Recommended

Welcome to the April edition of WIPAC Monthly, the magazine brought to you by Water Industry Process Automation & Control.

In this month's edition, along with the latest news from the industry we have articles on:

The use of artificial intelligence and self-service platforms to improve water sustainability

A feature article on measuring wastewater spills

An article on the National Underground Asset Register

Have a good month,

OliverWater Industry Process Automation & Control Monthly - April 2024

Water Industry Process Automation & Control Monthly - April 2024Water Industry Process Automation & Control

More Related Content

Similar to session two hardware description language

Similar to session two hardware description language (20)

hardware description language power point presentation

hardware description language power point presentation

Recently uploaded

Welcome to the April edition of WIPAC Monthly, the magazine brought to you by Water Industry Process Automation & Control.

In this month's edition, along with the latest news from the industry we have articles on:

The use of artificial intelligence and self-service platforms to improve water sustainability

A feature article on measuring wastewater spills

An article on the National Underground Asset Register

Have a good month,

OliverWater Industry Process Automation & Control Monthly - April 2024

Water Industry Process Automation & Control Monthly - April 2024Water Industry Process Automation & Control

Call Girl Bhosari Indira Call Now: 8617697112 Bhosari Escorts Booking Contact Details WhatsApp Chat: +91-8617697112 Bhosari Escort Service includes providing maximum physical satisfaction to their clients as well as engaging conversation that keeps your time enjoyable and entertaining. Plus they look fabulously elegant; making an impressionable. Independent Escorts Bhosari understands the value of confidentiality and discretion - they will go the extra mile to meet your needs. Simply contact them via text messaging or through their online profiles; they'd be more than delighted to accommodate any request or arrange a romantic date or fun-filled night together. We provide –(INDIRA) Call Girl Bhosari Call Now 8617697112 Bhosari Escorts 24x7

(INDIRA) Call Girl Bhosari Call Now 8617697112 Bhosari Escorts 24x7Call Girls in Nagpur High Profile Call Girls

Call girls in delhi ✔️✔️🔝 9953056974 🔝✔️✔️Welcome To Vip Escort Services In Delhi [ ]Noida Gurgaon 24/7 Open Sex Escort Services With Happy Ending ServiCe Done By Most Attractive Charming Soft Spoken Bold Beautiful Full Cooperative Independent Escort Girls ServiCe In All-Star Hotel And Home Service In All Over Delhi, Noida, Gurgaon, Faridabad, Ghaziabad, Greater Noida,

• IN CALL AND OUT CALL SERVICE IN DELHI NCR

• 3* 5* 7* HOTELS SERVICE IN DELHI NCR

• 24 HOURS AVAILABLE IN DELHI NCR

• INDIAN, RUSSIAN, PUNJABI, KASHMIRI ESCORTS

• REAL MODELS, COLLEGE GIRLS, HOUSE WIFE, ALSO AVAILABLE

• SHORT TIME AND FULL TIME SERVICE AVAILABLE

• HYGIENIC FULL AC NEAT AND CLEAN ROOMS AVAIL. IN HOTEL 24 HOURS

• DAILY NEW ESCORTS STAFF AVAILABLE

• MINIMUM TO MAXIMUM RANGE AVAILABLE.

Call Girls in Delhi & Independent Escort Service –

CALL GIRLS SERVICE DELHI NCR

Vip call girls in Delhi

Call Girls in Delhi, Call Girl Service 24×7 open

Call Girls in Delhi Best Delhi Escorts in Delhi

Low Rate Call Girls In Saket Delhi

X~CALL GIRLS IN Ramesh Nagar Metro

best Delhi call girls and Delhi escort service.

CALL GIRLS SERVICE IN ALL DELHI …

(Delhi) Call Girls in (Chanakyapuri)

Hot And Sexy Independent Model Escort Service In Delhi Unlimited Enjoy Genuine 100% Profiles And Trusted Door Step Call Girls Feel Free To Call Us Female Service Hot Busty & Sexy Party Girls Available For Complete Enjoyment. We Guarantee Full Satisfaction & In Case Of Any Unhappy Experience, We Would Refund Your Fees, Without Any Questions Asked. Feel Free To Call Us Female Service Provider Hours Opens Thanks.

Delhi Escorts Services 100% secure Services.Incall_OutCall Available and outcall Services provide.

We are available 24*7 for Full Night and short Time Escort Services all over Delhi NCR.

Delhi All Hotel Services available 3* 4* 5* Call Call

Delhi Escorts Services And Delhi Call Girl Agency 100% secure Services in my agency. Incall and outcall Services provide.

We are available 24*7 for Full Night and short Time Escort Services my agency in all over New Delhi

Delhi All Hotel Services available my agency

SERVICES [✓✓✓]

Housewife

College Girl

VIP Escort

Independent Girl

Aunty

Without a Condom sucking )?

Sexy Aunty.DSL (Dick Sucking Lips)?

DT (Dining at the Toes English Spanking)

Doggie (Sex style from no behind)??

OutCall- All Over Delhi Noida Gurgaon 24/7

FOR APPOINTMENT Call/Whatsop / 9953056974Call Girls in Ramesh Nagar Delhi 💯 Call Us 🔝9953056974 🔝 Escort Service

Call Girls in Ramesh Nagar Delhi 💯 Call Us 🔝9953056974 🔝 Escort Service9953056974 Low Rate Call Girls In Saket, Delhi NCR

Model Call Girl Services in Delhi reach out to us at 🔝 9953056974 🔝✔️✔️

Our agency presents a selection of young, charming call girls available for bookings at Oyo Hotels. Experience high-class escort services at pocket-friendly rates, with our female escorts exuding both beauty and a delightful personality, ready to meet your desires. Whether it's Housewives, College girls, Russian girls, Muslim girls, or any other preference, we offer a diverse range of options to cater to your tastes.

We provide both in-call and out-call services for your convenience. Our in-call location in Delhi ensures cleanliness, hygiene, and 100% safety, while our out-call services offer doorstep delivery for added ease.

We value your time and money, hence we kindly request pic collectors, time-passers, and bargain hunters to refrain from contacting us.

Our services feature various packages at competitive rates:

One shot: ₹2000/in-call, ₹5000/out-call

Two shots with one girl: ₹3500/in-call, ₹6000/out-call

Body to body massage with sex: ₹3000/in-call

Full night for one person: ₹7000/in-call, ₹10000/out-call

Full night for more than 1 person: Contact us at 🔝 9953056974 🔝. for details

Operating 24/7, we serve various locations in Delhi, including Green Park, Lajpat Nagar, Saket, and Hauz Khas near metro stations.

For premium call girl services in Delhi 🔝 9953056974 🔝. Thank you for considering us!Call Now ≽ 9953056974 ≼🔝 Call Girls In New Ashok Nagar ≼🔝 Delhi door step de...

Call Now ≽ 9953056974 ≼🔝 Call Girls In New Ashok Nagar ≼🔝 Delhi door step de...9953056974 Low Rate Call Girls In Saket, Delhi NCR

Recently uploaded (20)

Water Industry Process Automation & Control Monthly - April 2024

Water Industry Process Automation & Control Monthly - April 2024

DC MACHINE-Motoring and generation, Armature circuit equation

DC MACHINE-Motoring and generation, Armature circuit equation

Top Rated Call Girls In chittoor 📱 {7001035870} VIP Escorts chittoor

Top Rated Call Girls In chittoor 📱 {7001035870} VIP Escorts chittoor

(INDIRA) Call Girl Bhosari Call Now 8617697112 Bhosari Escorts 24x7

(INDIRA) Call Girl Bhosari Call Now 8617697112 Bhosari Escorts 24x7

XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX

XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX

Call Girls in Ramesh Nagar Delhi 💯 Call Us 🔝9953056974 🔝 Escort Service

Call Girls in Ramesh Nagar Delhi 💯 Call Us 🔝9953056974 🔝 Escort Service

Bhosari ( Call Girls ) Pune 6297143586 Hot Model With Sexy Bhabi Ready For ...

Bhosari ( Call Girls ) Pune 6297143586 Hot Model With Sexy Bhabi Ready For ...

VIP Model Call Girls Kothrud ( Pune ) Call ON 8005736733 Starting From 5K to ...

VIP Model Call Girls Kothrud ( Pune ) Call ON 8005736733 Starting From 5K to ...

VIP Call Girls Palanpur 7001035870 Whatsapp Number, 24/07 Booking

VIP Call Girls Palanpur 7001035870 Whatsapp Number, 24/07 Booking

Call Now ≽ 9953056974 ≼🔝 Call Girls In New Ashok Nagar ≼🔝 Delhi door step de...

Call Now ≽ 9953056974 ≼🔝 Call Girls In New Ashok Nagar ≼🔝 Delhi door step de...

Call Girls Pimpri Chinchwad Call Me 7737669865 Budget Friendly No Advance Boo...

Call Girls Pimpri Chinchwad Call Me 7737669865 Budget Friendly No Advance Boo...

session two hardware description language

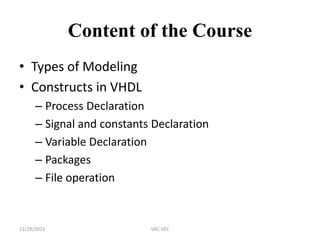

- 1. Content of the Course • Types of Modeling • Constructs in VHDL – Process Declaration – Signal and constants Declaration – Variable Declaration – Packages – File operation 12/29/2023 VAC VEC

- 2. Design Hierarchy Levels ( Modeling Styles 12/29/2023 VAC VEC • Structural – Define explicit components and the connections between them. • Dataflow – Most are like assigning expressions to signals • Behavioral – Write an algorithm that describes the circuit’s output

- 3. Dataflow Level • Dataflow description – The detail is less with data dependencies described, not the components and connections – Includes “when” and “select” (case) statements 12/29/2023 VAC VEC

- 4. Full Adder - Data flow 12/29/2023 VAC VEC

- 5. • A structural description is like the schematic, describing the components and their interconnections precisely – Includes concurrent statements • A component statement is a concurrent statement 12/29/2023 VAC VEC Structural Level

- 6. 4-bit Ripple-Carry Adder - Structural Description 12/29/2023 VAC VEC

- 7. 12/29/2023 VAC VEC 4-bit Ripple-Carry Adder - Structural Description cntd.

- 8. 8 Constructs in VHDL • A process statement is a concurrent statement, but all statements contained in it are sequential statement (statements that executes serially, one after the other). • The use of processes makes your code more modular, more readable, and allows you to separate combinational logic from sequential logic.

- 9. 9 The sensitivity list • List of all signals that the process is sensitive to. Sensitive means that a change in the value of these signals will cause the process to be invoked.

- 10. 10 Incomplete sensitivity list effect a b z (VHDL) z (gate level)

- 11. 11 VHDL Object Types • Constants • Signals • Variables • Files

- 12. 12 Signals • It is a physical signal (you can think of it like a piece of wire) • A signal is a sequence of time-value pairs • A signal assignment takes effect only after a certain delay (the smallest possible delay is called a “delta time”). • It is possible to define global signals (signals that can be shared among entities) • But more often signals are just locally defined for a given architecture

- 13. 13 Variables • Assignment to variables are scheduled immediately (the assignment takes effect immediately) • If a variable is assigned a value, the corresponding location in memory is written with the new value while destroying the old value. – This effectively happen immediately so if the next executing statement in the program uses the value of the variable, it is the new value that is used. • Typically, variables are used as a local storage mechanism, visible only inside a process

- 14. 14 Signals vs. Variables • Signals assignments are scheduled after a certain delay d • Variables assignments happen immediately, there is no delay

- 15. 15 Packages • Packages offers a mechanism to globally define and share values, types, components, functions and procedures that are commonly used. • package declaration and package body

- 16. 16 Subprograms • Procedures can return more than one value (they can have both input and output parameters) • Functions return always just one value (can have only input parameters) Example: conversion functions, resolution functions, …

- 17. 17 Attributes • Info attached to VHDL objects • Some predefined attributes: ‘left the leftmost value of a type ‘right ‘high the greatest value of a type ‘low ‘length the number of elements in an array ‘event a change on a signal or variable ‘range the range of the elements of an array object

- 18. 18 Component (socket mechanism) • Declare the name and interface of a “sub-unit”, to be used in the current level of design hierarchy. component adder port ( in_a, in_b: in std_logic_vector; z : std_logic_vector; carry: std_logic); end component; adder instance #1 adder instance #2

- 19. 19 ASSERT statement • The ASSERT checks a boolean expression and if the value is true does nothing, else will output a text string to std output. It can have different severity levels: NOTE, WARNING, ERROR, FAILURE ASSERT false REPORT “End of TestBench” SEVERITY ERROR;

- 20. 20 COMPLEX TYPES: • enumerated types TYPE color is (red, blue, yellow, green) • ARRAY TYPE dbus is ARRAY (31 downto 0) of std_logic

- 21. 21 COMPLEX TYPES: • RECORD TYPE instruction is RECORD opcode: integer; src: integer; dest: integer; END RECORD

- 22. 22 COMPLEX TYPES: • FILE TYPE ram_data_file_t IS FILE OF INTEGER; FILE ram_data_file : ram_data_file_t IS IN “/claudio/vhdl/tb/ram.txt”

- 23. 23 More on FILEs • use std.textio.all; • READ, WRITE, READLINE, WRITELINE, ENDFILE, … • VHDL supports overloading