Op ampdesignfinalproject

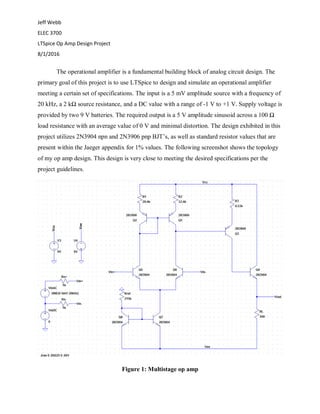

- 1. Jeff Webb ELEC 3700 LTSpice Op Amp Design Project 8/1/2016 The operational amplifier is a fundamental building block of analog circuit design. The primary goal of this project is to use LTSpice to design and simulate an operational amplifier meeting a certain set of specifications. The input is a 5 mV amplitude source with a frequency of 20 kHz, a 2 kΩ source resistance, and a DC value with a range of -1 V to +1 V. Supply voltage is provided by two 9 V batteries. The required output is a 5 V amplitude sinusoid across a 100 Ω load resistance with an average value of 0 V and minimal distortion. The design exhibited in this project utilizes 2N3904 npn and 2N3906 pnp BJT’s, as well as standard resistor values that are present within the Jaeger appendix for 1% values. The following screenshot shows the topology of my op amp design. This design is very close to meeting the desired specifications per the project guidelines. Figure 1: Multistage op amp

- 2. The first functional block that will be discussed is the differential input stage given in the figure below. Figure 2: Differential input stage with current mirror load The differential input stage forms the backbone of the op amp circuit. This stage is a bipolar differential amplifier with two npn transistors and an active current mirror load formed from a pnp current mirror as shown. The current mirror is used to enhance the voltage gain capability while helping to maintain the operating point balance that is necessary for good common-mode rejection. The current mirror circuit given below is formed by two npn transistors and a Rref resistor. Figure 3: Current mirror circuit

- 3. Current mirror biasing is extremely important in this design. A reference current is established by using resistor Rref that provides operating bias to the current mirror. A large value of resistance is required to achieve a small operating current that is independent of the supply voltage. Lastly, the last two stages of the op amp shown below are discussed. Figure 4: pnp common-emitter stage and npn output stage An op amp usually requires higher voltage gain than is available from a single differential amplifier stage. To achieve a higher gain, a pnp common-emitter amplifier Q3 is added by connecting it to the output of the differential amplifier. The resistor R3 is added at the collector of the pnp to help obtain a better output signal centered at 0 V. The output stage Q4 is added to maintain unity voltage gain and provide low output resistance. The input resistance is set by the input differential pair, and the output resistance is determined by the resistance looking into the emitter of Q4.

- 4. I measured the differential and common mode gain of my op amp using LTSpice. For the differential mode gain, I wired a voltage source to the two inputs of the op amp and specified a voltage of 1 V AC. Next, I ran an AC analysis simulation to obtain the Bode plot shown below. Figure 5: Circuit schematic and Bode plot corresponding to differential mode response In order to measure the common mode gain, I shorted the two input terminals of my op amp and wired it to the positive terminal of a 1 V AC voltage source. Next, I ran an AC analysis simulation to obtain the common mode response shown below. Figure 6: Circuit schematic and Bode plot corresponding to common mode response

- 5. I also measured total quiescent power dissipation and DC operating points for -1, 0, and +1 V in LTSpice. These values are easily found by running the op amp, hovering the cursor over the output and reading the values at the bottom of the screen. Given below is a table summarizing all of the aforementioned and required quantities for my op amp: DC input Differential Mode Gain Common Mode Gain CMRR Dissipated Power DC Output -1 V 2511 v/v .05 v/v 94 dB 982.4 mW 911.4 mV 0 V 2511 v/v .05 v/v 94 dB 993.3 mW 966.5 mV +1 V 2511 v/v .05 v/v 94 dB 982.4 mW 911.4 mV The following screenshots show plots of the output of my op amp at DC values of 0, -1, and +1 V. Figure 7: Output at 0 V DC

- 6. Figure 8: Output at -1 V DC Figure 9: Output at +1 V DC Figure 10: Average value of output waveform

- 7. The results in each plot give an output waveform with an amplitude of about 5.1 V with minimum distortion and an average value of 480.89 mV. This is as close as I could get to the required output amplitude of 5 V with 0 V average value. I think this is a good op amp and I am pleased with this design. It provides good overall characteristics: desired gain, CMRR and good frequency response. Overall, this project has taught me a great deal about the behavior and characteristics of multistage amplifiers. I am confident that the knowledge and experience I have gained from this project will stimulate my future endeavors next semester in radio lab.