More Related Content

Similar to W ee network_theory_10-06-17_ls2-sol (18)

W ee network_theory_10-06-17_ls2-sol

- 1. Serial : W_EE_NetworkTheory_100617_LS2

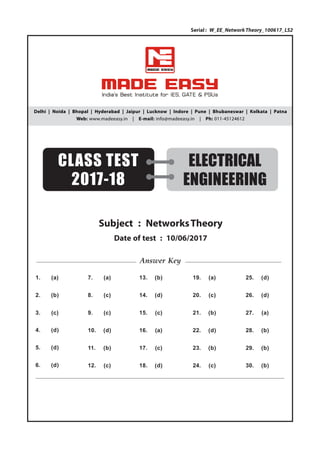

Subject : NetworksTheory

Date of test : 10/06/2017

1. (a)

2. (b)

3. (c)

4. (d)

5. (d)

6. (d)

7. (a)

8. (c)

9. (c)

10. (d)

11. (b)

12. (c)

13. (b)

14. (d)

15. (c)

16. (a)

17. (c)

18. (d)

19. (a)

20. (c)

21. (b)

22. (d)

23. (b)

24. (c)

25. (d)

26. (d)

27. (a)

28. (b)

29. (b)

30. (b)

Answer Key

Delhi | Noida | Bhopal | Hyderabad | Jaipur | Lucknow | Indore | Pune | Bhubaneswar | Kolkata | Patna

Web: www.madeeasy.in | E-mail: info@madeeasy.in | Ph: 011-45124612

CLASS TEST

2017-18

ELECTRICAL

ENGINEERING

- 2. © Copyright:www.madeeasy.in

8 Electrical Engineering

DetailedExplanations

1.1.1.1.1. (a)(a)(a)(a)(a)

At zero frequency, the capacitors are open circuited.

∴ Z(0) = R1 + R2 = 3 Ω

At ∞ frequency the capacitors are short-circuited.

∴ Z(∞) = R1 = 2 Ω

This gives R2 = 3 – 2 = 1 Ω

Hence, R1 = 2 Ω and R2 = 1 Ω

2.2.2.2.2. (b)(b)(b)(b)(b)

+

–

+ +– –

+

–

VR

I VC

VL

V

VR

VC

V

For a quick analysis, RV in phase with IR leads CV by 90° and hence capacitive. A series resonant circuit

is capacitive below resonant frequency. So (b) is correct.

Mathematical AnalysisMathematical AnalysisMathematical AnalysisMathematical AnalysisMathematical Analysis

RV = R j L

j C

+ ω +

ω

I

I I

RV = RI

CV =

j Cω

I

or R

C

V

V

= jω RC

which means that RV leads CV by 90° as shown in figure (b).

and RV

V

=

R

j

R j L

C

+ ω −

ω

=

( )2

1

RC

RC j LC

ω

ω + ω −

or, RV

V

=

( )

2

1

22 2 2 2

1

tan

1

RC LC

RC

R C LC

−

ω − ω

∠ ω

ω + ω −

From the above equation RV will lead V when

1 – ω2 LC > 0 or, ω2 LC < 1 or,

1

LC

ω < = ω0, the resonance frequency.

Hence, choice (b) is correct.

3.3.3.3.3. (c)(c)(c)(c)(c)

From maximum power transfer theorem;

P = I2 × RL

or P =

2

2

( )

Th

L

Th L

V

R

R R

×

+

...(i)

- 3. © Copyright:www.madeeasy.in

9CTEE17 • NetworksTheory

Hence Pmax at RL = RTh

Pmax =

2

4

Th

Th

V

R

From equation (i), we see first as RL increases the power delivered to the load (P) is increased upto a

maximum value Pmax then P starts declining for further increament in RL.

4.4.4.4.4. (d)(d)(d)(d)(d)

At t = 0 voltage on capacitor = 3 × 1 = 3 V

R = 2 Ω, C = 1F

∴ RC = 2, τ =

1

2

sec; v( ∞) = 0

Now, Vc(t) = Vc(∞) – [Vc(∞) – Vc(0)] × e–t/τ

v(t) = 0 – (0 – 3)e–t/2 = 3 e–t/2

When the switch S is closed after t > 0, the circuit becomes source free and the capacitor will only

discharge.

5.5.5.5.5. (d)(d)(d)(d)(d)

Infinite network having equivalent resistance RAB. If we reduce one step the effective resistance will not

change, so replace remaining network with Req ( = RAB).

R

R⇒

A

B

R R R R

R R R R → ∞

Req

RAB = Req

R

ReqRRAB = Req ⇒

A

B

Req = eq

eq

R R

R

R R

×

+

+

Req – R =

eq

eqR

R R

R

×

+

Req

2 – R2 = R Req

Req

2 – R Req – R2 = 0

we get, Req =

2 2

4

2 1

R R R+ ± +

×

Therefore, the possible value of Req =

( 5 1)

2

R+

= 1.62 × 2 = 3.24 Ω

- 4. © Copyright:www.madeeasy.in

10 Electrical Engineering

6.6.6.6.6. (d)(d)(d)(d)(d)

At resonance the current Is will flow through resistor.

Vs = 10 cos ω0 t × 1 = 10 cos ω0 t V

Vs =

d

L

dt

i

LR CIs

+

–

Vs

i

10 cos ω0 t =

d

L

dt

i

d

dt

i

=

10

L

cos ω0 t

d∫ i = 0

10

cos .t dt

L

ω∫

i(t) =

0

10

Lω

sin ω0 t A

7.7.7.7.7. (a)(a)(a)(a)(a)

8.8.8.8.8. (c)(c)(c)(c)(c)

V1 = nV2 ; since 1

2 1

V n

V

=

and I1 =

1

2

2

1 1

;since

n n

=

I

I

I

∴

A B

C D

=

0

0 1/

n

n

9.9.9.9.9. (c)(c)(c)(c)(c)

Here, current through 12 Ω resistor will be zero.

+

–

5 Ω

5 Ω

a

i1

20 V

Loop - 1

+ –

b

5 Ω5 Ω

20 V

Loop - 2

i2

In loop (1) and loop (2),

i1 =

20

10

= 2 A, i2 =

20

10

= 2 A

Va = 5 × 2 = 10 V, Vb = 5 × 2 = 10 V

– + + – + –

10 V 5 V 10 V

a b

Voltage between a and b points

= + 10 + 5 – 10 = 5 V

- 5. © Copyright:www.madeeasy.in

11CTEE17 • NetworksTheory

10.10.10.10.10. (d)(d)(d)(d)(d)

Current is lagging by 30°

θ =

1

tan 30LX

R

−

= °

tan 30° = LX

R

⇒

1

3

=

1

R

⇒ R = 3 1.732= Ω

11.11.11.11.11. (b)(b)(b)(b)(b)

For power transferred to load to be maximum. RL should be equal to RTh.

Voc:

+

–

v04 Ω

+

–

+

– 2 0i

5 Ω

6 Ω

+ –

4 V

2 Ω

v0

i0

Voc

+

–

v0 = 0 as current through 6 Ω resistor is zero

Applying KVL

4 Ω

+

–

+

– 2i0

5 Ω2 Ω

i0

Voc

+

–

4 V

2i0 + 4i0 – 2i0 + 5i0 = 4

i0 =

4

9

A

Voc =

4 4

5 2

9 9

− × + × =

12

Volt

9

−

iscscscscsc ;

+

–

v0

4 Ω

+

–

+

– 2 0i

5 Ω

6 Ω

+ –

2 Ω

v0

i0

v0

isc

Short circuited

4 V

Applying nodal analysis

0 0 0 0 00 2 4

6 5 6

v v v v− − + −

+ +

i

= 0 ...(i)

i0 =

2

3

...(ii)

- 6. © Copyright:www.madeeasy.in

12 Electrical Engineering

Substituting this value of I0 equation (i)

v0 =

12

Volts

11

−

isc = 0 12 2

A

6 11 6 11

v − −

= =

×

RTh =

12 11

9 2

oc

sc

V − ×

=

× −i = 7.33 Ω

12.12.12.12.12. (c)(c)(c)(c)(c)

We open circuit the load resistance to obtain VTh,

+

–

2 A

4 V

+ –

V0

1 Ω

1 Ω 2 Ω

4V0

X

Y

Open circuit

VTh

+

–

+ –

I

– +

Hence when the load is removed, current from the 2 A source flows in the closed path.

So, voltage V0 = 2 × 2 = 4 V

KVL in the loop:

–VTh + 4 + (2 × 1) + 4 + (4V0) = 0

or, VTh = 26 V

RTh can be obtained by short circuiting all voltage sources (except dependent source) and open circuiting

current source. Take 1V voltage source across load and Imagine ‘I’ current is flowing from source.

Here, 01 5

1

V−

= I

Since V0 = 2I , therefore

1 5(2 )

1

− I

= I

+

–

+ –

V0

1 Ω

1 Ω 2 Ω

4V0

I

Y

1 V

+

–

or, I =

1

11

A

∴ RTh =

( )

1 1

11

1/ 11

= = Ω

I

13.13.13.13.13. (b)(b)(b)(b)(b)

+

–

I3

I1

I2+ +

V2 6 Ω

3 Ω

3 Ω

141 V

I II

N

III

–

V1

–

- 7. © Copyright:www.madeeasy.in

13CTEE17 • NetworksTheory

1

2

V

V

=

1 1 1 2

2 2 1 2

22 1

41 4

V

V

= +

⇒ = +

I I I

I I I

Applying KVL

Loop I

3(I1 + I3) + V1 = 141

3I1 + 3I3 + 2I1 + I2 = 141

5I1 + I2 + 3I3 = 141 ...(i)

Loop II

V2 = (I3 – I2) ⋅ 6

V2 = I1 + 4I2

I1 + 4I2 = 6I3 – 6I2

I1 + 10I2 – 6I3 = 0 ...(ii)

Loop III

3(I1 + I3) + 3I3+ 6(I3 – I2) = 141

3I1 – 6I2 + 12I3 = 141 ...(iii)

By equation (i), (ii) and (iii)

I1 = 24 A I2 = 1.5 A I3 = 6.5 A

14.14.14.14.14. (d)(d)(d)(d)(d) +

–

AV

4 Ω 5 Ω

B

j 8.66 Ω– 4j Ω

X

VAB = VAX – VBX

VAX =

4

4 4

j

V

j

−

×

−

VAX = V × 0.707∠–45°

VBX = 8.66

0.866 30

5 8.66

j

V V

j

× = × ∠ ° +

VAB = ( )0.707 45 (0.866 30 [ ]AX BXV V V − = ∠ − ° − ∠ °

VAB = V × 0.9658∠–105°

Given VAB = 48.3∠30° volts

∴ V =

48.3 30

0.9658 105

∠ °

∠ − °

V = 50∠135° volts

15.15.15.15.15. (c)(c)(c)(c)(c)

Drawing equivalent in s-domain

sL1 sL2

+

–

V2

+

–

V1

R I2I1

+

–

+

–

1/Cs

sM 2I sM 1I

Applying KVL

in loop I

V1 = 1 1 2

1

sL sM

sC

+ +

I I

- 8. © Copyright:www.madeeasy.in

14 Electrical Engineering

in loop II

V2 = sMI1 + (R + sL2)I2

comparing with standard equations

Z11 = 1

1

sL

sC

+ Z12 = sM

Z21 = sM Z22 = R + sL2

16.16.16.16.16. (a)(a)(a)(a)(a)

From the circuit diagram, we have:

I1 = 1

2

V

R+

20 V

R

4Ω

2Ω4Ω

+

–

Vx

–+ Vx

V1

+

–

I1

Power absorbs by RΩ resistor is,

PR = I1

2 R

=

2

1 5

2

V

R

R

× = +

(Given) ...(1)

The nodal equations can be written as,

1 120

4 4

V V V− −

+x

= 1

1

2

V

R

=

+

I ...(2)

and Vx = 1

1

2

2

2

V

R

=

+

I ...(3)

From equation (2) and (3), we can write

1 1

5

4 4 4

V V V

− + −x

= 1

2

V

R+

or,

( )

1 12 2

5

4 2 4

V V

R

− +

+ =

( )

1

2

V

R+

or,

( )1

1 1

2 2 2

V

R

+

+

= 5

or, V1 =

( )10 2

3

R

R

+

+

Now, from equation (1) we obtain;

( )2

100

3

R

R

+

= 5

or, R2 – 14R + 9 = 0

Solving for R yields; R = 13.325 Ω or 0.675 Ω

17.17.17.17.17. (c)(c)(c)(c)(c)

at t = 0–, the circuit will be

2 Ω

2 Ω

3 Ω3 Ω

+

–

C

20V

3 Ω

+

–

VC

I 2 Happlying KVL

2I + 3I – 20 = 0

I =

20

4 A

5

=

- 9. © Copyright:www.madeeasy.in

15CTEE17 • NetworksTheory

VC = 3 × 4 = 12 Volts

at t = 0+ the circuit will be 2 Ω

2 Ω

3 Ω3 Ω

+

–

12 V

20 V

3 Ω

2 H

Va

i

iL(0–) = iL(0+) = 0 A

⇒ Va =

3 12

2 3

×

+

= 7.2 V

Va = 3 2

d

dt

+

i

i

at t = 0, i = 0

7.2 = 3 0 2

d

dt

+

i

×

⇒

d

dt

i

= 3.6 A/s

18.18.18.18.18. (d)(d)(d)(d)(d)

h-parameters equations are:

V1 = h11 I1 + h12 V2

I2 = h21I1 + h22 V2

Here, h21 =

2

2

1 0V =

I

I

The circuit for V2 = 0 can be redrawn as shown below.

+

–

V1

I1

I2

R1

R2

αI1

( )αI I1 2+

( )I I1 2+

1

sC

KVL in the above loop gives,

( )

( )1 2

2 1 2R

sC

α +

+ +

I I

I I = 0

1 2

2 1 2 2R R

sC sC

α

+ + +

I I

I I = 0

1 2 2 2

1

R R

sC sC

α

+ +

I + I = 0

2 2

1

R

sC

+

I = 1 2R

sC

α

− +

I

h21 = 2 2

1 21

R Cs

R Cs

α +

= − +

I

I

19.19.19.19.19. (a)(a)(a)(a)(a)

B =

1 0 0 1 0 0

0 1 0 0 0 1

0 0 1 1 1 1

−

− −

Fundamental loop matrix is always written in the form

B = [I : BT]

Identity

Matrix

Loop matrix with

respect to given tree

Ql = –[BT]T

- 10. © Copyright:www.madeeasy.in

16 Electrical Engineering

and Q = [Ql : I]

QL =

1 0 0

0 0 1

1 1 1

T

− −

− −

=

1 0 1

0 0 1

0 1 1

− −

Q =

1 0 1 1 0 0

0 0 1 0 1 0

0 1 1 0 0 1

− −

20.20.20.20.20. (c)(c)(c)(c)(c)

Let us consider one L-C unit as shown below.

L

V1 V2

+

–

1

Cs

C

+

–

I1 I2

sL

I1 I2

Applying KVL in input loop,

⇒ –V1 + I1Ls + V2 = 0

V1 = V2 + Ls I1 ...(i)

Applying KVL in the output loop,

⇒ 1 2

2V

sC

−

− +

I I

= 0

–V2 Cs + I1 – I2 = 0

I1 = I2 + V2 Cs ...(ii)

Substituting equation (ii) in equation (i)

V1 = V2 + Ls(I2 + V2 Cs)

= V2 + LsI2 + V2 LCs2

or, V1 = V2 (1 + LCs2) + LsI2 ...(iii)

I1 = V2 Cs + I2 ...(iv)

When comparing above two equations with

V1 = AV2 + BI2

I1 = CV2 + DI2

A B

C D

=

( )2

1

1

LCs Ls

Cs

+

with n such units connected as shown in given problem, the transmission matrix is the product of each

unit.

∴ [T] =

2

1

1

n

s LC sL

sC

+

- 11. © Copyright:www.madeeasy.in

17CTEE17 • NetworksTheory

21.21.21.21.21. (b)(b)(b)(b)(b)

Redrawing the circuit

+

–

+

– 0.2 V s2( )

2 Ω

V1( )s 10I ( )s1

+

–

V2( )sZ

Z = 1 5 1. s =

1 5 1

1 5 1

. s

. s

×

+

=

1 5

1 5 1

. s

. s +

Applying KVL in loop I

V1(s) = 2I1(s) – 0.2 V2(s) ...(i)

V2(s) = 1

1.5

10 ( )×

1.5 +1

s

s

s

− I

V2(s) =

15 ( )

1.5 +1

1s s

s

− I

...(ii)

From equations (i) and (ii)

Input admittance = 1

1

( )

( )

s

V s

I

=

1 5 1

6 2

. s

s

+

+

22.22.22.22.22. (d)(d)(d)(d)(d)

L, B, P

A

1ba 2

1′ 2′

+

–20V

+

– 15V

RL

We can determine the norton’s equivalent across the terminals a and b.

TTTTTo detero detero detero detero determineminemineminemine INNNNN :::::

L, B, P

A

1ba 2

1′ 2′

+

–20V

+

– 15V

IN

We can use superposition theorem to determine IN.

When only 20V source is acting alone.When only 20V source is acting alone.When only 20V source is acting alone.When only 20V source is acting alone.When only 20V source is acting alone.

L, B, P

A

1ba 2

1′ 2′

+

–20V

IN

′

From figure A in the question, we can calculate N′I .

N′I = 8 A

When only 15 V source is acting alone:

- 12. © Copyright:www.madeeasy.in

18 Electrical Engineering

L, B, P

A

1ba 2

1′ 2′

+

– 15V

IN

′′

By applying the Reciprocity principle to the figure. A in the given question, we can calculate N′′I .

N′′I =

2

15 3A

10

− × = −

15 10

2N

= ′′ I

Thus, IN = 8 3 5AN N+ = − =′ ′′I I (Using superposition theorem)

TTTTTo detero detero detero detero determineminemineminemine RRRRRNNNNN :::::

L, B, P

A

1ba 2

1′ 2′

RN

Equivalently, we can write the above circuit as show below.

L, B, P

A

1 2

1′ 2′

RN

From figure A in the given question, we can calculate RN as

RN =

10V

2.5

4A

= Ω

So, the Norton’s equivalent across the terminals a and b is will be as shown below.

RN = 2.5ΩIN = 5A

IL

RL

a

b

Maximum power will be delivered to RL, when RL will be equal to RN = 2.5Ω

When RL = RN = 2.5 Ω,

5

2.5 A

2L = =I

Hence, Pmax = IL

2RL = IL

2RN = (2.5)2 × 2.5 = 15.625 W

- 13. © Copyright:www.madeeasy.in

19CTEE17 • NetworksTheory

23.23.23.23.23. (b)(b)(b)(b)(b)

Redrawing the circuit

3 Ω

2 Ω

4 Ω

j5 Ω

j 5Ω

j3 Ω

+

–

A

20 0° I1

I2

B

Applying Mesh Law

Mesh I

3I1 + j5I1 + j3I2 + 2I1 – 2I2 = 20∠0°

(5 + j5)I1 + (–2 + j3)I2 = 20∠0° ...(i)

Mesh II

2I2 + j5I2 + j3I1 + 4I2 – 2I1 = 0

(6 + j5)I2 + (–2 + 3j)I1 = 0 ...(ii)

From equations (i) and (ii)

I1 = 2.30∠–41.70° A

I2 = 1.064 ∠–137.8° A

VTh = VAB = I2 × (4) = 4.256∠–137.8° V

24.24.24.24.24. (c)(c)(c)(c)(c)

Since the voltage across the 5 Ω resistor is VR, therefore current flowing through it is:

I =

5

RV

...(i)

–

+ 5 VR

+

–

VR

1A

5Ω

500Ω

+ –

100V

1A

+

–

I

Now, writing the mesh equations, we have:

100 = 500 (I – 1) + VR – 5 VR ...(ii)

Substituting equation (i) into equation (ii) yields,

500 + 100 = 500 5

5

R

R R

V

V V+ −

or VR =

600 5

6.25 V

480

×

=

- 14. © Copyright:www.madeeasy.in

20 Electrical Engineering

and I =

6.25

1.25 A

5

=

Now, power absorbed by 500Ω resistor is

P500Ω = (Ι – 1)2 × 500 = (1.25 – 1)2 × 500 = 31.25 W

and power absorbed by 5Ω resistor,

5P Ω =

( ) ( )2 2

6.25

7.8125 W

5 5

RV

= =

∴ Total power dissipated = 39.06 W

25.25.25.25.25. (d)(d)(d)(d)(d)

For current to be in phase with applied voltage imaginary part of impedance should be zero.

Redrawing the circuit

j LX j LX

R R

–j CX

–j CXRR

Zeq

Zeq =

( ) ( )

2

L CR jX R jX+ + −

=

2

C

L

C

jR X

R jX

R jX

− ⋅

+ + −

=

2 2

( )

2

C

L C

C

jR X

R jX R jX

R X

⋅

+ − +

+

equating imaginary part to zero

2

2 2

2

C

L

C

R X

X

R X

−

+

= 0

R2XC = ( )2 2

L CX R X⋅ +

⇒ XL =

2

2 2

C

C

R X

R X+

26.26.26.26.26. (d)(d)(d)(d)(d)

With ‘S’ open:

Ceq =

( )1 2 6

2 F

1 2 6

+ ×

= µ

+ +

∴ i = i3 = eq

dV

C

dt

1 Fµ

2 Fµ 6 Fµ

C

–+

V = 100 sin 1000 t (v)

i

i2

i1 i3

V1 V2

+ –+ –

i3 = ( ) ( )6

2 10 100 sin 1000−

×

d

t

dt

= (2 × 10–6) × 100 × 1000 × (cos 1000 t)

i3 = 0.2 cos (1000t) A

- 15. © Copyright:www.madeeasy.in

21CTEE17 • NetworksTheory

V2 = 3 6

1 1

0.2cos(1000 )

6 10

dt t dt

C −

=

×

∫ ∫i

V2 = ( )6

0.2 sin1000

33.33 sin 1000 V

10006 10

t

t−

= ×

V1 = V – V2 = 100 sin (1000 t) – 33.33 sin (1000 t)

V1 = 66.67 sin (1000 t) V

27.27.27.27.27. (a)(a)(a)(a)(a)

Converting the circuit into s-domain

Z(s) =

1

1 1

sC

R sL

+ +

+

–

1/sC

+

–

sLR VC1/s

Z(s)Z(s) = 2

1

1 11

s

s ss

s

=

+ ++ +

VC = Voltage across capacitor

= Voltage across Z(s)

= Z(s) ⋅ I(s)

Z(s) VC

+

_

I( )s

1/s

= 2

1

1

s

ss s

⋅

+ +

VC(s) = 2

1

1s s+ +

Taking inverse Laplace

vC(t) = 22 3

sin

23

t /

e t−

28.28.28.28.28. (b)(b)(b)(b)(b)

+

–

+

–

V1 V2

10 Ω

5 Ω

2 Ω4 Ω

25 V

50 V

2 Ω

21

With two principal nodes 1 and 2 and the third chosen as the reference node, by using KCL, the net current

out of node 1 must be equal to zero.

- 16. © Copyright:www.madeeasy.in

22 Electrical Engineering

Applying KCL at node-1, we have:

1 1 1 225

2 5 10

V V V V− −

+ + = 0

or, 8V1 – 1V2 = 50 ...(i)

KCL at node 2 gives,

2 2 2 150

2 4 10

V V V V+ −

+ + = 0

–8V1 + 68V2 = –2000 ...(ii)

By solving both the equations:

∴ V1 = 2.61 V

and V2 = –29.1 V

∴ I2Ω resistor = 1 2.61

1.30 A

2 2

V

= =

29.29.29.29.29. (b)(b)(b)(b)(b)

at t = 0–

vC = I × R2

R2

I

+

–

vC( )tC

at t = 0+

vC(0–) = vC(0+) = IR2

Req

IR2R2R1

vC(∞) = 0

(∵ capacitor will discharge fully)

Req = 1 2

1 2

R R

R R+

vC(t) = [ ](0) ( ) ( )

t

C C Cv v e v

−

τ− ∞ + ∞

vC(t) =

1 2

1 2

( )

2 Volts

t R R

R R C

R e

− +

⋅

⋅I

- 17. © Copyright:www.madeeasy.in

23CTEE17 • NetworksTheory

30.30.30.30.30. (b)(b)(b)(b)(b)

Let the additional parallel resistance required be Rx as shown below.

8081Ω Rx 3640ΩIs

3.2 mH

15.7 nF

Given, new bandwidth after adding an additional resistance Rx = 6 kHz.

Quality factor QP =

3

3

22.3 10

3.72

6 10

rf

BW

×

= ≈

×

Since, QP = ωrCReq , therefore

3.72 = 2π (22.3 × 103) (15.7 × 10–9) Req

⇒ Req = 1691 Ω

∵

eq

1

R

=

1 1 1

8081 3640 R

+ +

x

or,

1

1691

=

1 1 1

8081 3640 R

+ +

x

After solving, we get; Rx = 5184.20 ≈ 5184 Ω