Car ee 216-dld

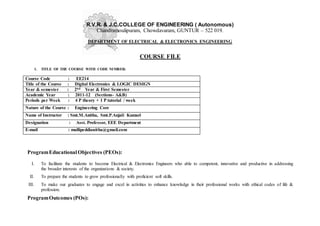

- 1. R.V.R. & J.C.COLLEGE OF ENGINEERING ( Autonomous) Chandramoulipuram, Chowdavaram, GUNTUR – 522 019. DEPARTMENT OF ELECTRICAL & ELECTRONICS ENGINEERING COURSE FILE 1. TITLE OF THE COURSE WITH CODE NUMBER: Course Code : EE214 Title of the Course : Digital Electronics & LOGIC DESIGN Year & semester : 2nd Year & First Semester Academic Year : 2011-12 (Sections- A&B) Periods per Week : 4 P theory + 1 P tutorial / week Nature of the Course : Engineering Core Name of Instructor : Smt.M.Anitha, Smt.P.Anjali Kumari Designation : Asst. Professor, EEE Department E-mail : mallipeddianitha@gmail.com ProgramEducationalObjectives (PEOs): I. To facilitate the students to become Electrical & Electronics Engineers who able to competent, innovative and productive in addressing the broader interests of the organizations & society. II. To prepare the students to grow professionally with proficient soft skills. III. To make our graduates to engage and excel in activities to enhance knowledge in their professional works with ethical codes of life & profession. ProgramOutcomes (POs):

- 2. The graduate will demonstrate/ exhibit PO1) An ability to apply knowledge of Applied Mathematics, Basic Engineering sciences. PO2) An ability to identify, formulate and solve Electrical Engineering problems. PO3) An ability to analyze and interpret data while designing components and systems to meet the needs of industry within realistic constraints. PO4) Knowledge of contemporary issues. PO5) An ability to work and visualize effectively in laboratories, industries among multidisciplinary teams. PO6) Skill to use modern engineering tools, software and equipment in modern Electrical Engineering practice. PO7) An understanding of managerial, professional and ethical responsibility. PO8) An ability to communicate effectively in both verbal and written form. PO9) The understanding of the impact of engineering solutions in global, economic, Environmental, safety and societal context. PO10) Recognition of the need and ability to engage in lifelong learning. PO11 An ability to carry out interdisciplinary programs and research in National/International organizations. Course Objectives: To understand different types of number systems used in digital systems. Boolean algebra concepts which are used to describe mathematical relationship between input and output signals. To understand Karnaugh maps and tabulation method which are used to construct combinational circuits.

- 3. To understand about the memory elements such as flip-flops, counters, registers To understand about the programmable logic devices like PAL, PLA and different types of IC logic families. Course Outcomes: Understand the basic digital logic fundamentals such as numbering system, binary codes and Boolean algebra Understand various methods and techniques to simplify the Boolean algebra functions. Able to design the various digital circuits like encoders, decoders and counters. Become familiar with different types of memory elements and IC logic families. II/IV Year B.Tech. - First Semester EC/EE 214 DIGITAL LOGIC DESIGN UNIT – I [Text Book 1] NUMBER SYSTEMS AND CODES: Decimal, Binary, Octal, Hexadecimal Number systems and their conversions, Arithmetic additions, subtraction using the method of complements, Multiplication and division. Codes: BCD, Excess 3, Gray, Alphanumeric and Error detection codes. BOOLEAN ALGEBRA: Boolean expressions and theorems, Logic gates, Universal gates, Canonical and standard forms, Boolean functions, simplification of Boolean functions using K maps (up to five variables), Minimal functions and their properties, Tabulation method, NAND implementations two level and Multilevel. (19) UNIT – II [Text Book 1] COMBINATIONAL LOGIC CIRCUITS: EX-OR, EX-NOR Circuits, General design procedure for Combinational logic circuits, Design and applications of Binary Adders and Subtrac tors, Comparators, Encoders, Decoders, Multiplexers and Demultiplexers, Design of BCD to 7 Segment Decoder, Parity Generator and Checker, Error Detection and Correction using Hamming Code, BCD Adder / Subtractor, Carry look ahead adders. (16) UNIT – III [Text Book1] SEQUENTIAL LOGIC CIRCUITS: Latches, Characteristic Table, Characteristic Equation, Excitation table, State table and State diagrams for SR, JK, Master Slave JK, D and T Flip -flops, Conversion from one type of Flip-flop to another, Shift Registers, Analysis and Synthesis of Sequential Circuits -Sequence Generator, Sequence Detector, Parity Generator. COUNTERS USING FLIP- FLOPS: Design of Ripple counters, Synchronous counters, Up/Down counters using Flip-flops. (14) UNIT – IV [Text Book 1] IC LOGIC FAMILIES: RTL, DTL, TTL, ECL, MOS, CMOS and IIL families and their comparison. Programmable Logic Devices: Programmable Logic Arrays (PLA), Programmable Array Logic (PAL), CPLD, FPGA. (11) Learning Resources: Text Books:

- 4. 1. M Morris Mano, Digital Logic and Computer Design, PHI/Pearson Education, 2003. 2. RP Jain, Modern Digital Electronics, 3rd Edition, TMH, 2003 3. Fundamentals of Digital Circuits, A.Anand Kumar,4th Edition,Pearson Education. Reference Books: 1. Zvi Kohavi, Switching and Finite Automata Theory, 2nd Edition, TMH, 1978 2. Taub and Schilling, Digital Integrated Electronics, Mc-Graw Hill, 1977. Web References: 1. http://www.ece.ubc.ca/~saifz/eece256.htm 2. http://nptel.iitm.ac.in/courses/Webcourse-contents/IIT-%20Guwahati/digital_circuit/frame /index.html Mapping of course outcomes with Pos: Course Outcomes Description POs CO1 To understand different types of number systems used in digital systems. Boolean algebra concepts which are used to describe mathematical relationship between input and output signals. PO1,PO9 CO2 To understand Karnaugh maps and tabulation method which are used to construct combinational circuits PO2, PO5 CO3 To understand about the memory elements such as flip-flops, counters, registers. PO2,PO3, PO5,PO10,PO11 CO4 To understand about the programmable logic devices like PAL, PLA and different types of IC logic families. PO10,PO11 Mapping of course outcomes with QPs: Question No. Description A1Q1 Write notes on error detecting and error correcting codes CO1 A1Q2 What do you mean by carry look ahead adder and draw its logic diagram? CO2 A2Q1 Draw the circuit diagram for 3-input TTL NAND gate and explain its operation. (b) Draw and explain the circuit diagram of a 3-input IIL NOR gate. CO3

- 5. A2Q2 What is a race condition? How it is eliminated in JK – master slave flip-flop? Explain with neat diagram. (b) Convert D- flip flop into (i) T-flip flop (ii) JK- flip flop. CO4 S1Q1 (a) Add (1101.1110)2 to (0001.1011)2. (b) What are universal gates? (c)Add (327.54)8 to (665.37)8. (d) Convert the gray code 101101 to binary equivalent. (e)Convert the Boolean expression ABCDE+ABE1+ACD to min terms. (f) What is parity generator? CO1, CO2 S1Q2 a) Explain weighted codes and non-weighted codes and also explain self complemented Weighted and non weighted codes. (b) Perform the each of the following decimal additions in 8421 BCD. (i) 24 + 18 (ii) 48+58 (OR) (c) Implement Boolean function for Ex-OR gate using NAND gates and also implement for Ex-NOR gate using NOR gates. (d) Find the minimal SOP expression using k-map for the following expression(w,x,y,z)=∑(1,5,6,12,13,14)+d(2,4,8) CO1 S1Q3 (a) Design BCD to 7-segment display decoder. (OR) (b) Design 3-bit even parity generator and 3-bit odd parity checker. CO2 S2Q1 a.) Give the excitation table for T-flip-flop. b) Which type of logic gate is faster? c) What is the figure of merit of a digital IC? d) Differentiate combinational and sequential circuit. e) How many flip-flops required generate a sequence of 9 bits? f) Define the terms fan-in and fan-out CO3,CO4 S2Q2 Design a sequential circuit with two D flip-flops A and B, and one input x. When x=0, the state of the circuit remains the same. When x=1, the circuit goes through the state transitions from 00 to 01 to 11 CO3

- 6. to 10 back to 00, and repeats. (OR) (a) Draw the logic diagram of a 4 bit universal shift register and explain its operation. (b) Design mod-5 synchronous counter. S2Q3 (a) Explain briefly the characteristics of MOS logic and write a note on CMOS logic. (b) Differentiate between PAL and PLA. (OR) (a) Implement a PLA structure for a full subtractor. (b) Explain briefly about RTL logic family. CO4

- 7. Content Delivery Methods: M1: Lecture interspersed with discussion M2: Guest Lecture M3: Tutorial M4: Field Visits M5: Experimental (Models, Virtual, simulation) M6: Group Assignments LESSON PLAN Period Unit Learning objectives TOPICS TO BE COVERED Chapter in the text book/reference Teaching aid Delivery method 1. UNIT- I To give entire idea about Decimal, Binary, Octal, Hexadecimal number systems and their conversions-Arithmetic operations Number Systems and their base conversions, decimal, binary, octal, Hexa decimal M Morris Mano Black Board M1 2. To describe codes: BCD, Excess 3, Gray, Alphanumeric and error detection codes. Number Systems and their base conversions, decimal, binary, octal, Hexa decimal M Morris Mano Black Board M1 3. To narrate the Boolean expressions Arithmetic addition, subtraction using the method of complements M Morris Mano Black Board M1 4. To demonstrate theorems Arithmetic addition, subtraction using the method of complements Black Board M1 5. To provide the basic concepts used in the design & analysis of digital system Arithmetic addition, subtraction using the method of complements M Morris Mano Black Board M1 6. Multiplication and division.. M Morris Mano Black Board M1 7. Codes; BCD, excess-3, Gray, Alphanumeric M Morris Mano Black Board M1 8. Tutorial M Morris Mano Black Board M1 9. Simplification of Boolean expressions M Morris Mano Black M1

- 8. and theorems Board 10. All logic gates (AND, OR, NOT and including Universal gates (NAND, NOR), Canonical & Standard Forms - Minterms & Maxterms, sum of minterms, product of max terms, conversion between Canonical & standard forms M Morris Mano Black Board M1 11. All logic gates (AND, OR, NOT and including Universal gates (NAND, NOR), Canonical & Standard Forms - Minterms & Maxterms, sum of minterms, product of max terms, conversion between Canonical & standard forms M Morris Mano Black Board M1 12. Boolean function simplification of Boolean functions using K-maps, Boolean functions, map method, two & three variable map & four variable map & five variable map with an example. M Morris Mano Black Board M1 13. Boolean function simplification of Boolean functions using K-maps, Boolean functions, map method, two & three variable map & four variable map & five variable map with an example M Morris Mano Black Board M1 14. Tabulation Method, Determination of prime implicants, selection of prime implicants with an example, NAND & NOR implementation. M Morris Mano Black Board M1 15. Tabulation Method, Determination of prime implicants, selection of prime implicants with an M Morris Mano Black Board M1

- 9. example, NAND & NOR implementation. 16. Two level & multi-level implementation & IEEE symbols M Morris Mano Black Board M1 17. Tutorial M Morris Mano Black Board M1 18. Ex-OR, EXNOR circuits, Graphic symbols, algebraic functions, truth table, design procedure for combinational logic circuits, design procedure with simple example M Morris Mano 19. Binary adder & subtractor, Half adder, truth table, various implementations of Half adders, full adders, maps for full adder, implementation of full adder with two half adders & an OR gate, Half Subtractor, Full subtractor, maps for full subtractor M Morris Mano Black Board M1 20. Binary adder & subtractor, Half adder, truth table, various implementations of Half adders, full adders, maps for full adder, implementation of full adder with two half adders & an OR gate, Half Subtractor, Full subtractor, maps for full subtractor M Morris Mano Black Board M1 21. Comparator - a bit magnitude comparator, Decoders, 3-8 line decoder, design of BCD to decimal decoder, implementation of full adder with decoder, encoder M Morris Mano Black Board M1 22. UNIT- II To teach the general design procedure for combinational Multiplexer & Demultiplexer, 4 to 1 line MUX, Boolean function implementation using MUX. M Morris Mano Black Board M1

- 10. logic circuit. 23. To describe the parity generator and checker Design of BCD to 7 segment decoder, design procedure & implementation with decoder, parity generators & Checker. M Morris Mano Black Board M1 24. To define error detection and correction using hamming code Design of BCD to 7 segment decoder, design procedure & implementation with decoder, parity generators & Checker. M Morris Mano Black Board M1 25. To provide various methods & techniques suitable for a variety of digital system Error detection & correction using Hamming Code. M Morris Mano Black Board M1 26. Tutorial M Morris Mano Black Board M1 27. BCD Adder/ Sub tractor Block diagram, derivation, M Morris Mano Black Board M1 28. BCD Adder/ Sub tractor Block diagram, derivation, M Morris Mano Black Board M1 29. BCD Adder/ Sub tractor Block diagram, derivation, M Morris Mano Black Board M1 30. Excess-3 adder & sub tractor M Morris Mano Black Board M1 31. Excess-3 adder & sub tractor M Morris Mano Black Board M1 32. Excess-3 adder & sub tractor M Morris Mano Black Board M1 33. Carry-look A head adder generator M Morris Mano Black Board M1 34. JK Flip Flop, SR Flip Flop, T Flip Flop & DFF, Truth table, characteristic equation, Ch.table, Block diagram of all FF's, Excitation table. M Morris Mano Black Board M1

- 11. 35. UNIT- III To narrate the sequential logic circuit Edge Triggering FF's, Waveforms, applications of FF's. M Morris Mano Black Board M1 36. To explain about characteristic table-characteristic equation- Excitation table-state table and state diagrams for latches Design procedure for sequence logic circuit, conversion of FF's from one type to another (JK M Morris Mano Black Board M1 37. To teach the design procedure of Flip Flop ,Registers ,Counters. Design procedure for sequence logic circuit, conversion of FF's from one type to another (JK M Morris Mano Black Board M1 38. To provide many of the classical rules of logic design useful in the design of circuit components such as MS1 & LS1 devices and also to bridge the gap between these classical rules & practical design Design procedure for sequence logic circuit, conversion of FF's from one type to another (JK M Morris Mano Black Board M1 39. Design procedure for sequence logic circuit, conversion of FF's from one type to another (JK M Morris Mano Black Board M1 40. Design of Shift Registers (SISO, SIPO, PISO, PIPO). M Morris Mano Black Board M1 41. Design of Ring Counter & twisted Ring Counter & O/P waveforms using Flip Flops M Morris Mano Black Board M1 42. Tutorial M Morris Mano Black Board M1 43. Bidirectional Shift Registers & Design of sequence generator. M Morris Mano Black Board M1 44. Ripple or Asynchronous counter, 3 bit M Morris Mano Black M1

- 12. Binary counter O/P waveforms. Board 45. 44 Step down Counters using Flip Flops. M Morris Mano Black Board M1 46. 45 RTL, DTL, Logic operation, Loading considerations, Noise margin, propagation delay & other characteristics M Morris Mano Black Board M1 47. TTL (Transistor & Transistor Logic) operation of TTL NAND gate, Totem pole O/P, Open Collector O/P, Schottkey TTL, tri state logic M Morris Mano Black Board M1 48. UNIT- IV 1To study IC logic families: RTL, DTL, TTL, ECL, MOS, CMOS AND IIL FAMILIES. TTL (Transistor & Transistor Logic) operation of TTL NAND gate, Totem pole O/P, Open Collector O/P, Schottkey TTL, tri state logic M Morris Mano Black Board M1 49. To narrate the comparison of IC logic families. TTL (Transistor & Transistor Logic) operation of TTL NAND gate, Totem pole O/P, Open Collector O/P, Schottkey TTL, tri state logic M Morris Mano Black Board M1 50. To give the design procedure of Programmable logic array, Programmable array logic TTL (Transistor & Transistor Logic) operation of TTL NAND gate, Totem pole O/P, Open Collector O/P, Schottkey TTL, tri state logic M Morris Mano Black Board M1 51. ECL configuration operation & its characteristics M Morris Mano Black Board M1 52. MOS & CMOS operations, IIL family M Morris Mano Black Board M1 53. Characteristics, comparison of different logic families. M Morris Mano Black Board M1 54. Characteristics, comparison of different logic families. M Morris Mano Black Board M1 55. Characteristics, comparison of different M Morris Mano Black M1

- 13. logic families. Board 56. Characteristics, comparison of different logic families. M Morris Mano Black Board M1 57. MSI and LSI: Programmable logic arrays M Morris Mano Black Board M1 58. MSI and LSI: Programmable logic arrays M Morris Mano Black Board M1 59. MSI and LSI: Programmable logic arrays M Morris Mano Black Board M1 60. Programmable array logic and sequential programmable devices M Morris Mano Black Board M1 61. Programmable array logic and sequential programmable devices M Morris Mano 62. Programmable array logic and sequential programmable devices M Morris Mano Evaluation Scheme: Component Duration (Minutes) Marks % Weight age Date & Time Venu Assignment Test-I 30 12 7 (75% from first best & 25% from next best) 08.09.2011 Main Block Assignment Test-II 30 12 05.11.2011 Main Block Sessional Test-I 90 18 18 (75% from first best & 08.09.2011 Cyber Block /Digital BlockSessional 90 18 05.11.2011

- 14. Test-II 25% from next best) Attendance ---- 5 5 (Attendance above 90% -5Marks ) --NA-- --NA-- End Semester Examination 180 70 70 17.11.2011 Cyber Block /Digital Block Chamber Consultation Hour: 2.50pm to 4.30PM (Wed, Sat) Venue: Staff Room

- 15. Course Assessment Report (CAR) Course Code EE214 Program B.Tech in EEE Course Title Digital Electronics & Logic Design A.Y 2011-12 Faculty Smt. M.Anitha Asst. Prof , Smt.P.Anjali Kumari, Asst. Prof Section A & B I. Mapping of Course outcomes to Program Outcomes (A.Y 2012-13): Program Outcome PO1 PO2 PO3 PO5 PO9 PO10 PO11 Mapped Course Outcomes CO1 CO2 CO3 CO3 CO2 CO3 CO1 CO3 CO4 CO3 II. Course Assessment: Direct method Assessment method Direct method Indirect method Course Outcomes Tool/ Task % score of COs % average of COs attainment % of COs attainment CO1 To give the overall idea of operation and control of power system to a power engineering student A1Q1 S1Q1 S1Q2 93 61 82 78.67 81.68 CO2 To make the student to understand economic load dispatch under various operational constraints and techniques to solve the problem A1Q2 S1Q1 S1Q3 93 61 86 80.00 80.98 CO3 To develop skills for applying them in future on various engineering applications A2Q1 S2Q1 S2Q2 79 82 75 78.67 86.01

- 16. CO4 To know the importance of quality of power P-F, Q-V control loops, AGC A2Q2 S2Q1 S2Q3 82 82 66 76.67 85.17 Note: %Score for course outcome= Percentage of students who got 60% or more marks Minimum Level for PO attainment: 60% CO Assessment through Internal exam evaluation and course end survey CO Direct Assessment in% (Int) Indirect Assessment in% PO mapping CO1 78.67 81.68 PO1(2),PO9(2) CO2 80.00 80.98 PO2(2), PO5(2) CO3 78.67 86.01 PO2(2),PO3(2), PO5(2),PO10(2),PO11(2) CO4 76.67 85.17 PO10(2),PO11(2) POS attainment by direct and indirect methods Overall= 70% of Direct Assessment + 30% of Survey POS Direct Assessment Indirect Assessment Over all PO attainments % of Target PO1 78.5 81.68 79.45 60 PO2 84.5 83.5 84.20 60 PO3 84.5 86.01 84.95 60 PO5 81.585 83.5 82.16 60 PO9 78.33 81.33 82.16 60 PO10 78.25 82.41 79.50 60 PO11 78.25 85.59 80.45 60 PO ATTAINMENT

- 17. 74 76 78 80 82 84 86 88 PO1 PO2 PO3 PO5 PO9 PO10 PO11 Direct assessment Indirect Assessment Over all PO attainments

- 18. II/IV B.Tech (1st Semester) A&B Sections-(For the year 2011-12) Result Analysis A & B SECTIONS No.of students appeared for the whole examination : 144 No. of students cleared whole examination : 122 Percentage of pass : 84.72% SECTIONWISE ANALYSIS A-Section No.of students appeared for the whole examination : 79 No. of students cleared whole examination : 67 Percentage of pass : 84.81% B-Section No. of students appeared for the whole examination : 65 No. Of students cleared whole examination : 55 Percentage of pass : 84.81% III. Comments and Recommendations for improvement All the program outcomes are attained to minimum expected level. The teacher, who are going to teach Digital Electronics & Logic Design (EE216) for the next academic year (i.e. 2012-13) are advised to show the students how to use scientific calculator for conversion of number systems and remedial classes to improve the pass percentage. Proper Questions are chosen to assess COs.