Bca1040 digital logic

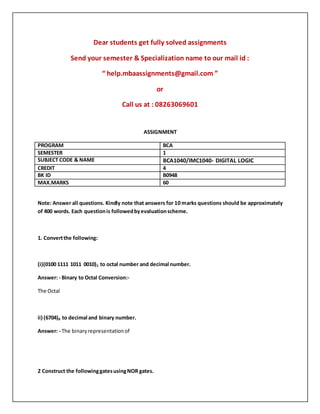

- 1. Dear students get fully solved assignments Send your semester & Specialization name to our mail id : “ help.mbaassignments@gmail.com ” or Call us at : 08263069601 ASSIGNMENT PROGRAM BCA SEMESTER 1 SUBJECT CODE & NAME BCA1040/IMC1040- DIGITAL LOGIC CREDIT 4 BK ID B0948 MAX.MARKS 60 Note: Answer all questions. Kindly note that answers for 10 marks questions should be approximately of 400 words. Each question is followed by evaluation scheme. 1. Convert the following: (i)(0100 1111 1011 0010)2 to octal number and decimal number. Answer: - Binary to Octal Conversion:- The Octal ii) (6704)8 to decimal and binary number. Answer: - The binary representation of 2 Construct the following gates using NOR gates.

- 2. Answer:- (a)XOR: - An XOR gate is constructed similarly to an OR gate, except with an additional NAND gate inserted such that if both inputs are high, the inputs to the final NAND gate will also be high, and the output will be low 3 Simplify the following truth table using k-map and find the reduced function f(x,y,z). X y z f(x,y,z) 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 0 1 0 1 0 1 1 0 1 1 1 1 1 Answer: - A Karnaugh map is an array containing 2k cells where k is the number of variables in the DNF expression to be minimized. Each cell of the Karnaugh map corresponds to one row of the truth table, or one assignment of truth values to the variables of the expression. K-maps is an alternate approach to representing Boolean functions. K-map representation can be used to 4. Draw the truth table of full adder and implement it using the logic gates. Answer: - Full adder:- This type of adder is a little more difficult to implement than a half -adder. The main difference between a half-adder and a full-adder is that the full-adder has three inputs and two outputs. The first two inputs are A and B and the third input i s an input carry designated as CIN. When a full adder logic is designed we will be able to string eight of them together to create a byte-wide adder and cascade the carry bit from one adder to the next.

- 3. Q.5 What are sequential circuits? Explain differences between sequential circuits and combinational circuits. Answer:-Sequential circuits:- In digital circuit theory, sequential logic is a type of logic circuit whose output depends not only on the present value of its input signals but on the past history of its inputs. This is in contrast to combinational logic, whose output is a function of only the present input. That is, sequential logic has state (memory) while combinational logic does not. Or, in other words, sequential logic is combinational logic with memory. Sequential logic is used to construct finite state machines Q.6 What are shift registers? Explain serial in serial out shift register. Answer: - A shift register is a cascade of flip flops, sharing the same clock, in which the output of each flip-flop is connected to the "data" input of the next flip-flop in the chain, resulting in a circuit that shifts by one position the "bit array" stored in it, shifting in the data present at its input and shifting out the last bit in the array, at each transition of the clock input. More generally, a shift register may be multidimensional, such that its "data in" and stage outputs are themselves bit arrays: this is implemented simply by running several shift Dear students get fully solved assignments Send your semester & Specialization name to our mail id : “ help.mbaassignments@gmail.com ” or Call us at : 08263069601