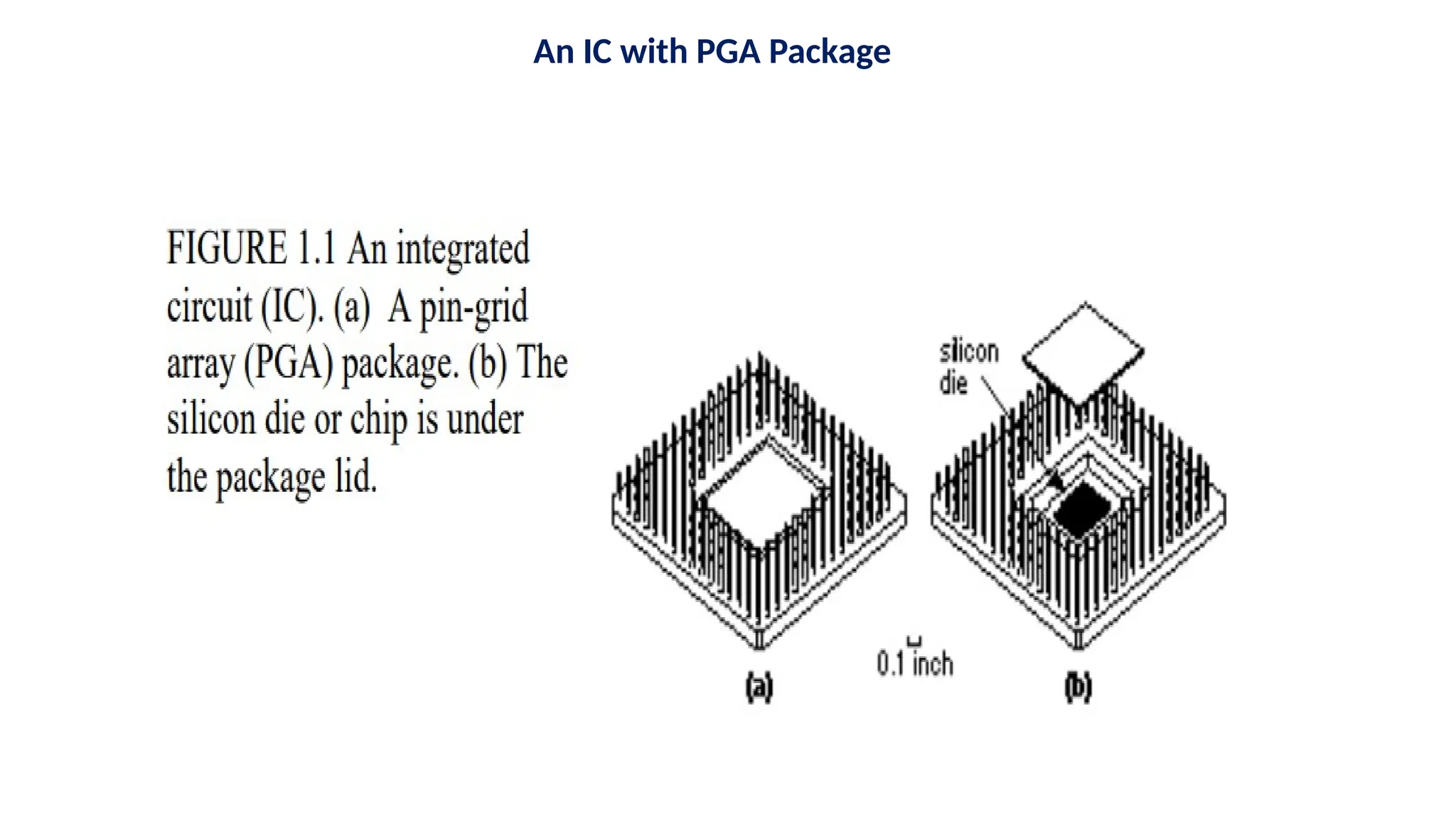

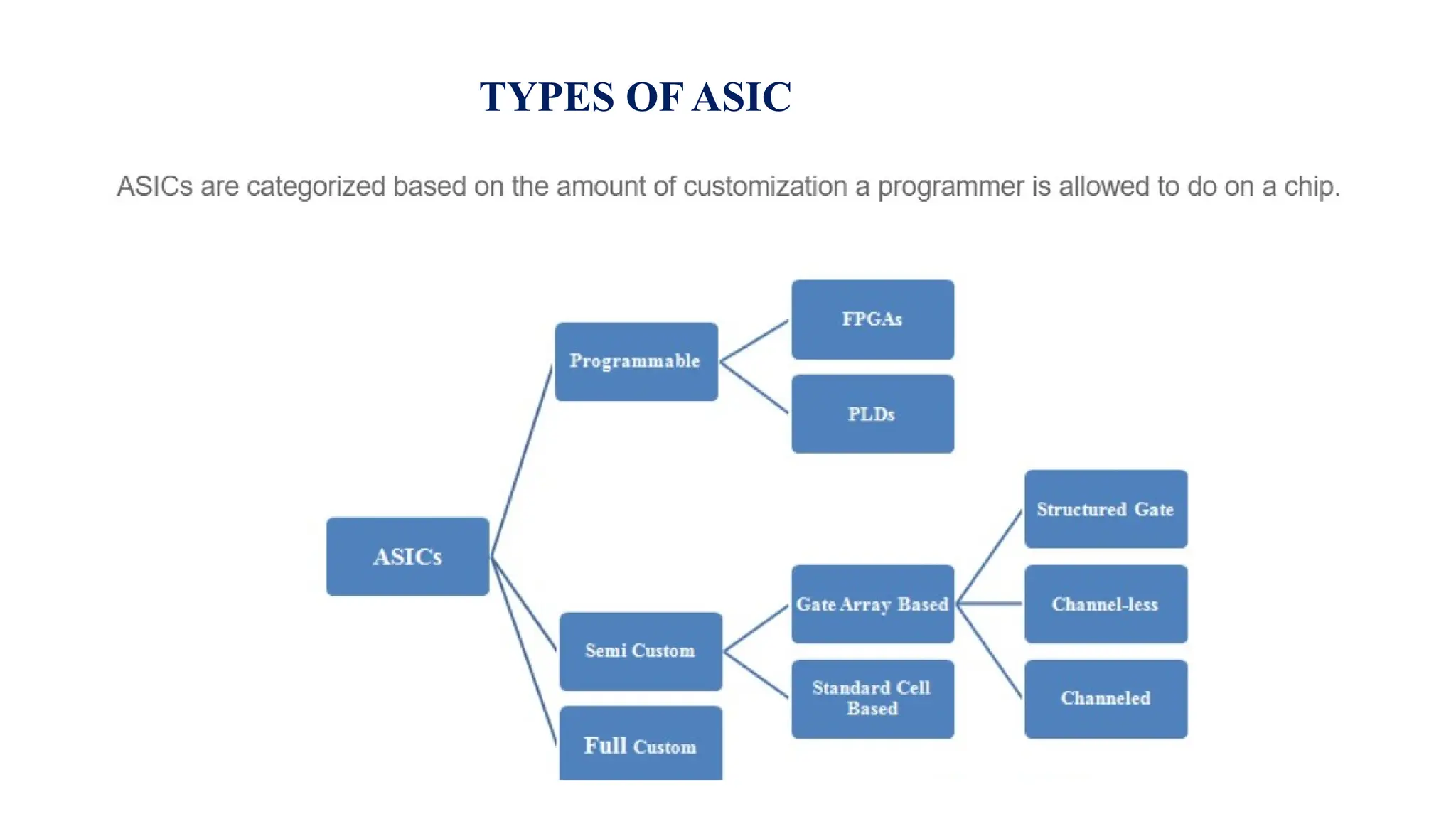

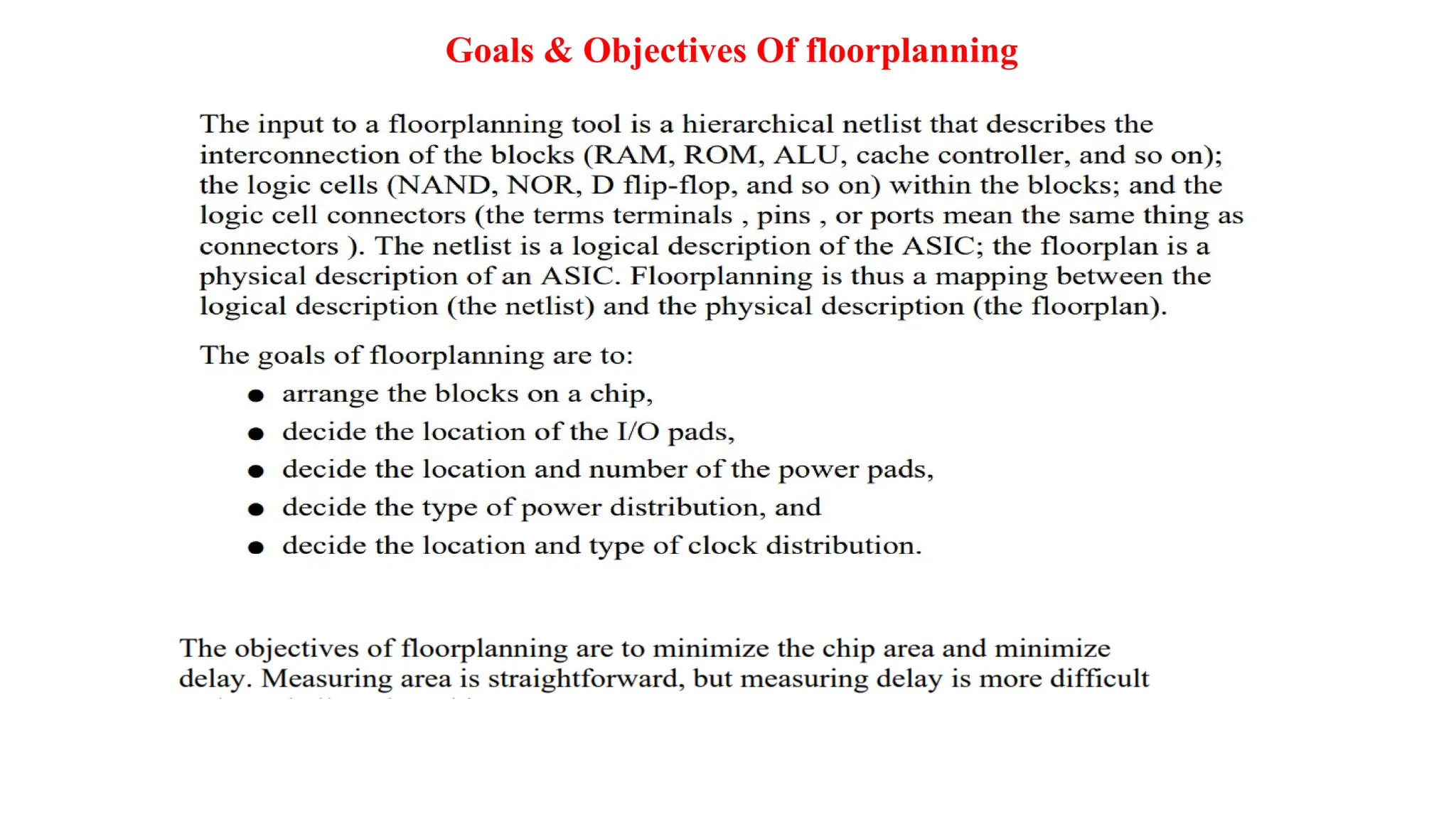

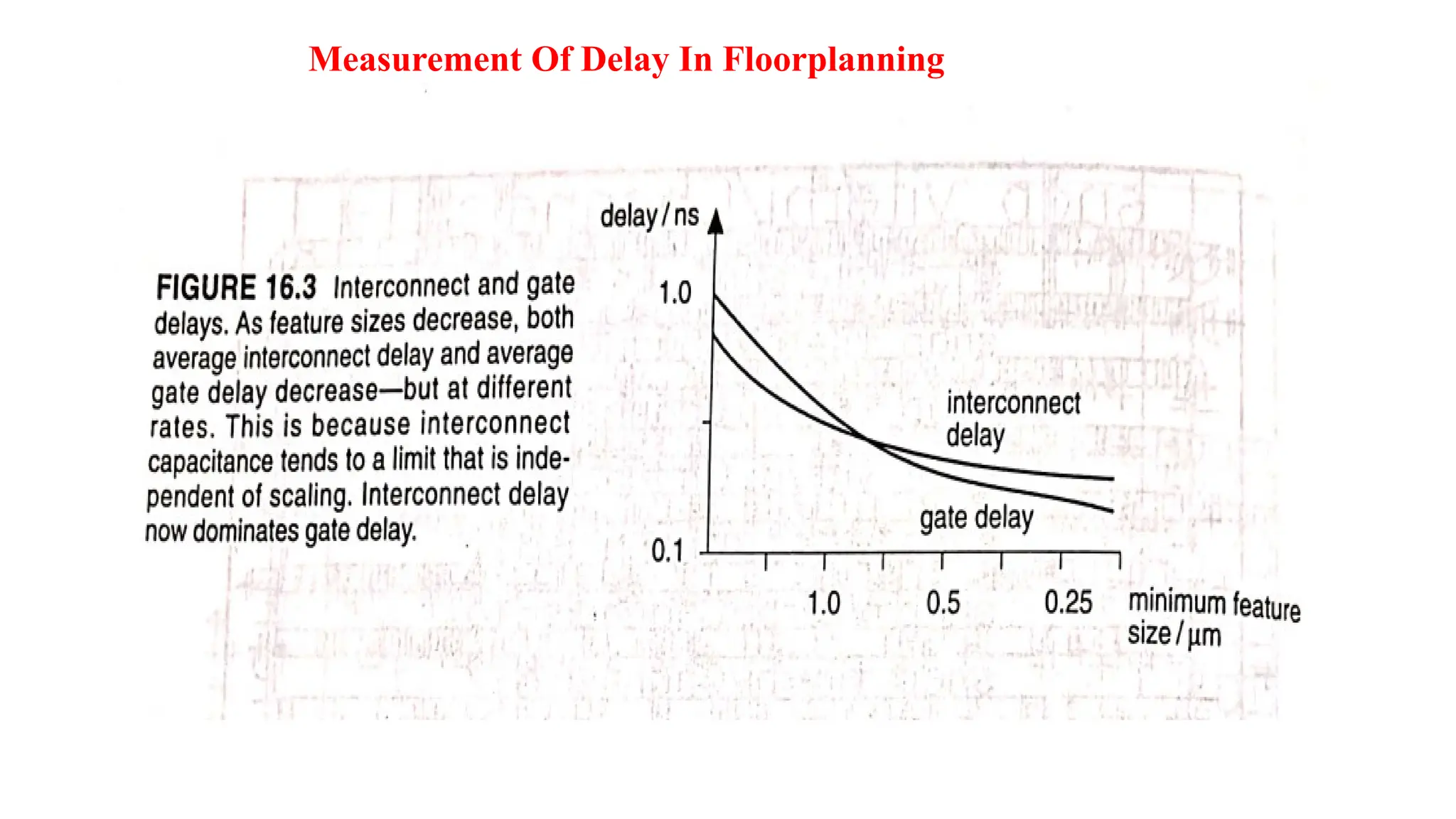

The document discusses the design and layout processes of application-specific integrated circuits (ASICs), including various types such as standard cell-based, gate arrays, and programmable logic devices like FPGAs. It covers key concepts like floorplanning, channel routing, and the flow of ASIC design, as well as verification methods like directed testing and their advantages and disadvantages. The content emphasizes measurement of delays in design and the incremental approach to ensure design correctness.