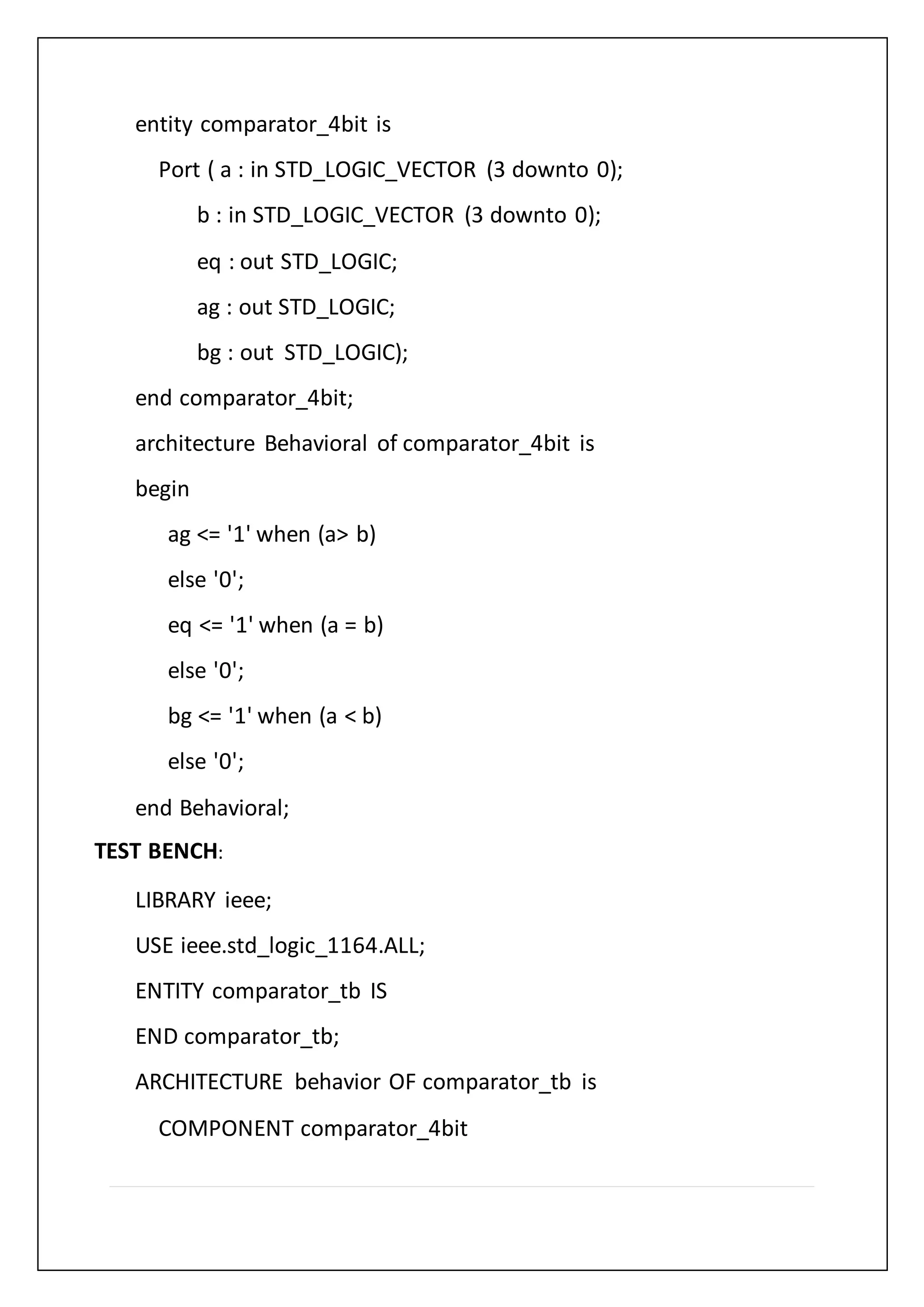

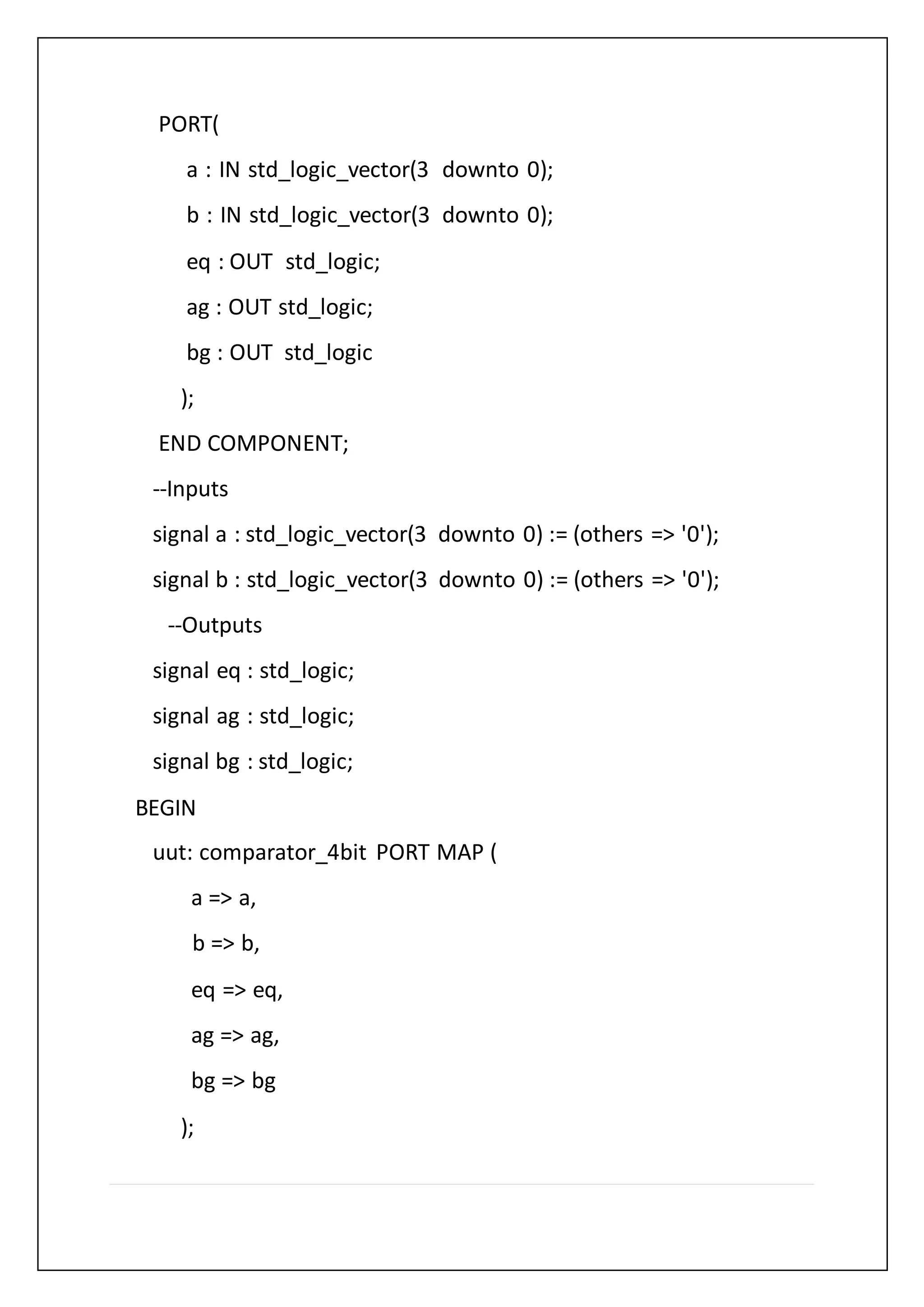

This document describes designing and simulating a 4-bit comparator using VHDL. It explains the theory of how a comparator works by comparing two binary numbers and determining if one is greater than, less than, or equal to the other. It provides the VHDL code to implement a 4-bit comparator and test bench code to simulate it by inputting different combinations of 4-bit numbers and observing the output. The simulation was successful in comparing the inputs as expected and generating the appropriate output signals to indicate less than, equal, or greater than.