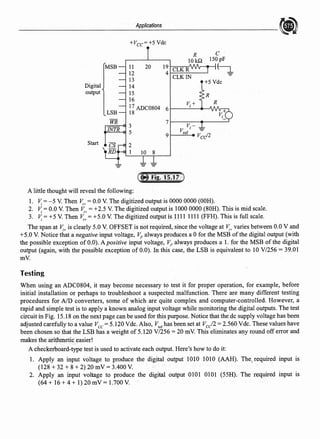

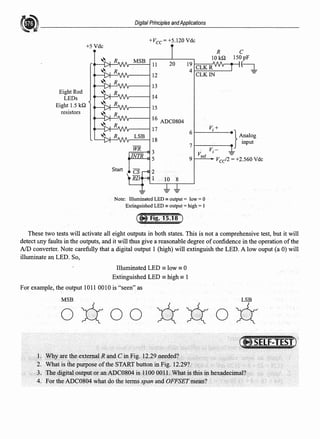

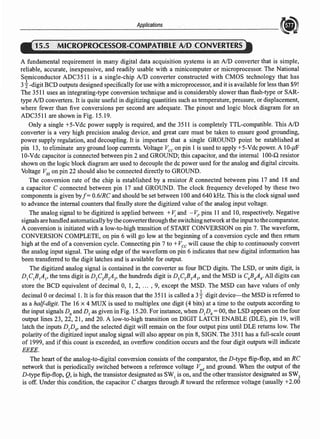

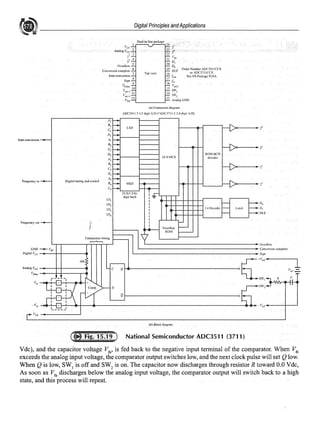

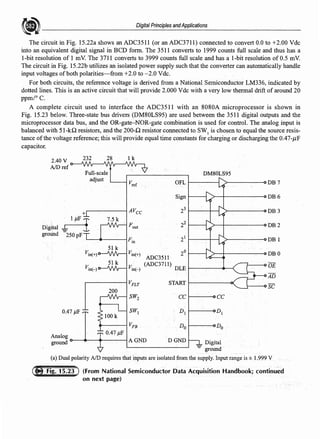

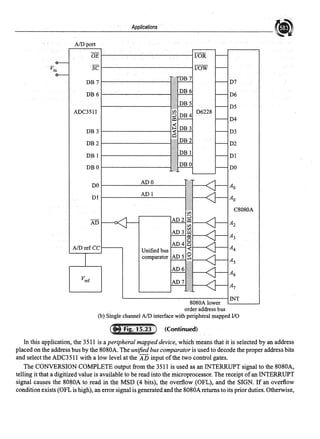

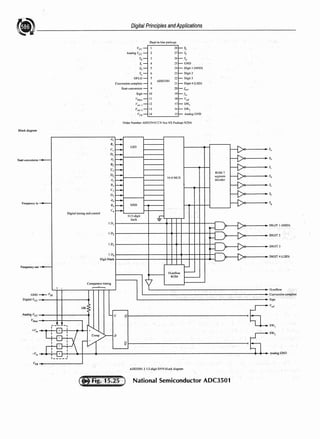

This document discusses applications of digital circuits, including multiplexing LED displays, frequency counters, time measurement circuits, and analog-to-digital converters. It focuses on multiplexing techniques to reduce power requirements for LED displays. Multiplexing works by pulsing each display digit sequentially rather than illuminating all digits continuously. With a high enough pulse repetition rate, the eye perceives steady illumination without flicker. The document provides examples of multiplexing common anode and common cathode LED displays, and discusses methods for generating control waveforms. It also covers applications using AD converters like the ADC0804 and ADC3511 to build instruments like digital voltmeters.

![NS85J88 43

Gu:ud

I I·::',·~~r==-i==1--~---~-:n;:'.=l---'!:Hl____

r;=-.:--::::-:--- '---·vv y.fJ / / , ,-, ~,10-t-'NH-==

:J

:11s· .~:· r··---,;~.;;;;··-----, -, ' - -.- I , ,-, - ,-, I~ ': l 1

, 340-5 1 1 r,--' I ,,-- 14 v

I I ~ I I "' .. -

,-,-+--l-:'~- ~ : T ' " ' I

- ~ I

4

j' 11• 5 I 'f 'f,t--'fA,_J__

. - : I ' " ' 11917 1,~ I ~ 1

lrJN914 R{S.232:

LMJJ6

1

±1% I I I I -<,

'"' :;,i ,, I ,m,.., -, -j--<

T 2'00 µI' I F ;, R, { I GND R i

. ' "''' ool, T. •; f::'--]l,' i D /;,. f )_ 4 'l•, -

I '------() :.::______ J - - I - ~ -

l

l ,;:,•pF I I

~D f I

!

~-·,

--- .7.5k I

150k 50k I I ,;' ;" • 17 118 19 '20 ' I -

::: :::: ~ 't:: , . .. I 122 2J ,,

4

Off 5' .,. _'< ii, ,~ 1' .:i2 0 ,... - 2

.5 26 27 ,!

l>CI l o, . - - ~ 0 ( 1 ~ -'

·~ s • ' ' ' ' ' ' ' ·1

S,. IOllk i3 ~ ;:; ;j ~ o

, ~ "~ _m ·":"· ,ooa,orn

(

<n.1.L. l 11> 11i', I ""' oc, . ,

- 20: .'.Ok >ll.01%1

, _ .~ -"" _ ~[ ] f >

o1!JQL ·v ·•~ .I ;j' 2 ' ~- ,<> 'i. oo Q i,

---,e------==------t(1

'1-~0.1

47

~/:·IF!=-j= 14 13 1 ' '§ §

0

g 5 ·,:

I (]) 12 Ill 110 9 Is l " ~ 0 "- .:"

_ _ _ __J__,; ~ L - r . ,I' , 4 3 , ~I

:::. "'- ,'" L' -

< 9.9M<l J I _J !

' ..,., -

.b -, '"•'

' ...

1 - ""'' "''"= ,,.w - ,

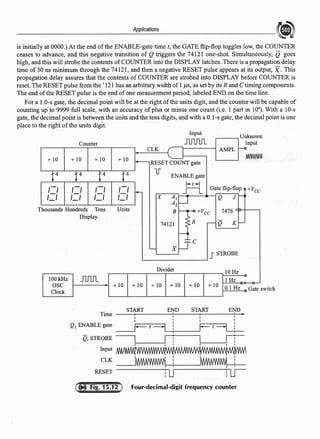

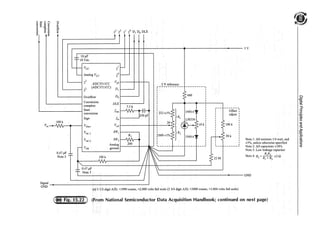

otherwise specified x5 Yo unless

- I~ote 2: All capacitors ±10%

i otc 3: Low leaka ,cc· .

Note 4: R R l(R } apacttor required

I 2 I · R2) =R3± 25 Q

t·)

V(-)

:g

~

t

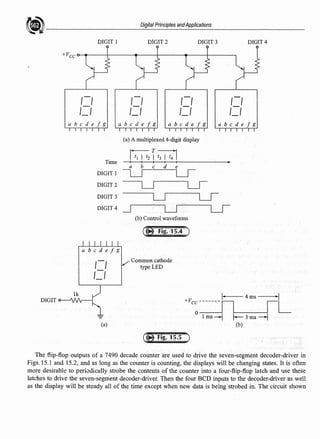

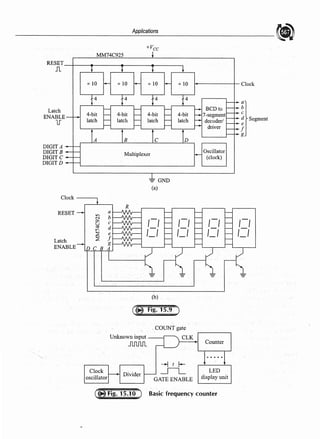

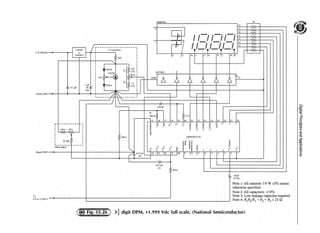

3i digit DVM, Four decade; ±0.2, +0.2, ±20, and ±200 Vdc (National Semiconductor)](https://image.slidesharecdn.com/unit-5digitalelectronics-230930120401-5bd199ba/85/unit-5-digital-electronics-pdf-32-320.jpg)

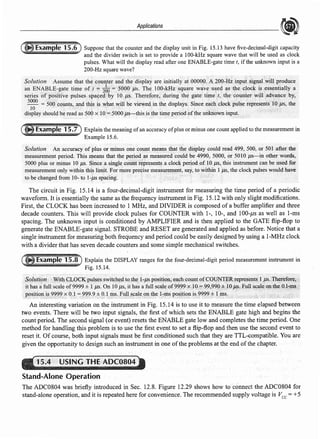

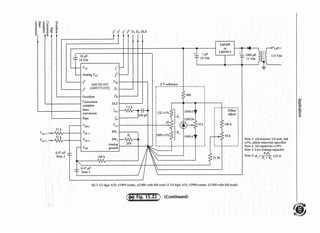

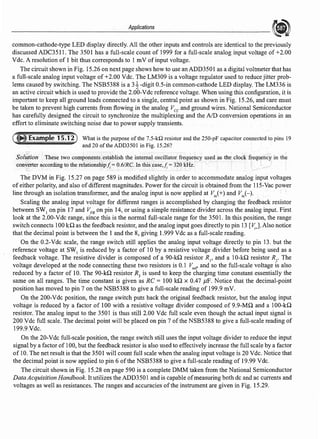

![Technical specifications

DC volts < ± I% accuracy

ranges 2 V, 20 V, 200 V, 2 kV

input impedance 2 V range, > IO Mn

20 V to 2 kV range, 10 MQ

AC RMS volts < ± l% accuracy

ranges 2 V, 20 V, 200 V, 2 kV

(40 to 5 kHz sinewave)

DC amps < ± I% accuracy

ranges 200 µA, 2 mA, 20 mA, 200mA, 2A

Ohms < ± l% accuracy

ranges 200 n, 2Hl. 20kQ, 200kQ, 2 MQ

'Al MU

tll«i

1 ~' ---¥Iv--,

,v

20 -

~

'1MU

OJ""

i'""

J:!U

~ V

}fl'

',,l!s

Note I: All V,, connections should use a single Vee

point and all ground/analog ground connection should

use a single ground/analog ground point.

Note 2: All resistors are 1/4 watt unless otherwise

specified

Note 3: All capacitors arc ±10%

Note 4: All op amps have a 0. I /IF capacitor

connected across the V+ and V- supplier

Note 5: All diodes arc IN914

l2lH2

:,.;s115w,

J.10tl

"··'~ L. 111 ·I II l1

1

t

la,

~1

<JV.=.,.

:J; il ' !~,,

l'I J.. ~l.l.1h( ,~?

IOHl~ ~U

1)0~0

~

,.,..

"°'.""~ """" ' ~ L--+-~____.__....-t-1-4--~

01~. JrnlV ,,_.!-:-°

l j ( ~

JOµl nn

d~:,

.....

X2(l

!Oll~O

nc o !':,

Ohnis

Cr,nmwn WHl!"-•

Vuhs

amp·,°--

Ohu1{

I LU l~ l

~ l p A

... '""'•

!OHU!"·020m,

1~ ~z.1•~]00 mA9 r

~ 1 ,

I ~l l"i,

rcc-1'-

;

...

l){'I .~,,- ~ ~ c ; - W v - ~

lK AC

M<,U 1~,,

J'lf>U!I·!, ·1

~ l ) f . ) U

2U!

l'lf,Hl 1"~

~

;;::. PJ.d

h'-'

11HJ I H"'

,r

511!

,~ ~t=1'II./). Ht

H)9 r

~ ~ 1 U

1.w,:-.mo !~o

""'"' l~;:·

~'"·::'""J.~t.LLLLL.1~ 11'

*•U71if

N :;..

l5Wt.J

1>D-1~Hl /•1" ,,ht dit!it;i! m"1mnd,·r

::;::1011F

tru

tU7

,,,

I ' o,:::'fifl"''"' " /1 15 f,l PP

A low-cost DMM using the ADD 3501 (National Semiconductor Data Acquisition Handbook)

~~H:

t:::)

<cl'

:::;:

~

-0

5·

C')

-s·

cn

"'

~

Q.

~

£

g.

::i

"'](https://image.slidesharecdn.com/unit-5digitalelectronics-230930120401-5bd199ba/85/unit-5-digital-electronics-pdf-33-320.jpg)