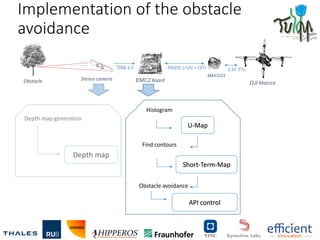

This project aims to develop ubiquitous low-power image processing platforms. It has several objectives including defining a reference platform, instantiating it through use cases, and demonstrating performance improvements. Several partners from industry and academia are involved. Key tasks include selecting hardware components, developing interfaces and tools, and validating the platform using applications like medical imaging, automotive driver assistance, and unmanned aerial vehicles. An initial hardware instance was selected using the Sundance EMC2 board with an ARM CPU and FPGA. The UAV use case involves real-time stereo depth estimation for obstacle avoidance.

![Tasks and WP2 objectives

Objectives:

1. The reference platform instantiation [based on the recommendations given in WP1 and coordinated with

WP3-WP5]

2. A holistic iterative development and optimization concept for low-power high-performance

image processing boards [taking into account results of WP3 - WP5].

Tasks:

T2.1 Components and parameters [M03 - M15] Leader: FHG / Participants: RUB, SUN, THL, NTNU, SYN

T2.2 Internal Components Interfaces [M06 to M12] Leader: FHG / Participants: SUN, THL, NTNU, SYN

T2.3 Development of Tulipp Platform [M12 - M34] Leader: SUN / Participants: FHG, THL, NTNU, SYN](https://image.slidesharecdn.com/tulippoverviewiosb-190301103127/85/TULIPP-overview-7-320.jpg)