Embed presentation

Download to read offline

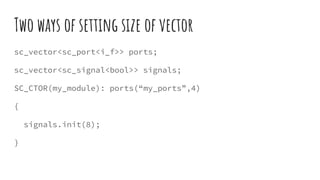

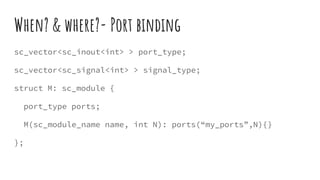

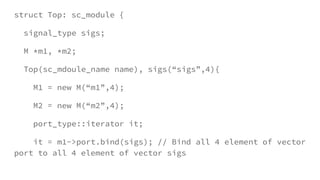

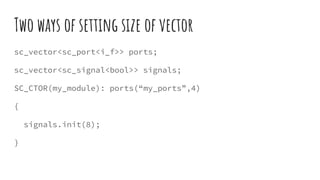

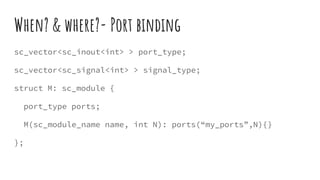

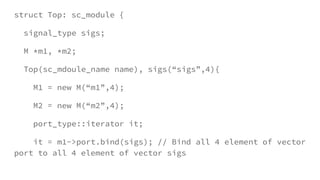

sc_vector is a SystemC class that allows users to create vectors of SystemC objects like ports, modules, and signals. It provides member functions for accessing elements in the vector and binding vector ports. The size of an sc_vector must be set during construction or with init() and cannot be dynamically resized. There are two ways to set the size - during construction like sc_vector<sc_port<i_f>> ports("my_ports",4) or later with init() like signals.init(8). Port binding can be done by iterating through an sc_vector of ports and binding it to a vector of signals.