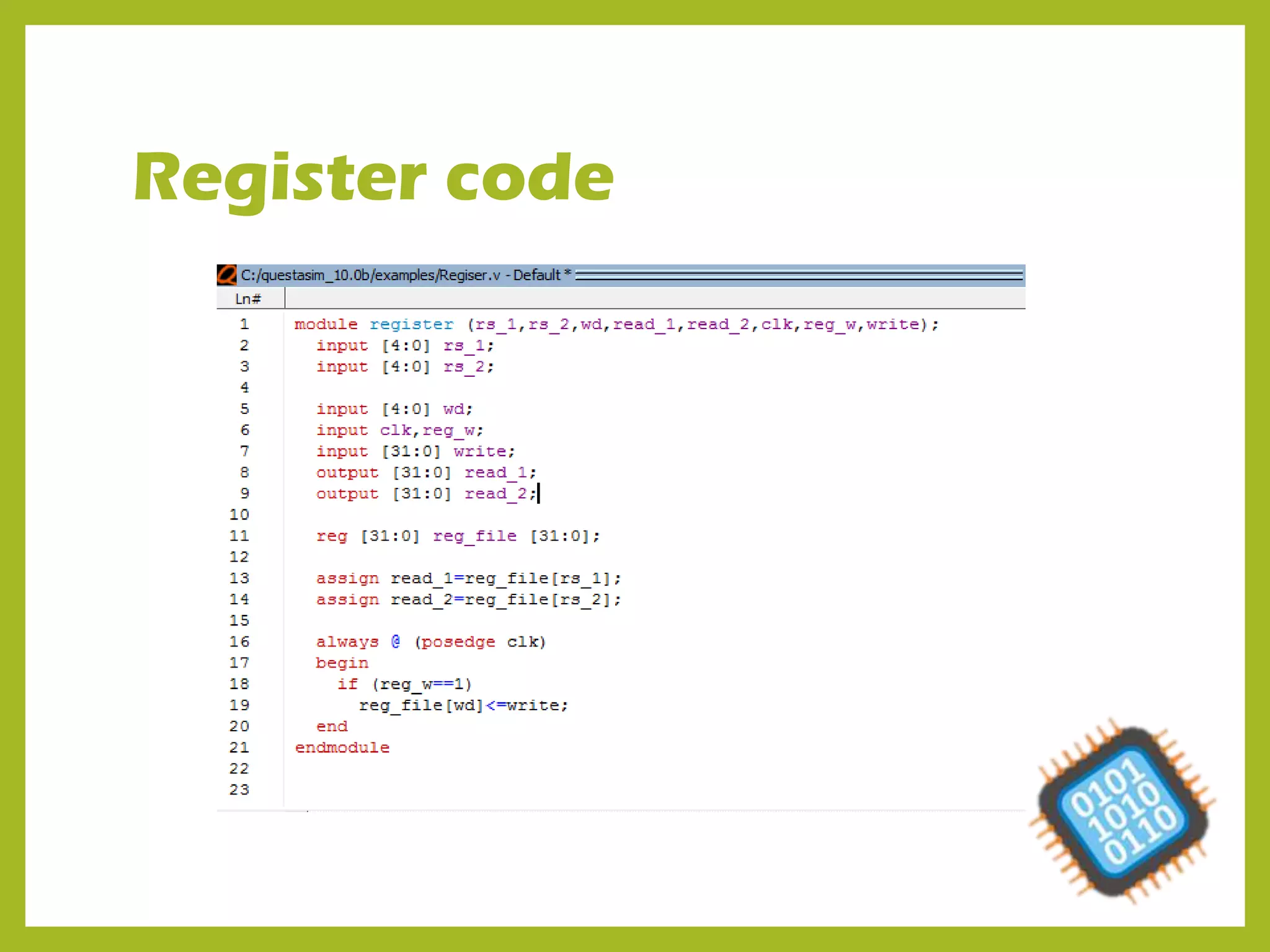

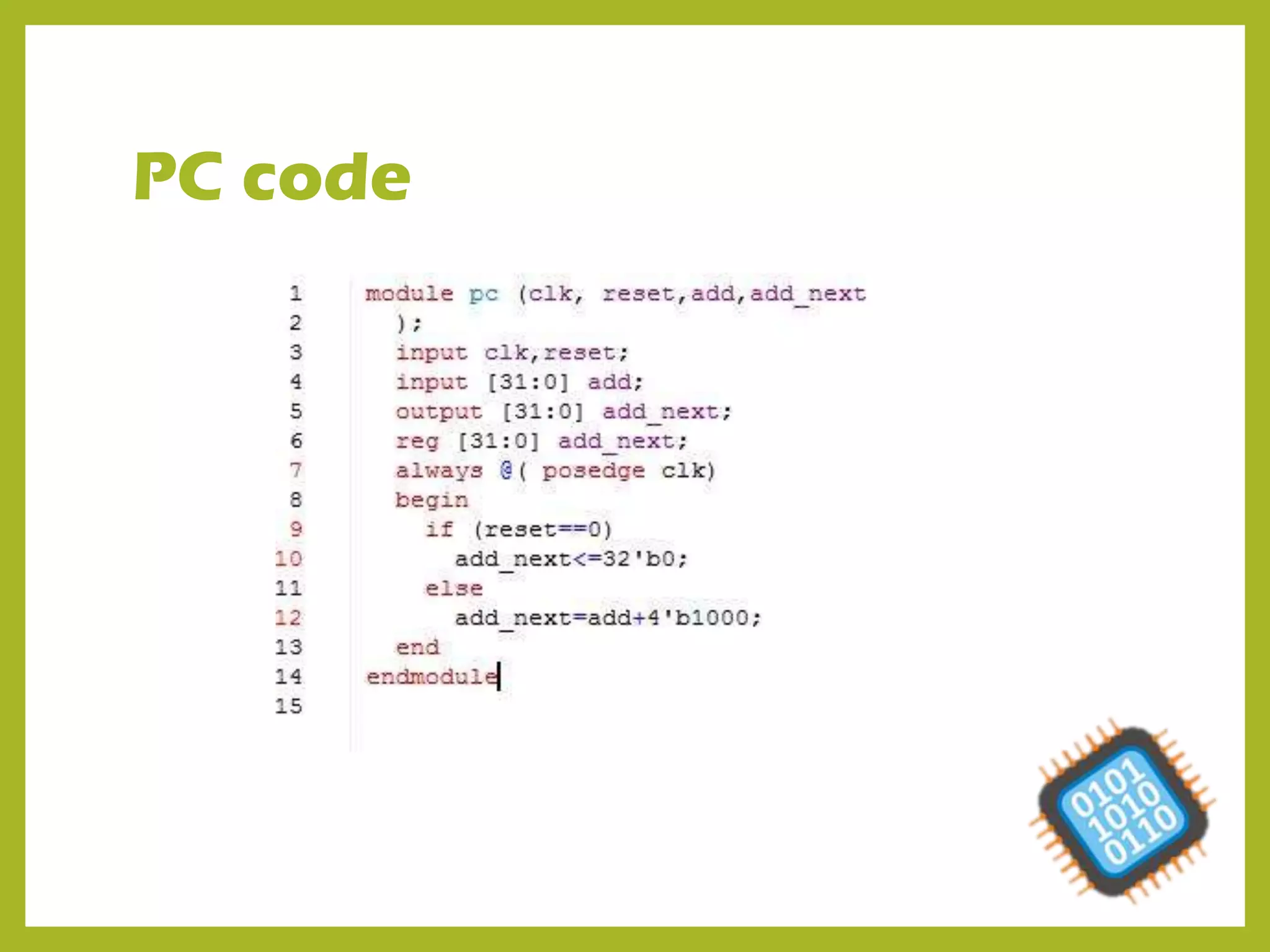

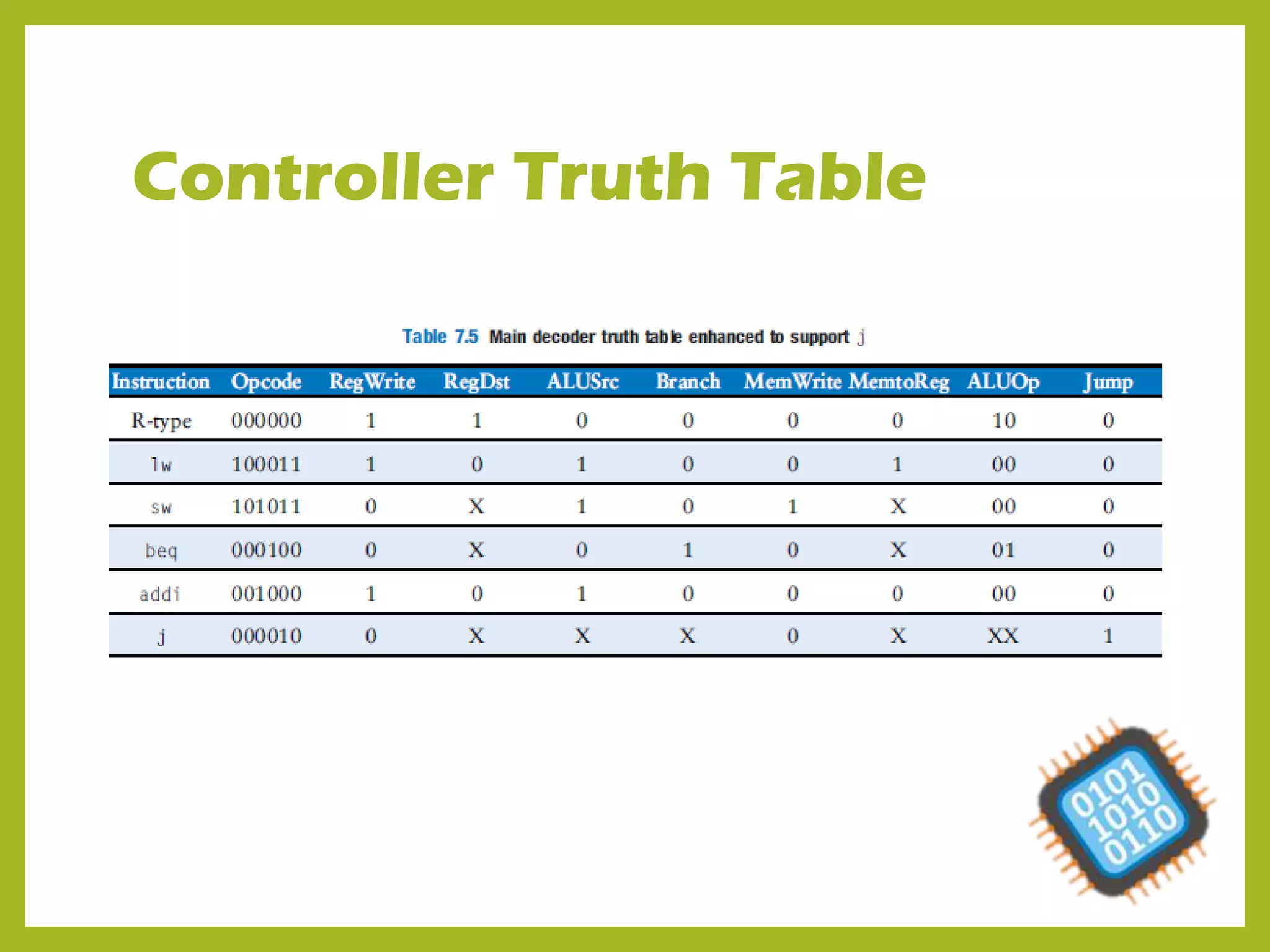

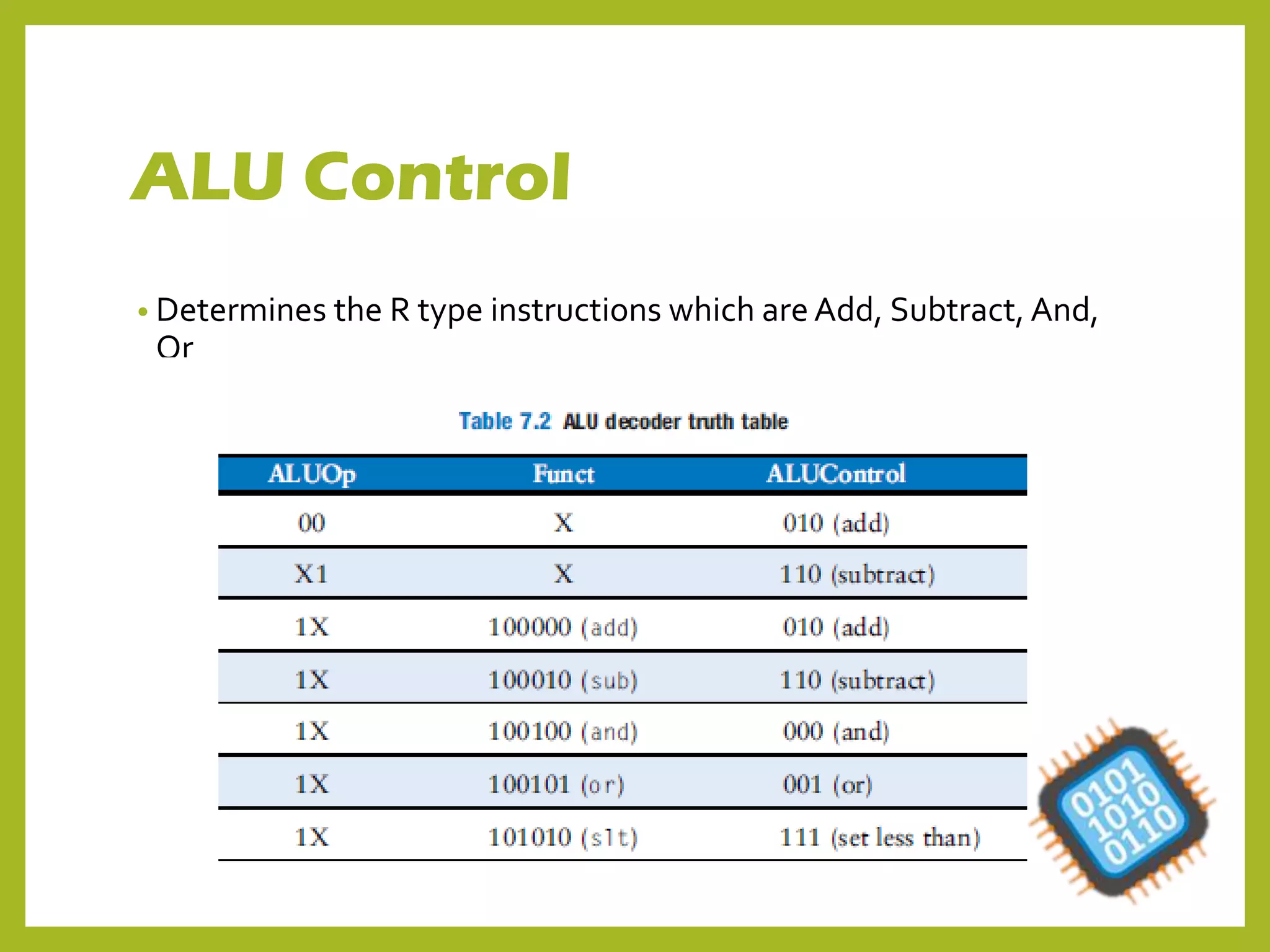

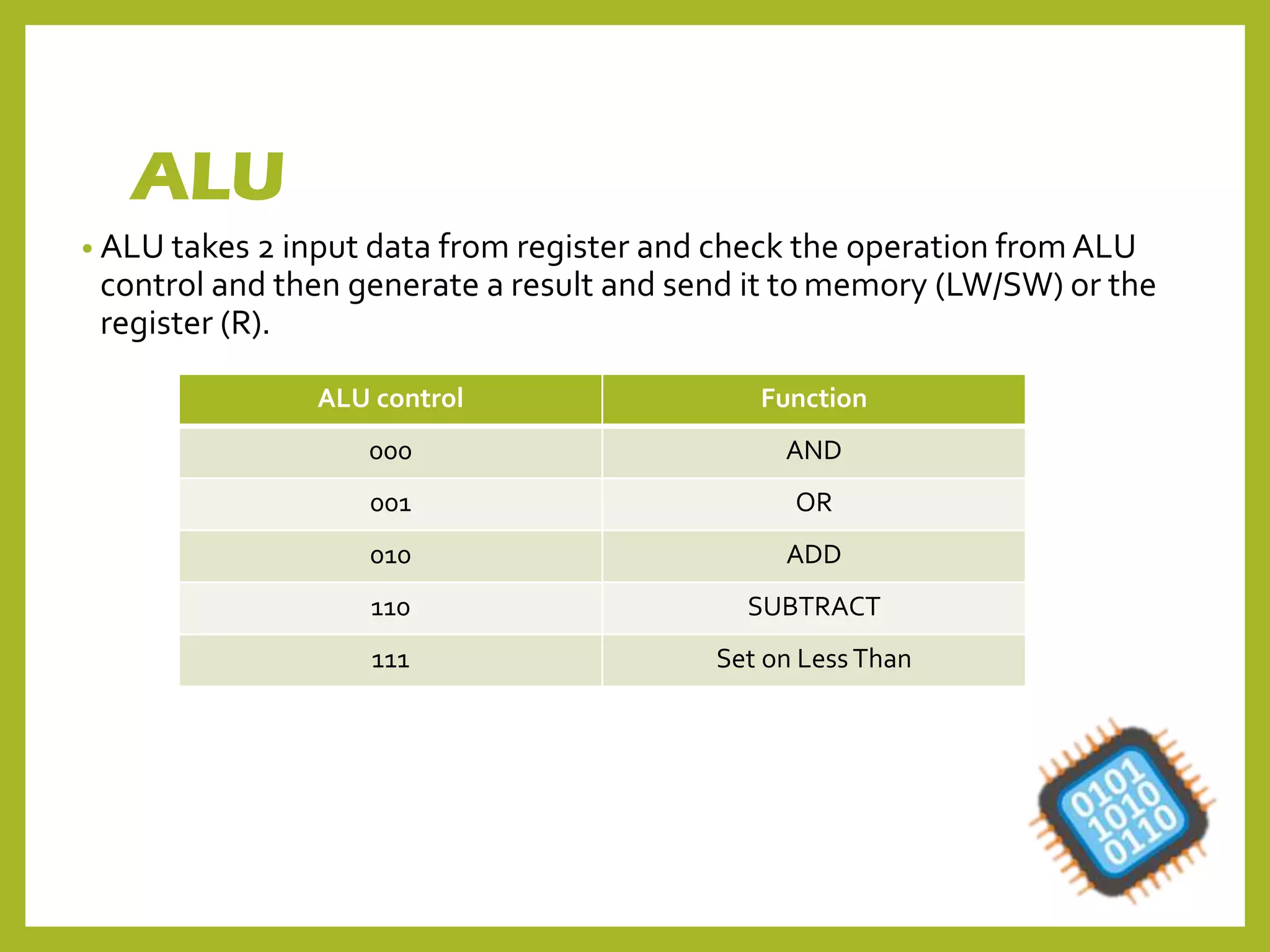

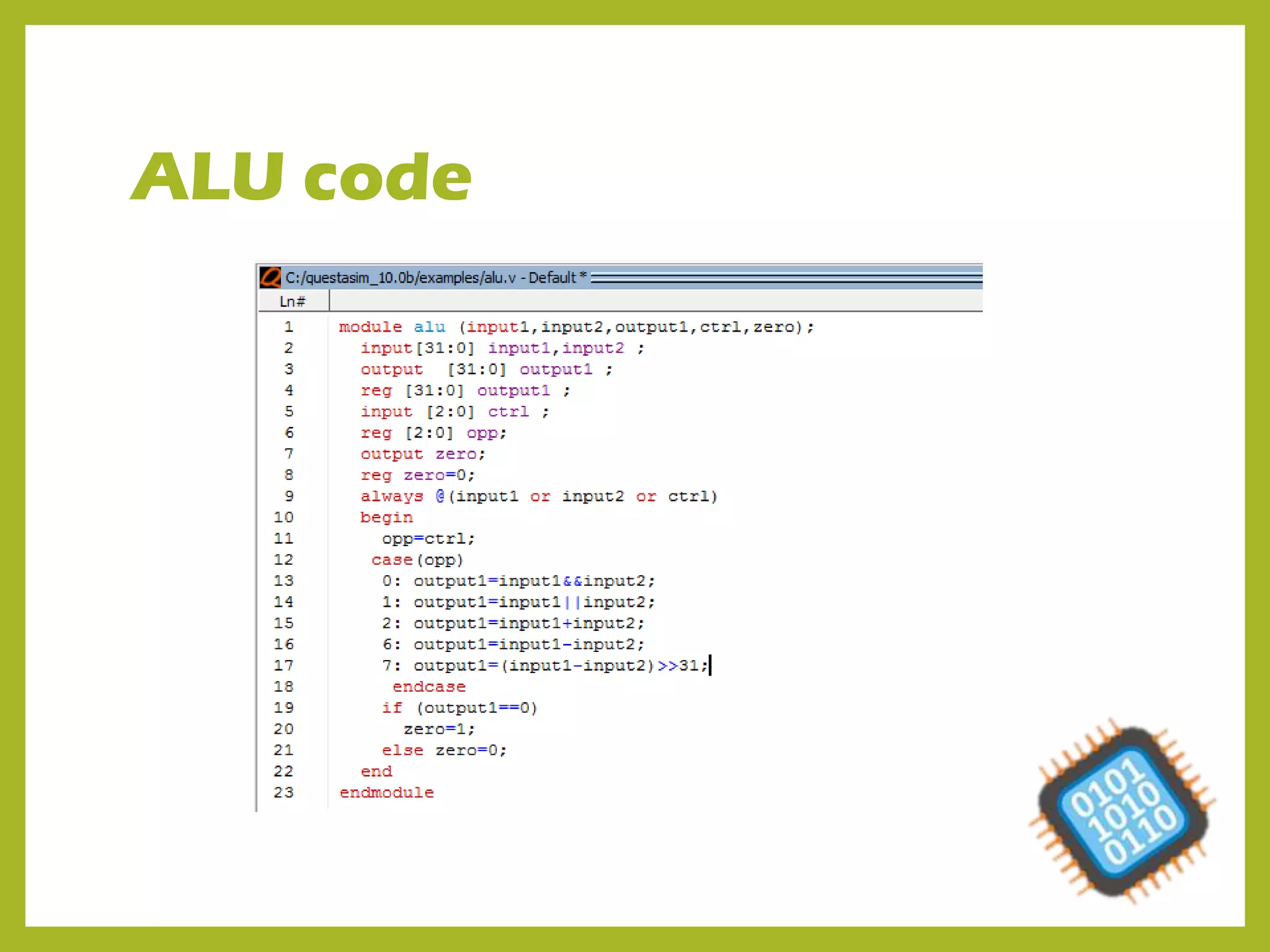

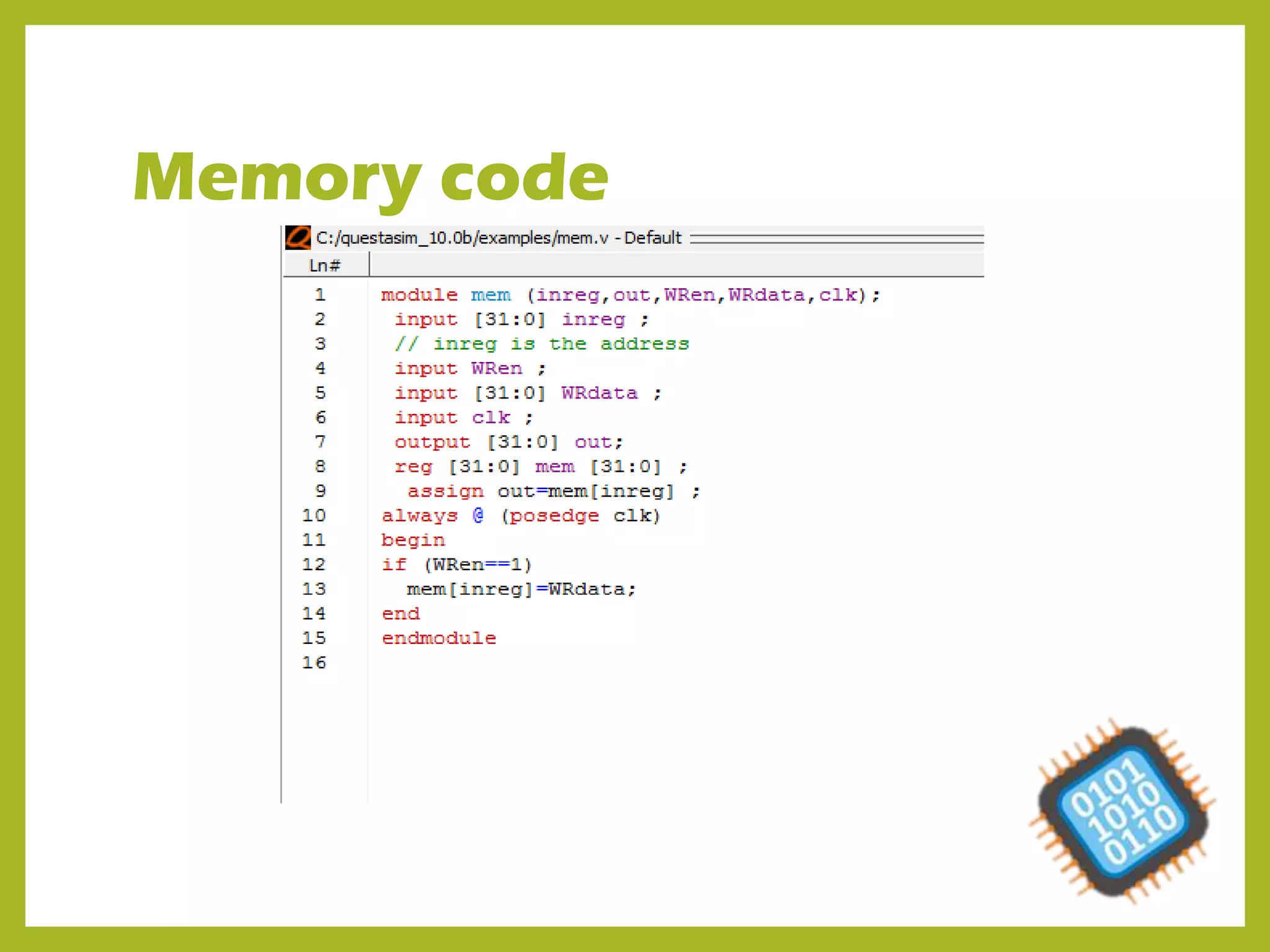

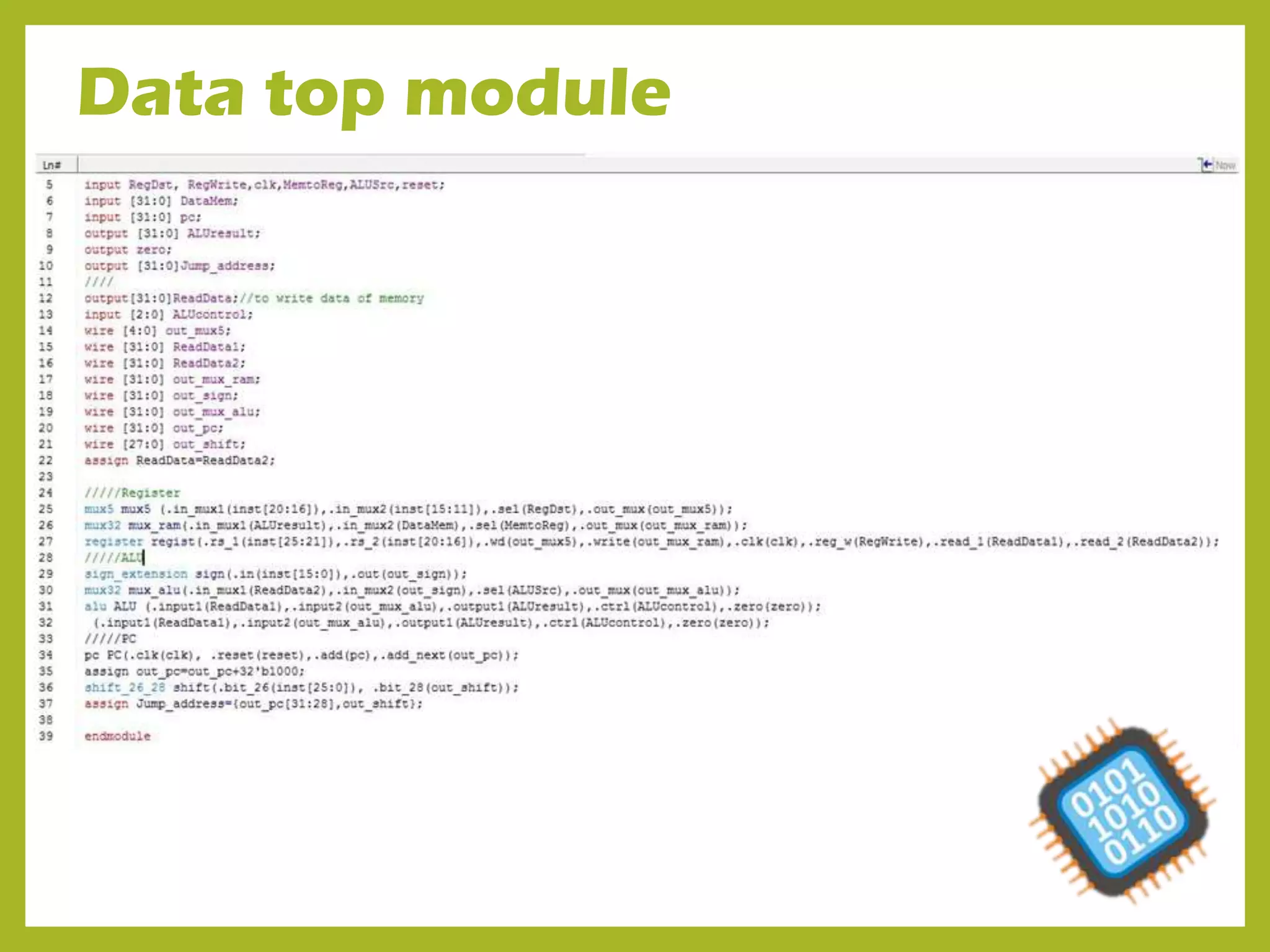

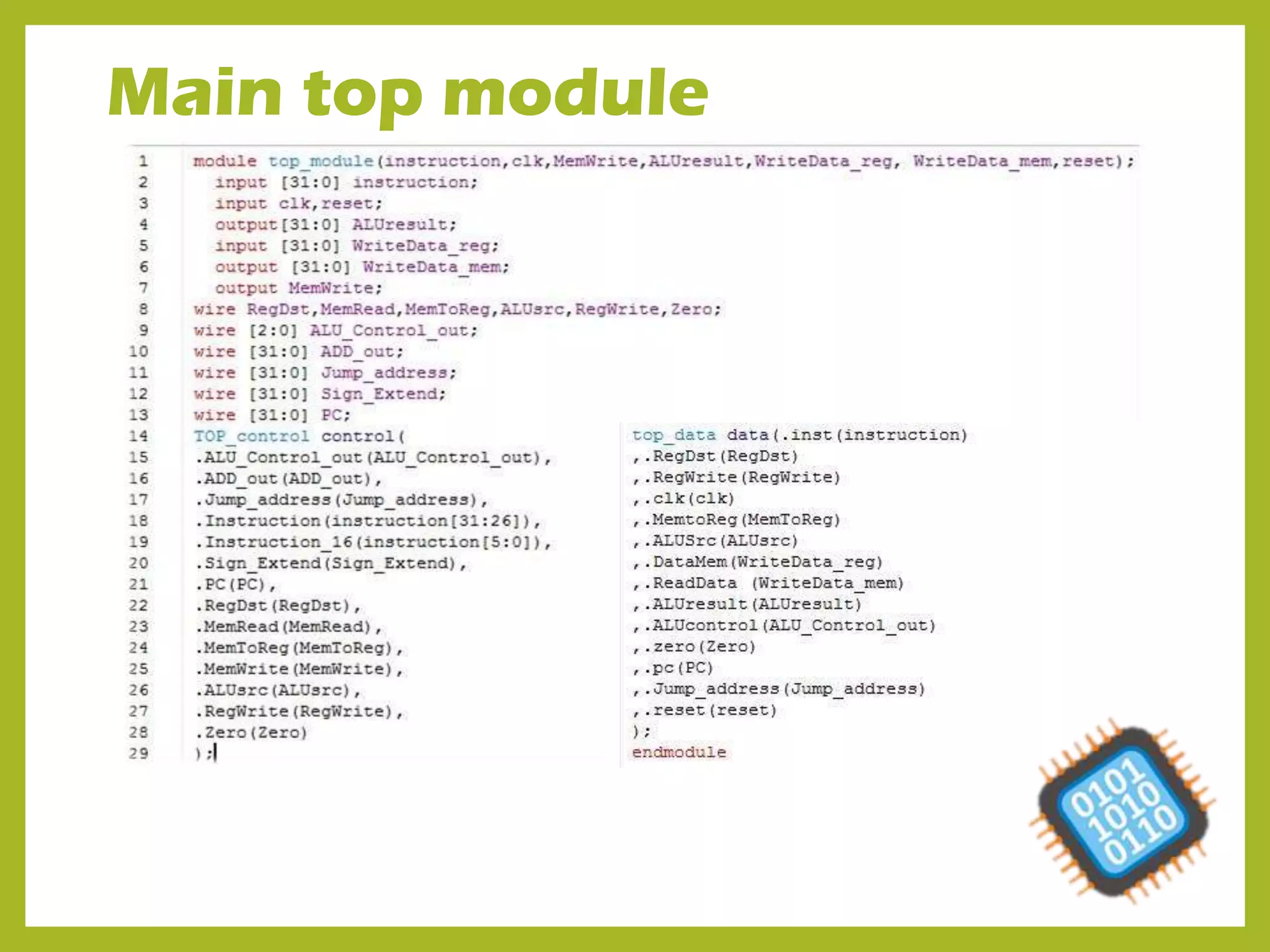

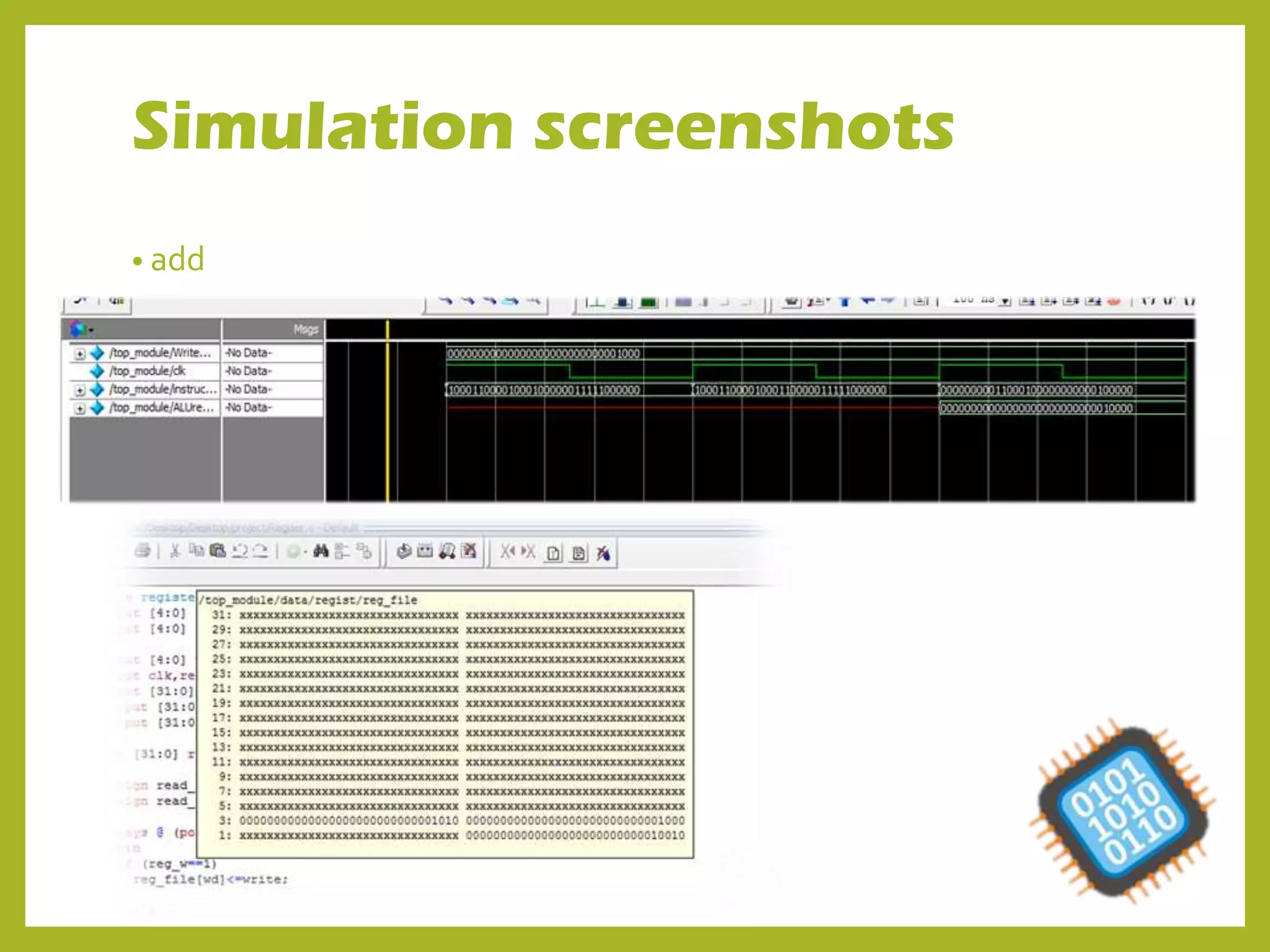

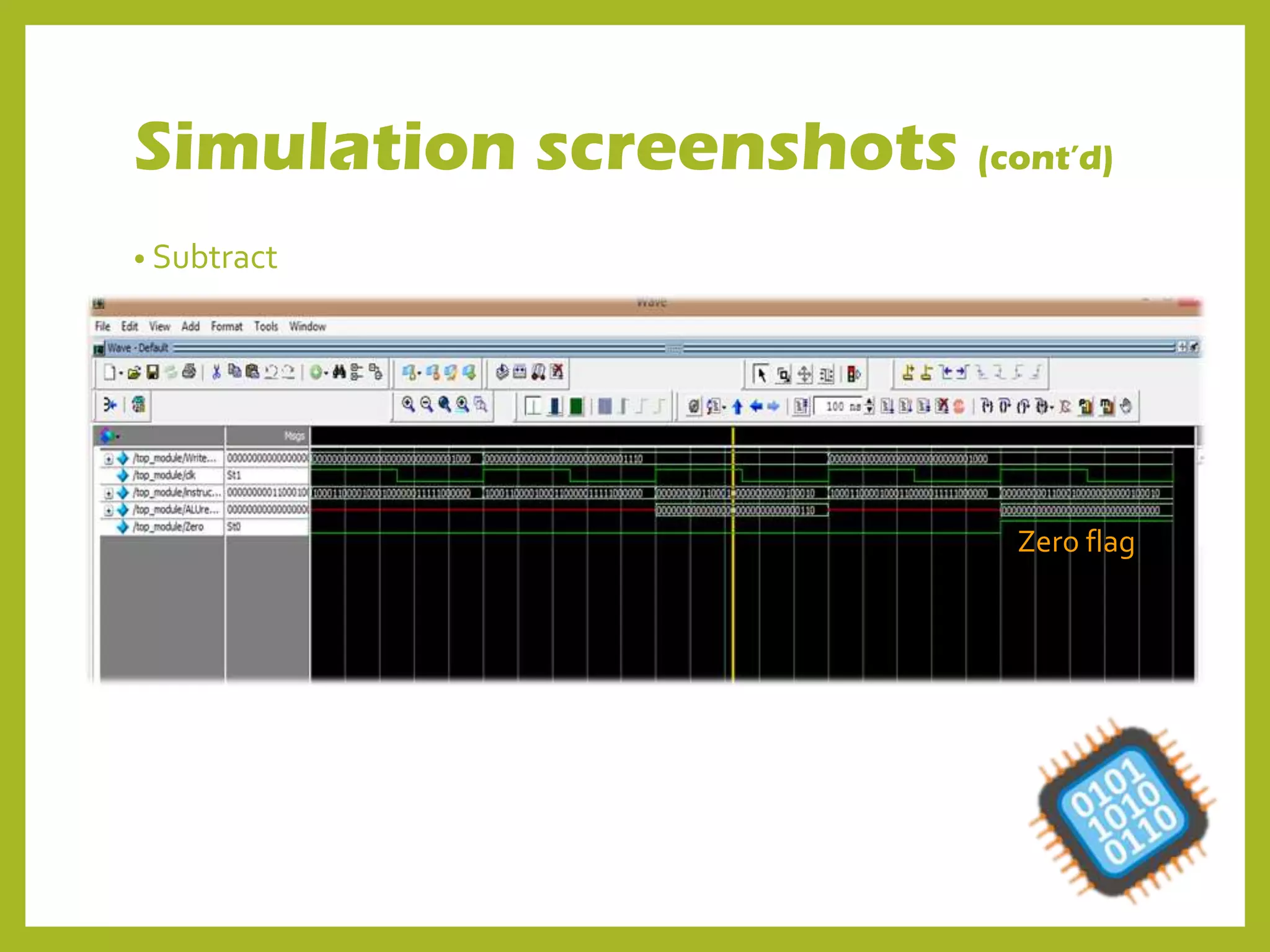

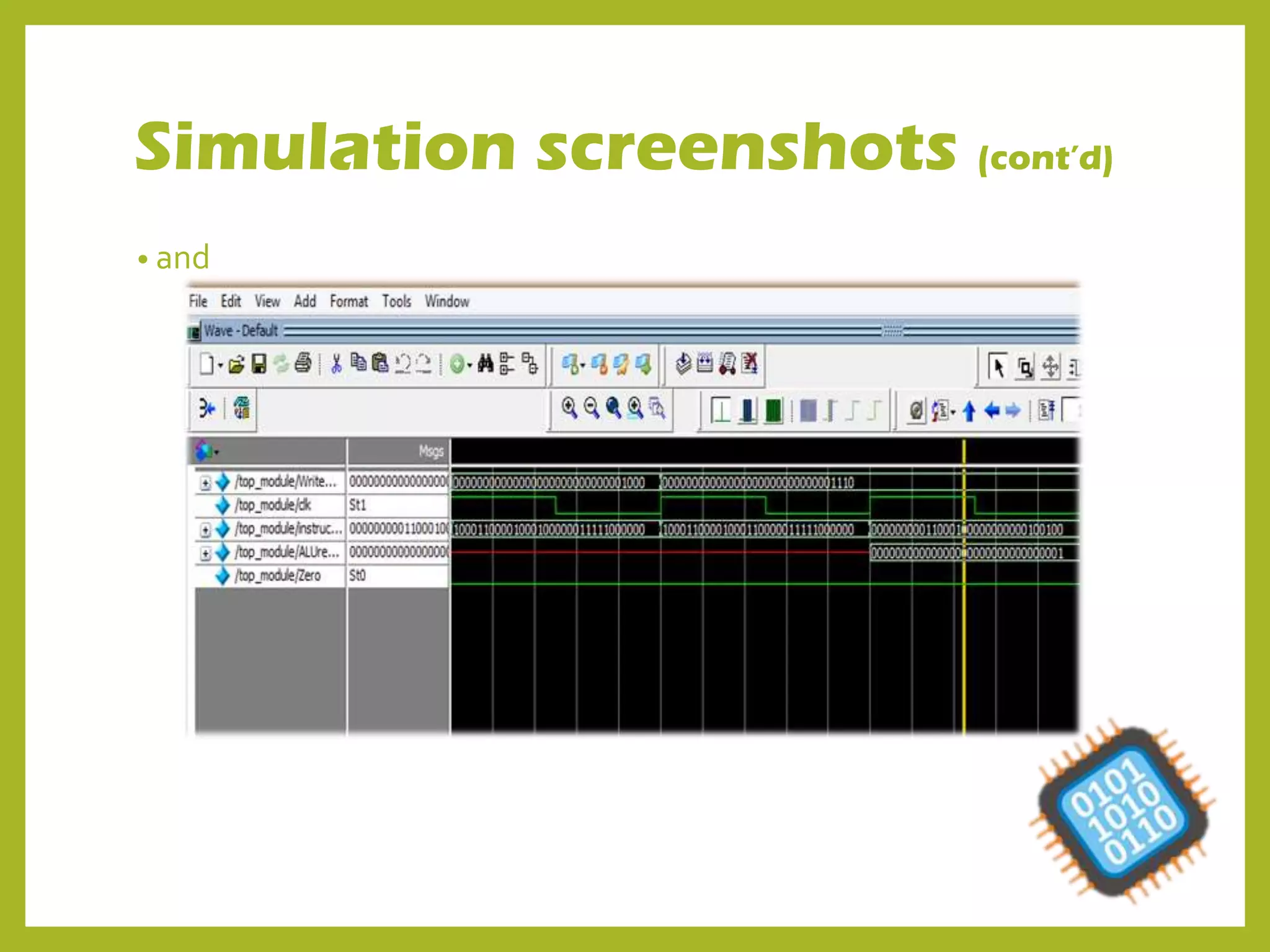

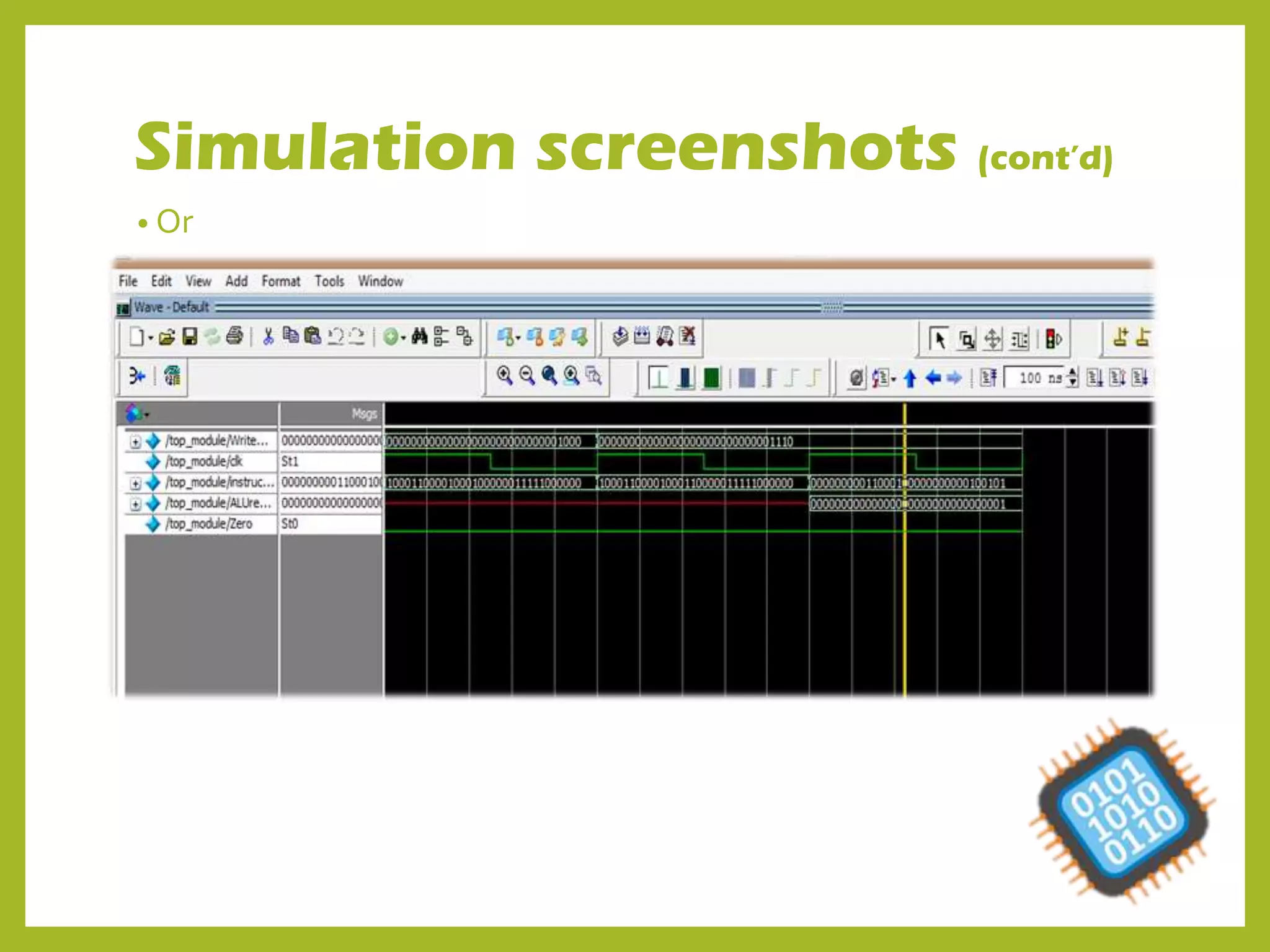

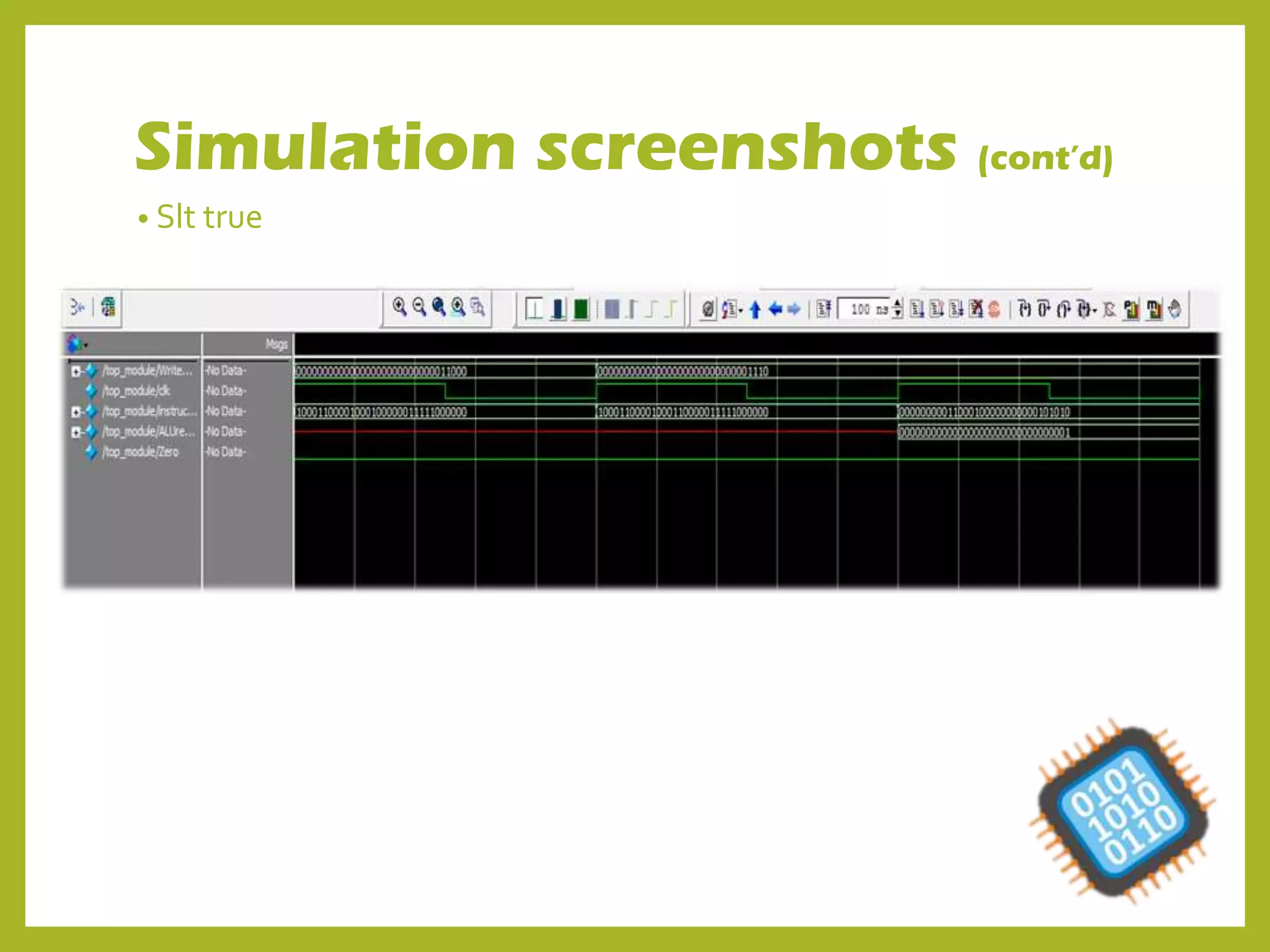

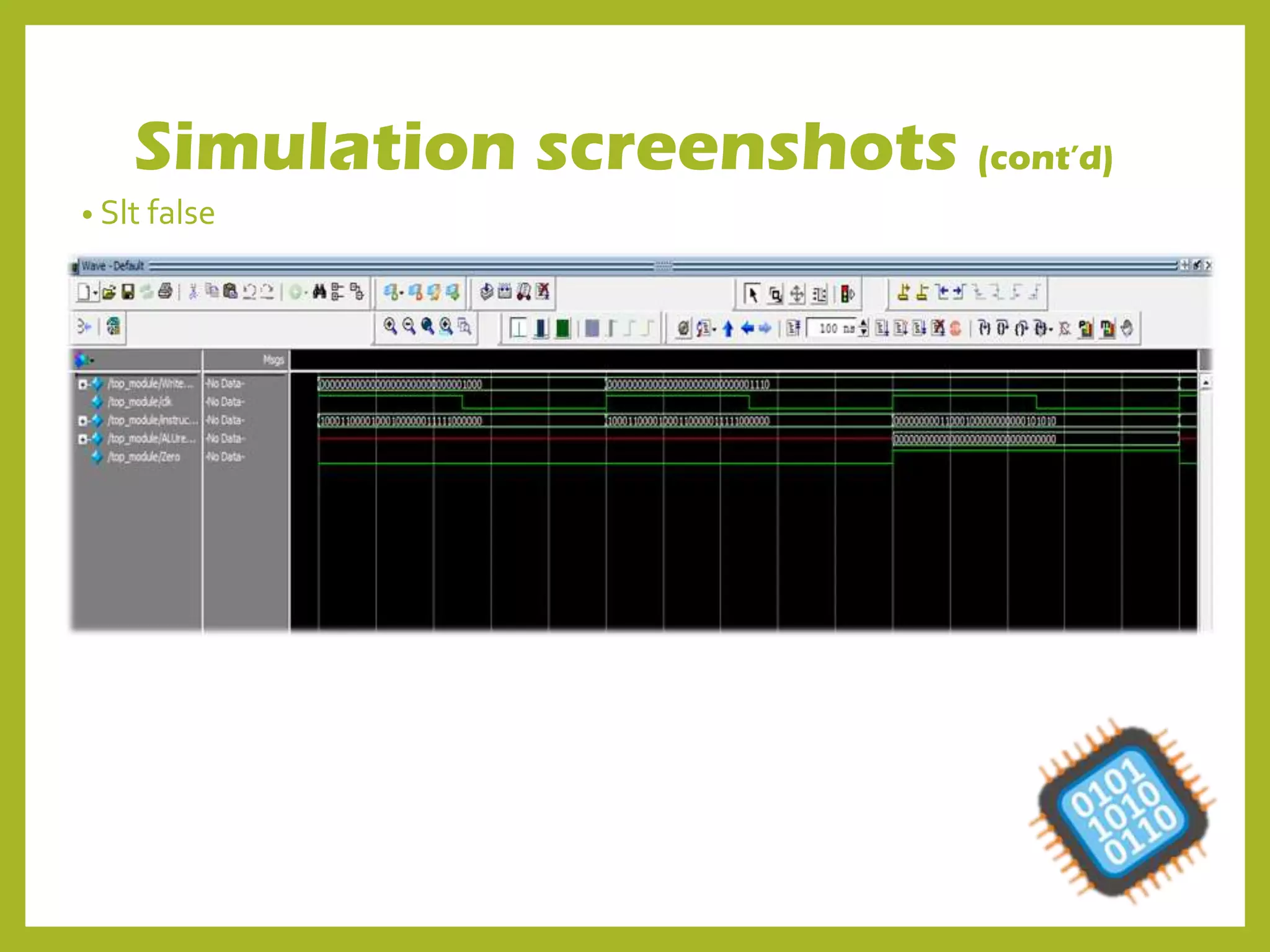

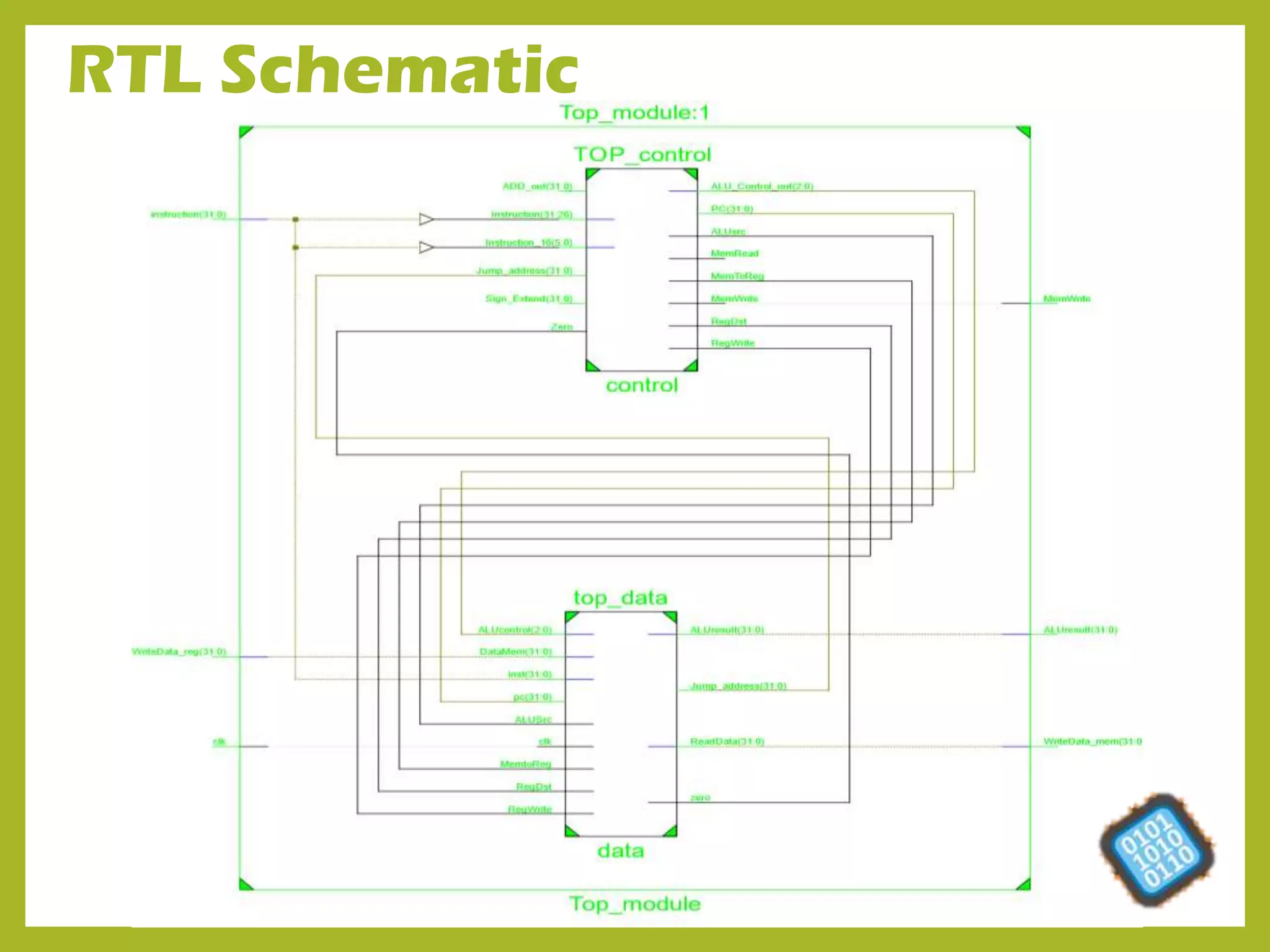

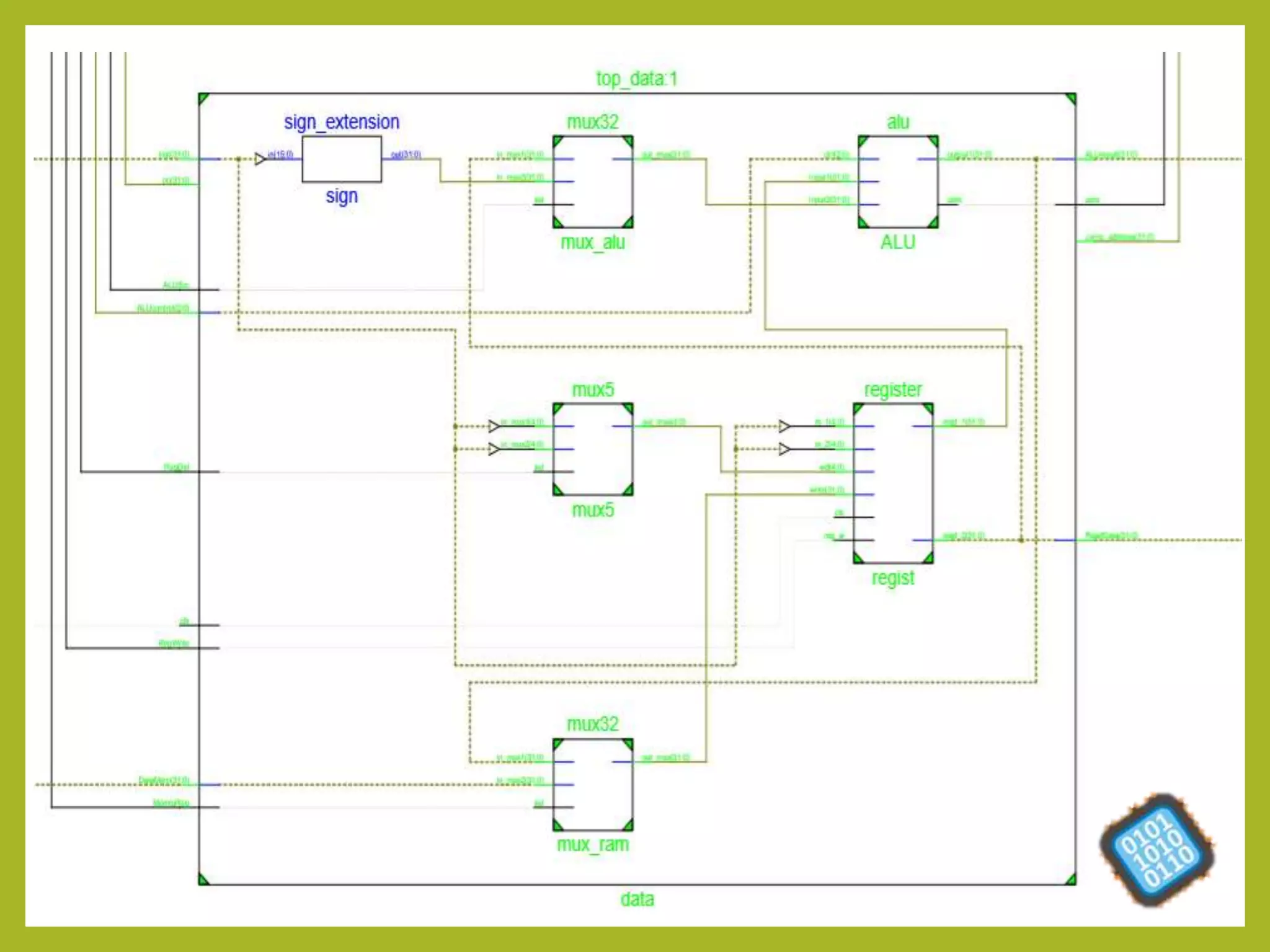

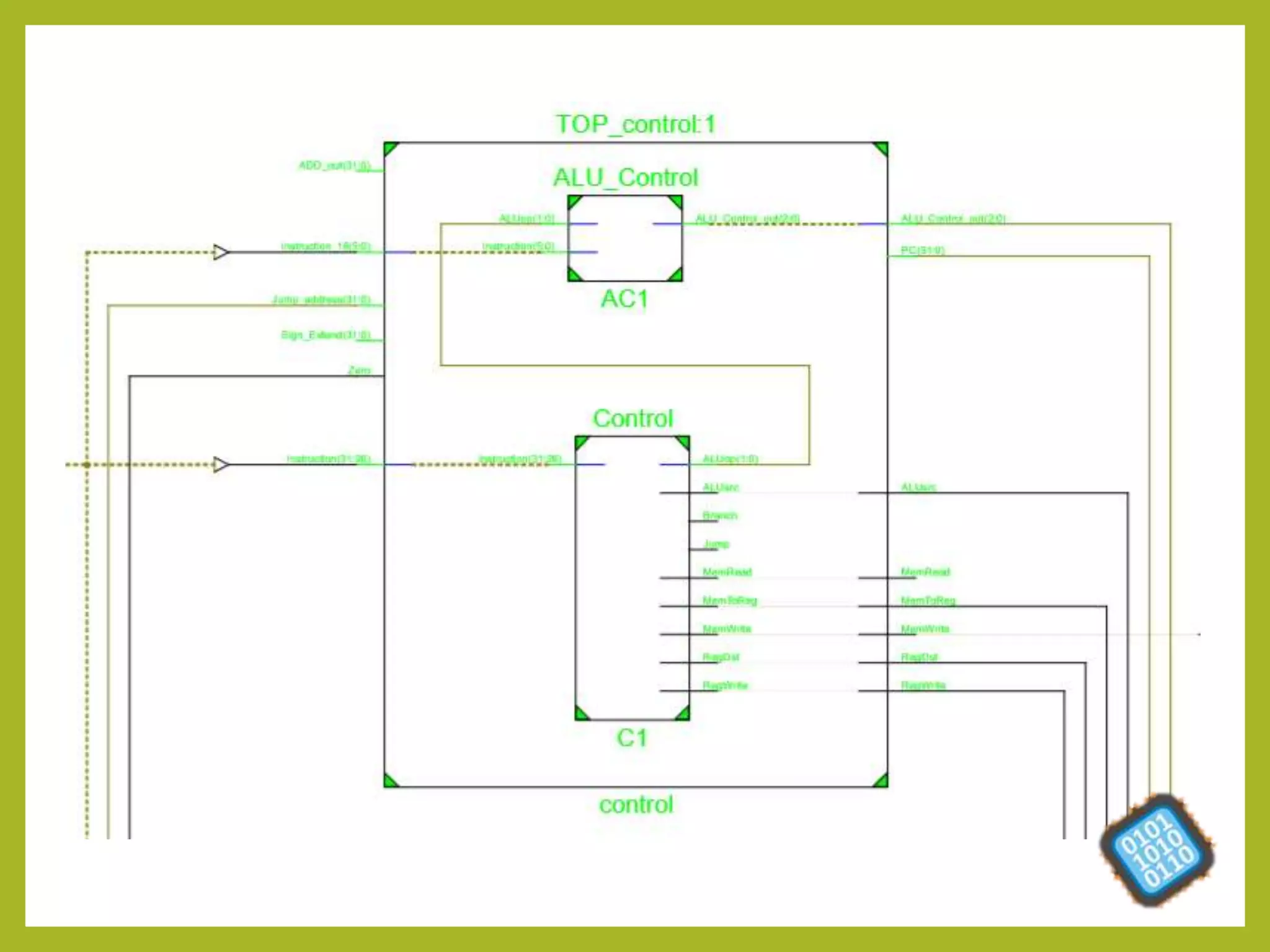

This document describes a single cycle processor implemented in Verilog that executes instructions in one clock cycle. It includes a register file to store data, an program counter (PC) to track the next instruction address, a controller to decode instructions and control operations, an arithmetic logic unit (ALU) to perform arithmetic and logical operations on data, and a memory to store and retrieve data. The processor supports load, store, add, and, or, subtract, set on less than, and branch equal instructions operating on 32-bit data words through its register ports, ALU, and memory components controlled by the single cycle controller.