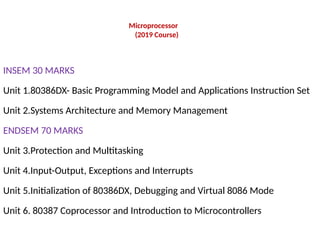

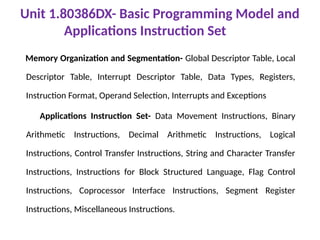

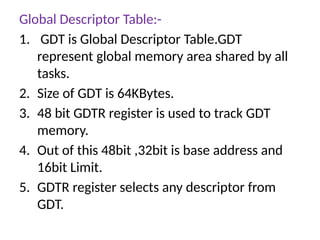

The document outlines the syllabus for a microprocessor course at S. B. Patil College of Engineering, covering key topics such as the 80386DX architecture, programming models, memory management, multitasking, I/O systems, and microcontrollers. It details various units including instruction sets, protection mechanisms, initialization, debugging, and coprocessor integration. Additionally, it highlights the differences between microprocessors and microcontrollers along with their applications.