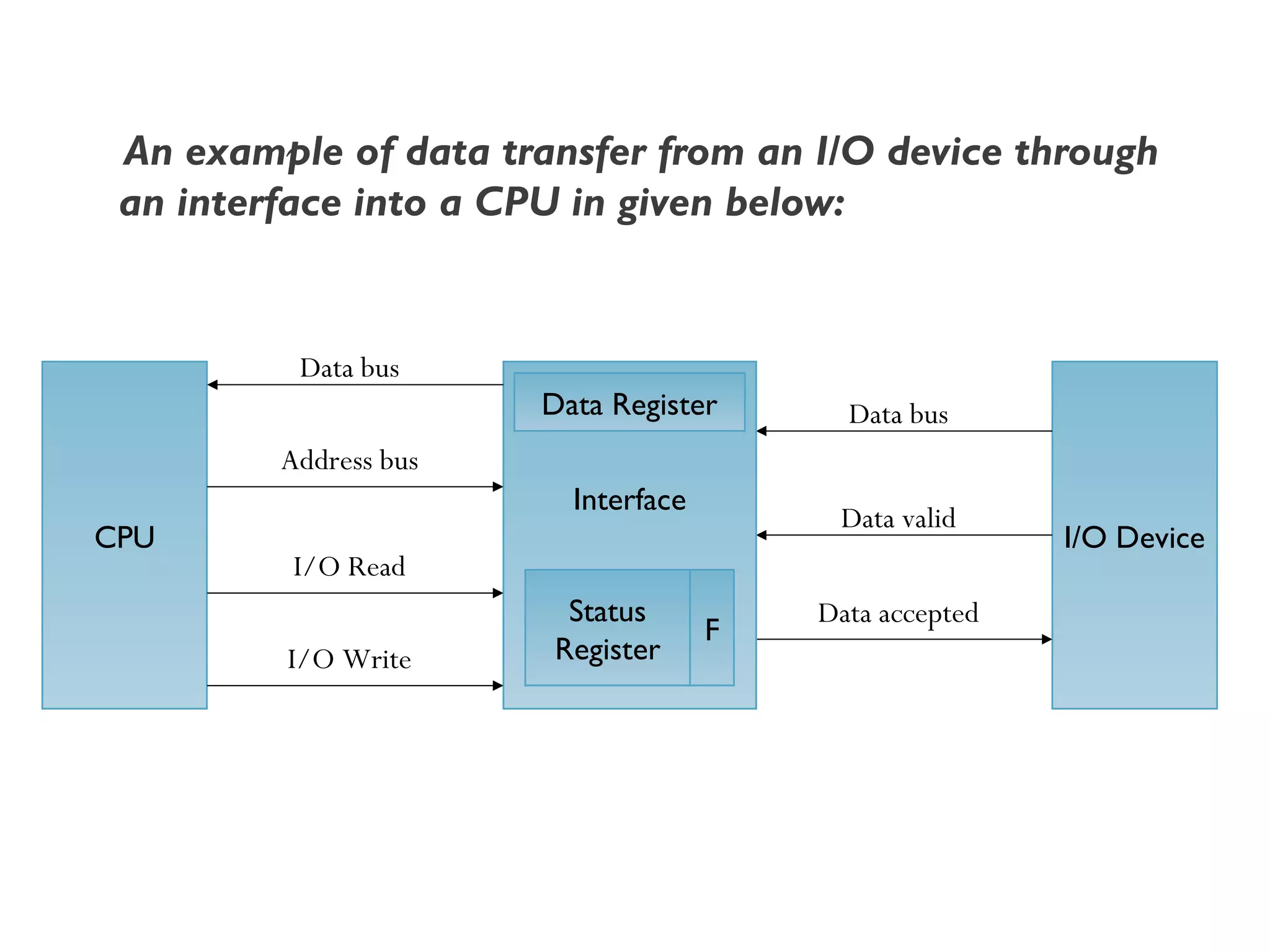

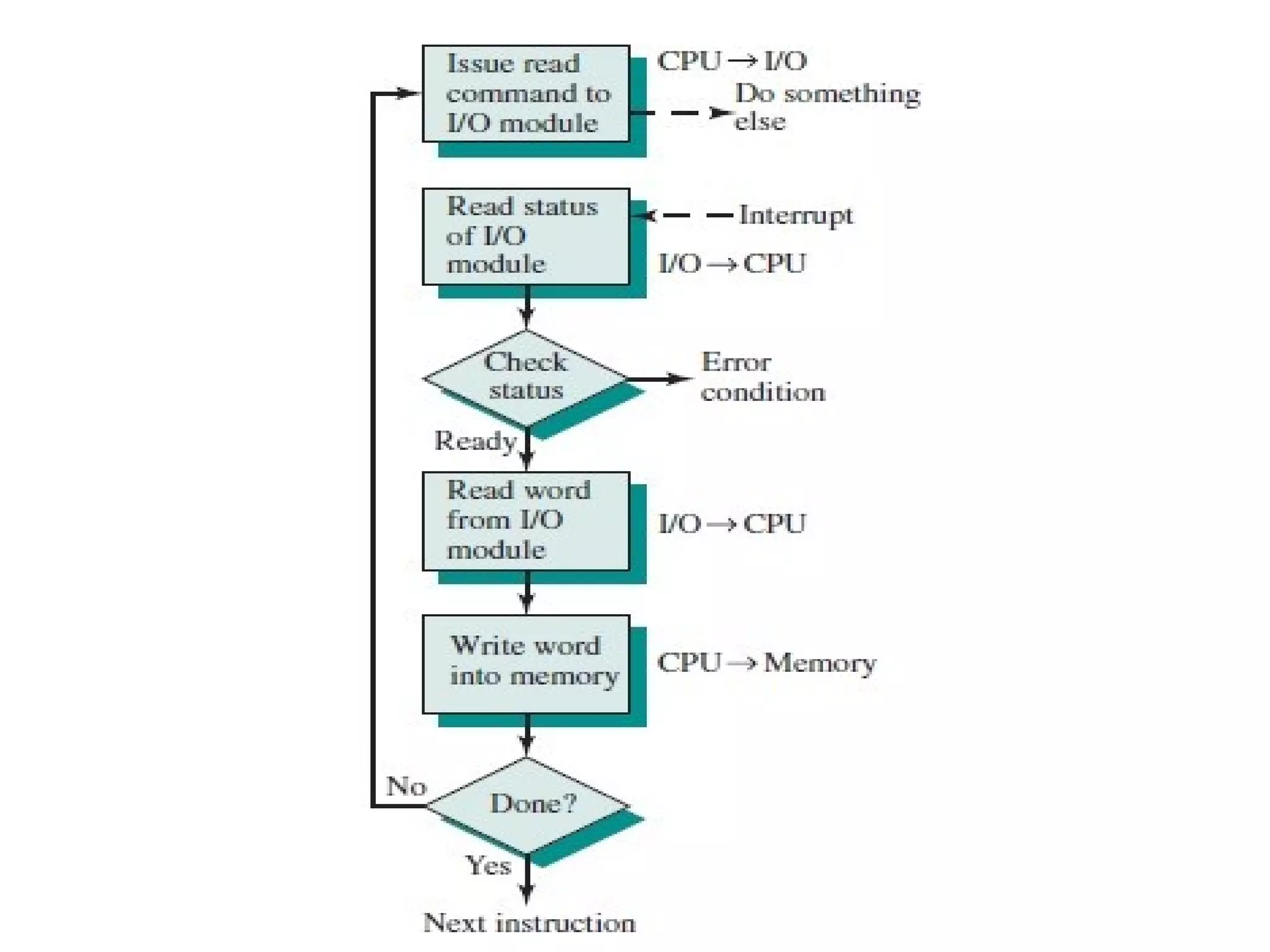

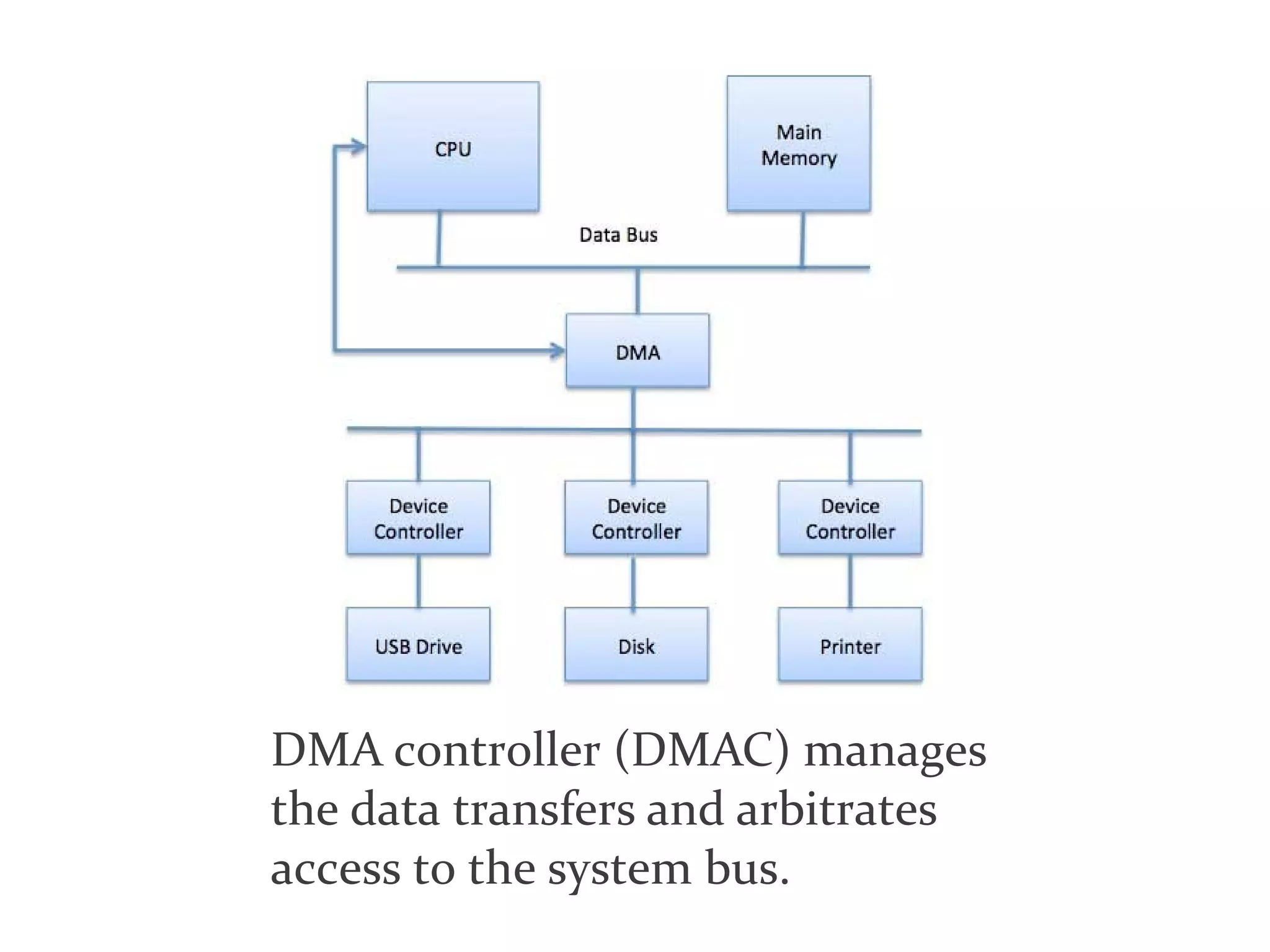

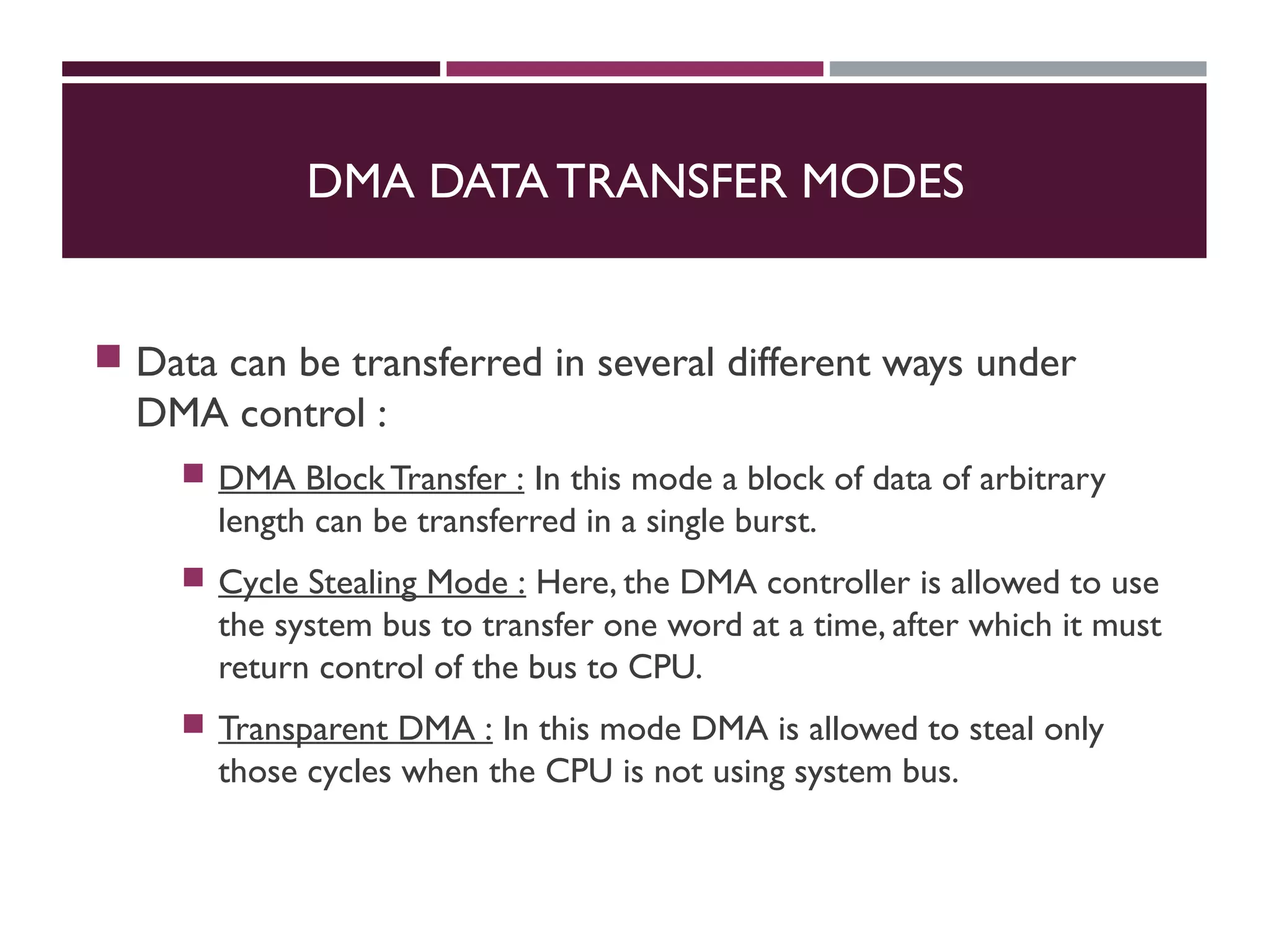

This document discusses different modes of data transfer between I/O devices and memory in a computer system. It describes three main modes: programmed I/O, interrupt-initiated I/O, and direct memory access (DMA). Programmed I/O involves constant CPU monitoring during transfers. Interrupt-initiated I/O uses interrupts to notify the CPU when a transfer is ready. DMA allows I/O devices to access memory directly without CPU involvement for improved efficiency.