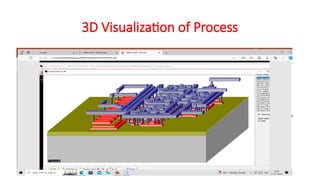

Microwind is a digital schematic circuit design and simulation software popular among VLSI circuit designers, supporting various tools such as DSCH for digital circuit design and simulation, and NanoLambda for precision CMOS layout. It focuses on advanced semiconductor technology, particularly the nanometer scale, enhancing transistor density and energy efficiency while adhering to Moore's Law. The document also discusses technology scaling advantages and disadvantages, detailing the design flow, tools, and various analysis features available in Microwind for circuit optimization.