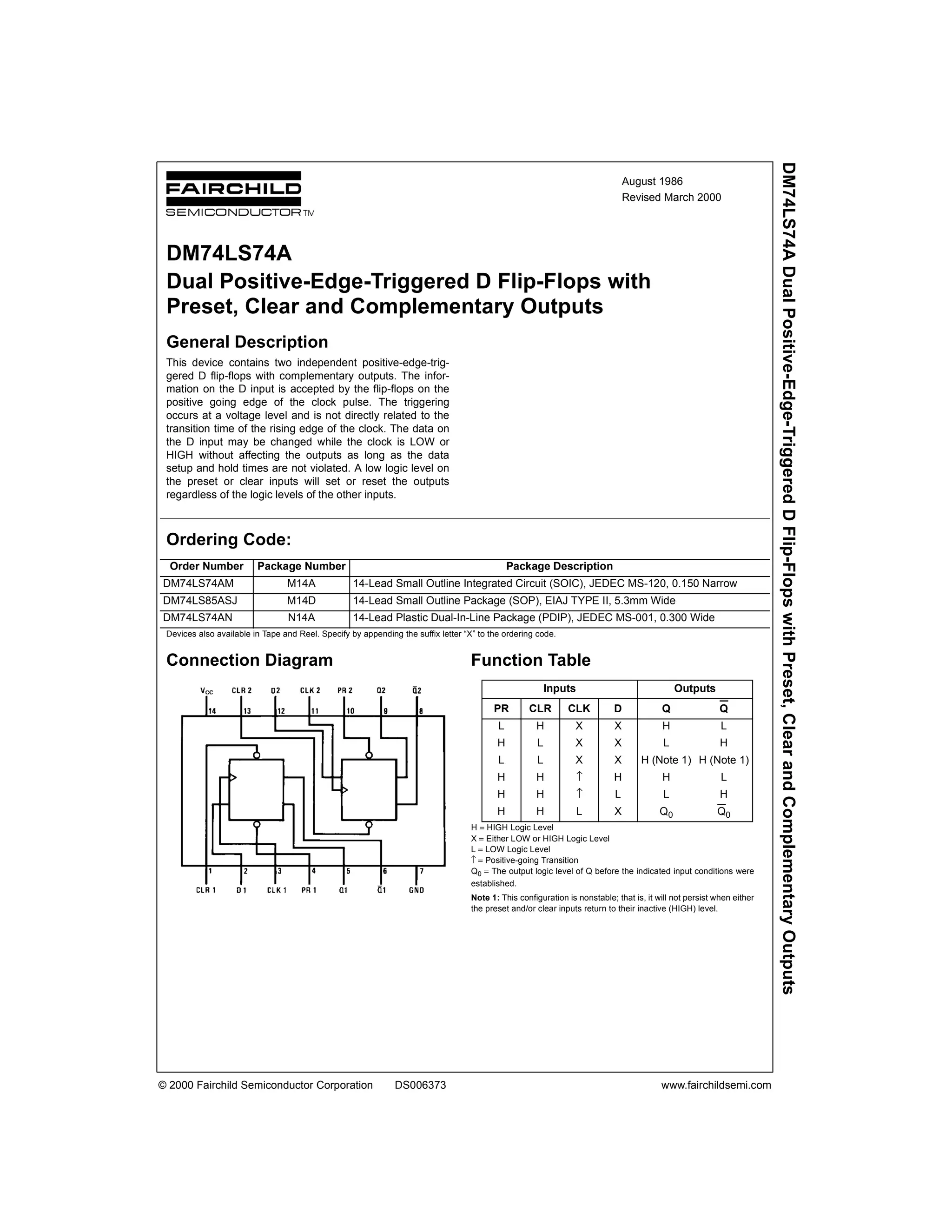

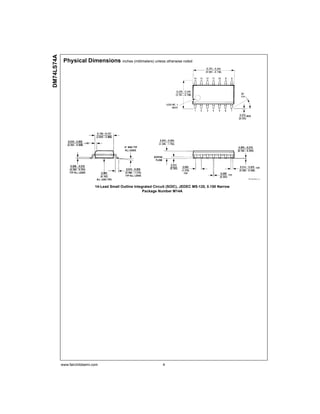

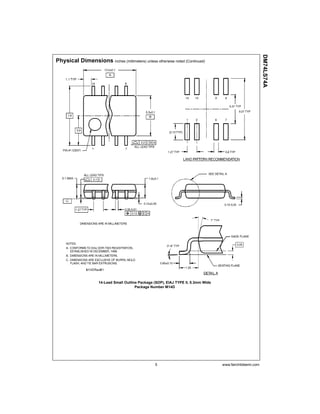

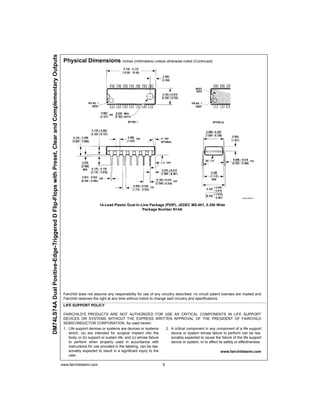

This document describes the DM74LS74A dual positive-edge triggered D flip-flop integrated circuit. It contains two independent D flip-flops that accept input on the positive edge of the clock signal. Each flip-flop has preset and clear inputs to force the outputs, and complementary Q and Q-bar outputs. The document provides pinout diagrams, truth tables, electrical specifications, and packaging/dimension information.