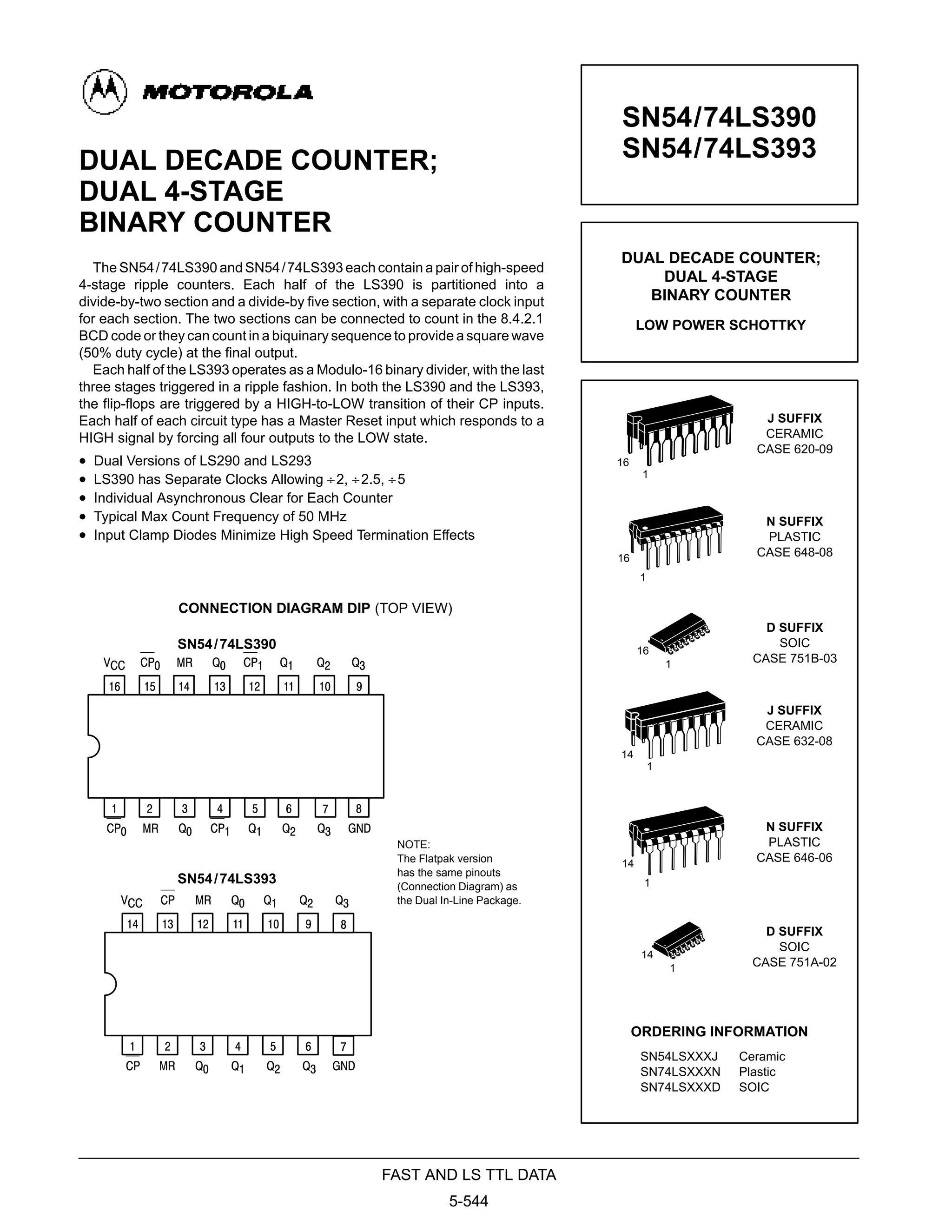

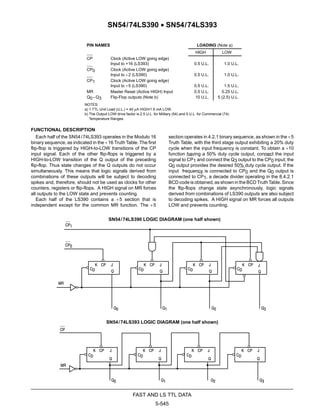

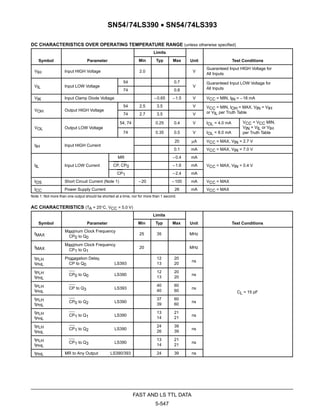

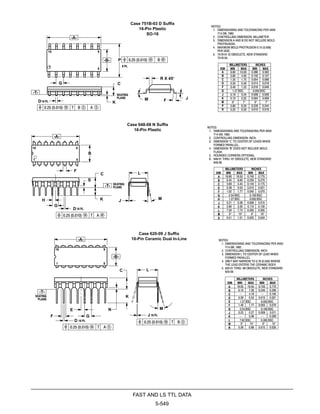

The document provides information on the SN54/74LS390 and SN54/74LS393 dual decade counter and dual 4-stage binary counter integrated circuits. It describes the operation and connections of each chip, including truth tables showing the output patterns. Specifications such as pin names and numbers, electrical characteristics, and packaging/ordering details are also included.