Logic gate

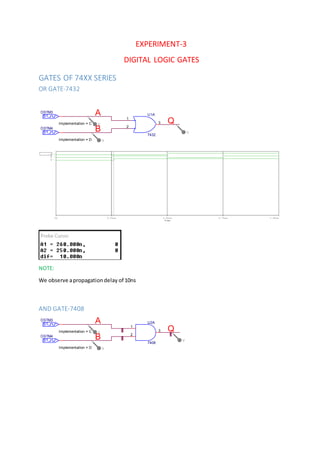

- 1. EXPERIMENT-3 DIGITAL LOGIC GATES GATES OF 74XX SERIES OR GATE-7432 NOTE: We observe apropagationdelay of 10ns AND GATE-7408 Q S1 DSTM3 Implementation = C V V U1A 7432 1 2 3 A S1 DSTM4 Implementation = D B V TimeTime 0s 0.25us 0.50us 0.75us 1.00us A B Q 0 1 1 U2A 7408 1 2 3 S1 DSTM4 Implementation = D 0 0 V V A Q B V S1 DSTM3 Implementation = C 0

- 2. NOTE: We observe 2propagationdelays 1) High-to-LowPropagationDelayTphl 2) Low-to-HighPropagationDelay Tplh So average propagationdelay - tp = (Tphl + Tplh)/2 NAND GATE-7400 TimeTime 0s 0.5us 1.0us 1.5us 2.0us A B Q 1 1 1

- 3. Tphl = 6.34 ns Tplh = 11.11 ns TimeTime 0s 0.25us 0.50us 0.75us 1.00us 1.25us 1.50us 1.75us 2.00us A B Q 1 1 0 TimeTime 0s 0.25us 0.50us 0.75us 1.00us 1.25us 1.50us 1.75us 2.00us A B Q 0 0 1

- 4. NOT GATE-7404 Tphl = 7.94 ns Tplh= 12.69 ns TimeTime 0s 0.5us 1.0us 1.5us 2.0us A Q 1 1 TimeTime 0s 0.5us 1.0us 1.5us 2.0us A Q 0 1

- 5. VARIOUS GATES USING UNIVERSAL NAND GATE: NOT GATE USING NAND GATE: AND GATE USING NAND GATE: TimeTime 0s 0.5us 1.0us 1.5us 2.0us A Q

- 6. OR GATE USING NAND GATE: TimeTime 0s 0.25us 0.50us 0.75us 1.00us 1.25us 1.50us 1.75us 2.00us A B Q TimeTime 0s 0.25us 0.50us 0.75us 1.00us 1.25us 1.50us 1.75us 2.00us A B Q

- 7. NOR GATE USING NAND GATE: Ex-OR GATE USING NAND GATE: TimeTime 0s 0.25us 0.50us 0.75us 1.00us 1.25us 1.50us 1.75us 2.00us A B Q

- 8. VARIOUS GATES USING UNIVERSAL NOR GATE: NOT GATE USING NOR GATE: TimeTime 0s 0.25us 0.50us 0.75us 1.00us 1.25us 1.50us 1.75us 2.00us A B Q

- 9. AND GATE USING NOR GATE: TimeTime 0s 0.25us 0.50us 0.75us 1.00us 1.25us 1.50us 1.75us 2.00us A Q TimeTime 0s 0.25us 0.50us 0.75us 1.00us 1.25us 1.50us 1.75us 2.00us A B Q

- 10. OR GATE USING NOR GATE: NAND GATE USING NOR GATE: TimeTime 0s 0.25us 0.50us 0.75us 1.00us 1.25us 1.50us 1.75us 2.00us A B Q

- 11. Ex-OR GATE USING NOR GATE: TimeTime 0s 0.25us 0.50us 0.75us 1.00us 1.25us 1.50us 1.75us 2.00us A B Q TimeTime 0s 0.25us 0.50us 0.75us 1.00us 1.25us 1.50us 1.75us 2.00us A B Q

- 12. APPLICATION: HALF ADDER USING NAND GATE: HALF ADDER USING NOR GATE: TimeTime 0s 0.25us 0.50us 0.75us 1.00us 1.25us 1.50us 1.75us 2.00us A B s c

- 13. DISCUSSION: 1. WHY CALLED HALF ADDER? 2. DIFFERENCE BETWEEN HALF ADDER USING NANDGATE ANDNOR GATE? 3. IS THERE ANY SPECIFICRELATION BETWEEN Tphl ANDTplh ? 4. NAME OF UNIVERSALGATES? 5. WHAT ISTTL LOGIC? 6. TABULATION ANDCOMPARATIVESTUDY OF VARIOUSGATES? 7. HOW TO SELECT LOGIC GATES FORYOUR APPLICATION? CONCLUSION: IC INFORMATION: IC NUMBER DESCRIPTION LOGIC TYPE 7400 Quad 2-InputNANDGates 14 pinIC TTL 7404 Hex InvertingGates 16 pinIC TTL 7408 Quad 2-InputANDGates 14 pinIC TTL 7432 Quad 2-InputOR Gates 14 pinIC TTL NOTE: TimeTime 0s 0.25us 0.50us 0.75us 1.00us 1.25us 1.50us 1.75us 2.00us A B S C

- 14. 74 Indicatesthatit isTTL type and alsoshowsthe temperature range (COMMERCIALTEMPARATURE RANGE) Pin7-Gnd Pin14-Vcc Commercial: 0°C to 85°C Industrial: −40°C to 100°C Automotive: −40°C to 125°C Extended: −40°C to 125°C Military: −55°C to 125°C IMPORTANT UNDERSTANDINGS: IMPORTANT PARAMETERS FOR GATES: Switchingspeed Powerdissipation Delaytime Supplyvoltage While selectinglogicgate icsforour requirementwe choose itthe basisof the above measuring standards DIFFERENT TECHNOLOGY: RTL DDL DTL TTL-7400 series CMOS-4000 series APPLICATION: Half adder Full adder Encoder Decoder Multiplexer