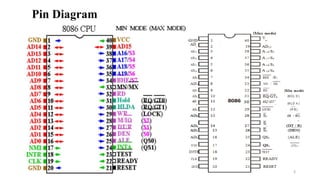

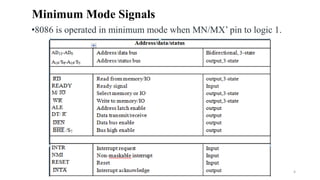

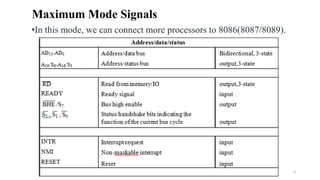

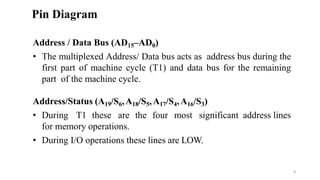

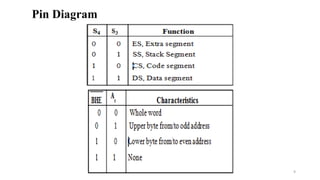

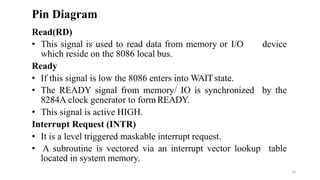

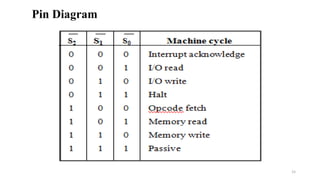

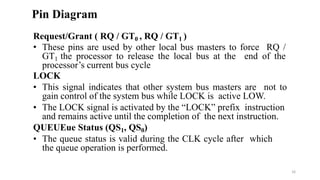

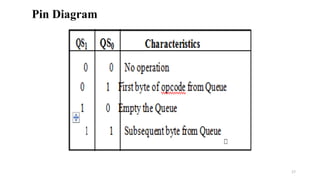

The document describes the pin diagram and functions of various pins of the 8086 microprocessor. It discusses pins for address/data bus, read/write signals, interrupts, reset, clock, power and ground. It also covers minimum/maximum mode pins, hold acknowledge, request/grant, lock and queue status pins. The 8086 can operate in minimum or maximum mode depending on the state of the MN/MX pin. It uses a multiplexed address/data bus and address latch enable signal to separate address and data.