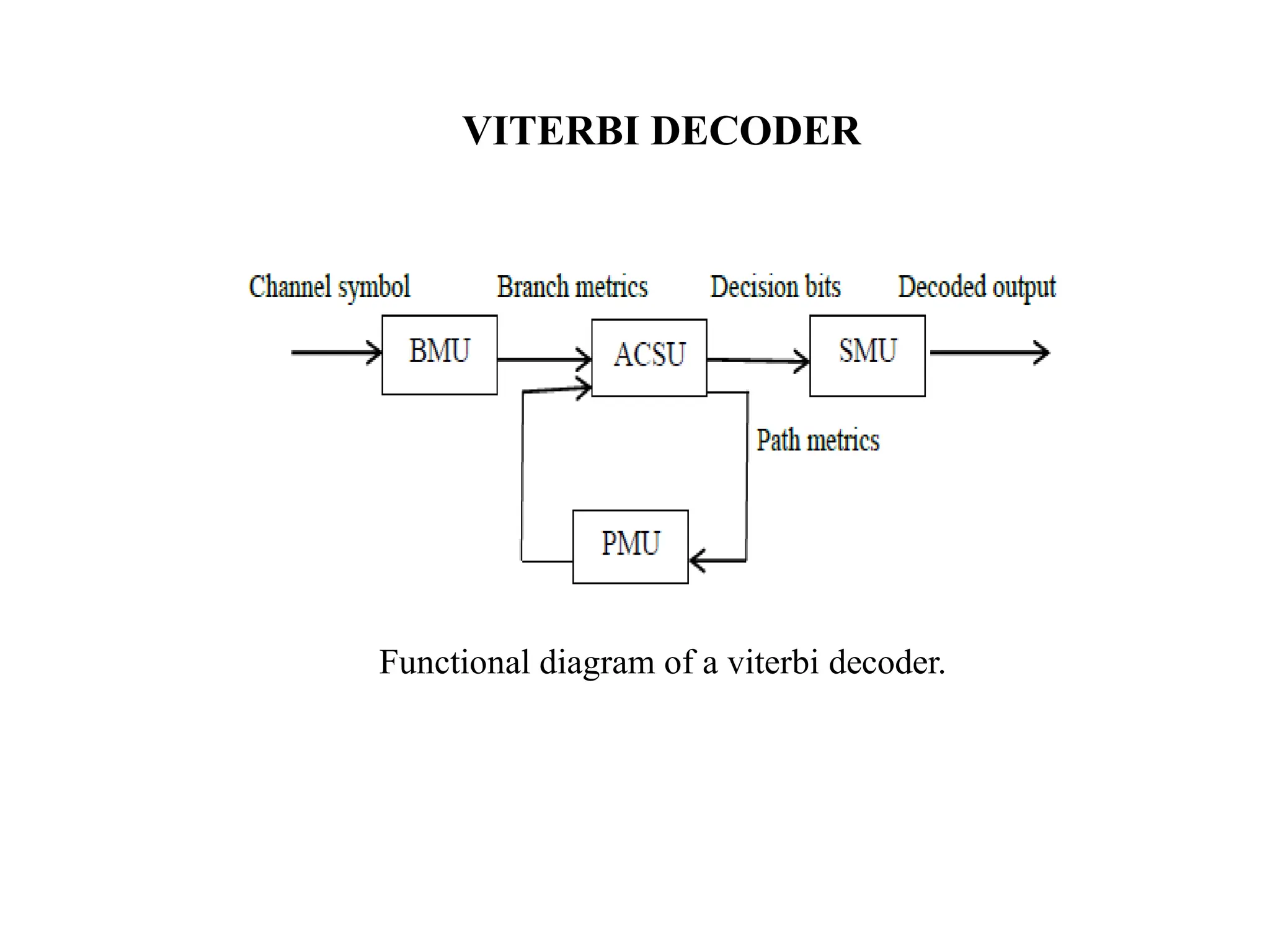

This document discusses a design for a high-speed, low-power Viterbi decoder using a pre-computation architecture that integrates a T-algorithm to minimize power consumption without sacrificing decoding speed. The introduction of the proposed architecture aims to effectively reduce power while maintaining performance, particularly for applications like digital video broadcasting. Additionally, it reviews existing literature on low-power Viterbi decoders and presents design considerations and benefits.