The document provides an overview of computer architecture, focusing on instruction set architecture (ISA), processor architecture, and memory organization, particularly distinguishing between von Neumann and Harvard architectures. It details the components of a typical computer system, dives into ARM CPU architecture and instruction sets, and explores memory types and addressing. Additionally, it discusses assembly programming and the functioning of registers, memory, and arithmetic operations in a computer system.

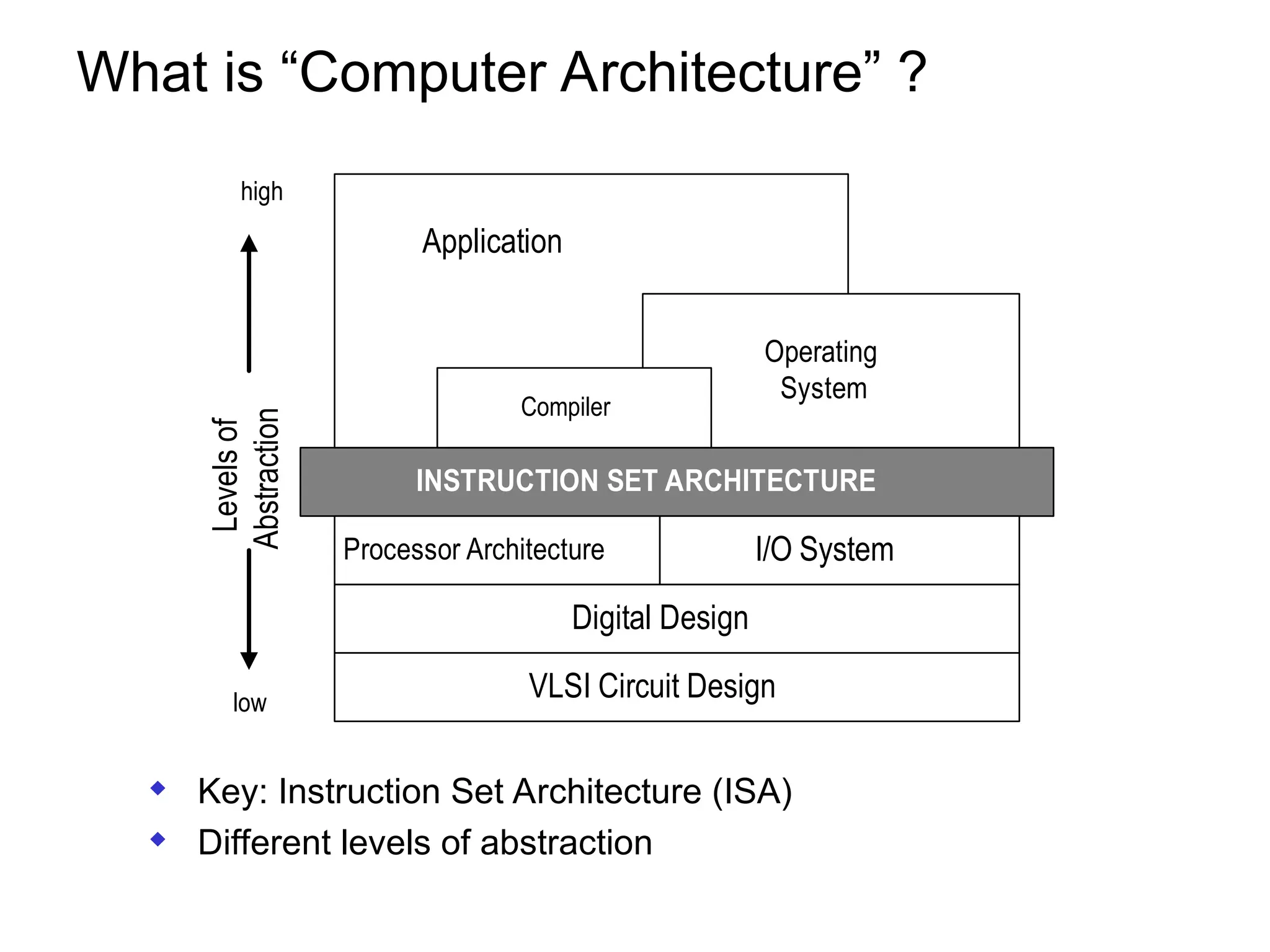

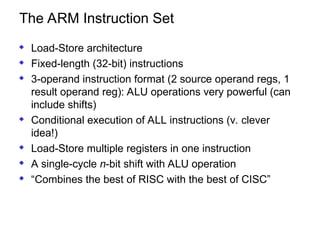

![Memory in detail

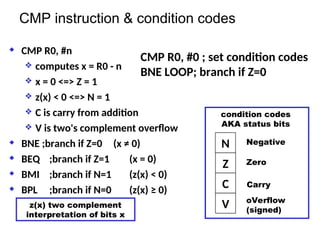

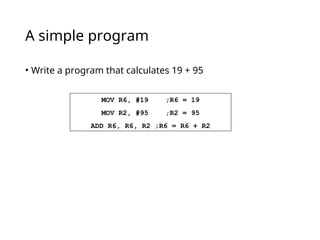

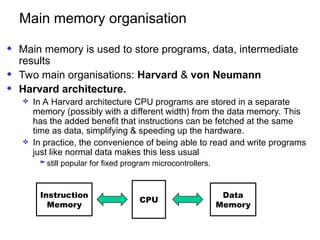

Memory locations store instructions data and

each have unique numeric addresses

Usually addresses range from 0 up to some

maximum value.

Memory space is the unique range of possible

memory addresses in a computer system

We talk about “the address of a memory

location”.

Each memory location stores a fixed number

of bits of data, normally 8, 16, 32 or 64

We write mem8[100], mem16[100] to indicate

the value of the 8 or 16 bits with memory

address 100 etc

0 02E

machine

code

2 02F

1 030

7 000

--

0AA0

0110

0BB0

--

--

000

001

002

003

004

005

006

02E

02F

030

...](https://image.slidesharecdn.com/lecture3-240922032005-2caab6bf/85/Embedded-Systems-ARM-Computer-Architecture-7-320.jpg)

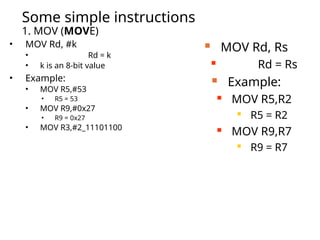

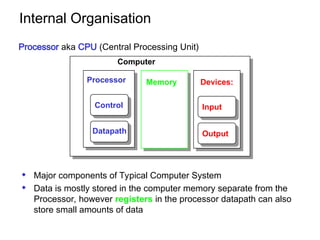

![Internal Registers & Memory

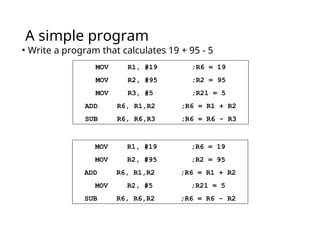

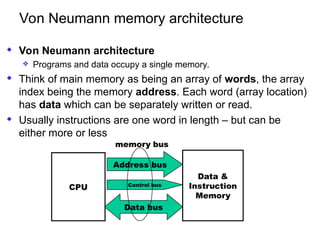

Internal registers (e.g. A, R0) are

same length as memory word

Word READ:

A := Mem16[addr]

Word WRITE:

Mem16[addr] := A

Byte READ:

A := 00000000 Mem8[addr]

Byte WRITE:

Mem8[addr] := A(7:0) (bottom 8 bits)

16 bits

8 bits 8 bits

bottom

8

Top

8

A

Memory

16 bits](https://image.slidesharecdn.com/lecture3-240922032005-2caab6bf/85/Embedded-Systems-ARM-Computer-Architecture-9-320.jpg)

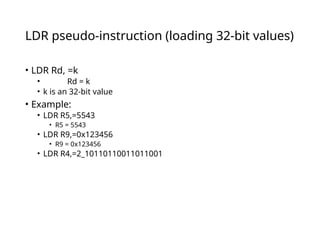

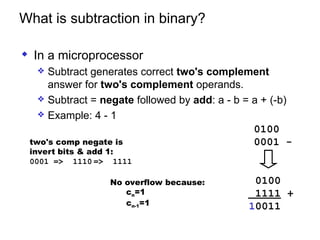

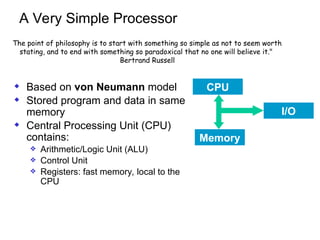

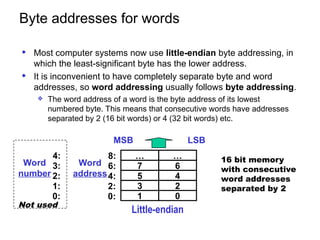

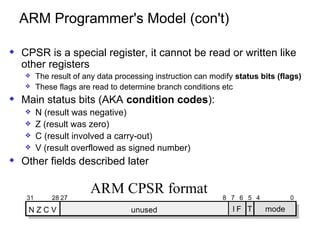

![1. Levels of representation in

computers

High Level Language

Program

Assembly Language

Program

Machine Language

Program

Control Signal

Specification

Compiler

Assembler

Machine

Interpretation

temp := v[k];

v[k] := v[k+1];

v[k+1] := temp;

lw $15, 0($2)

lw $16, 4($2)

sw $16, 0($2)

sw $15, 4($2)

0000 1001 1100 0110 1010 1111 0101 1000

1010 1111 0101 1000 0000 1001 1100 0110

1100 0110 1010 1111 0101 1000 0000 1001

0101 1000 0000 1001 1100 0110 1010 1111](https://image.slidesharecdn.com/lecture3-240922032005-2caab6bf/85/Embedded-Systems-ARM-Computer-Architecture-16-320.jpg)

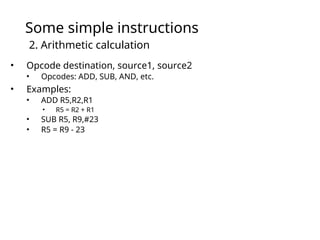

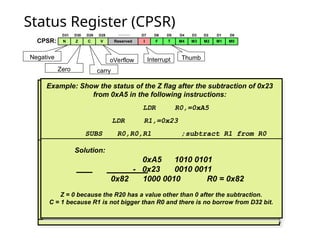

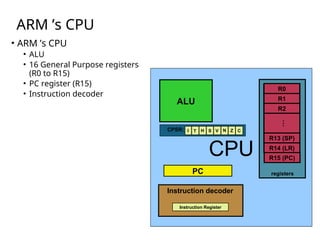

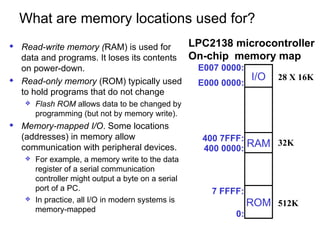

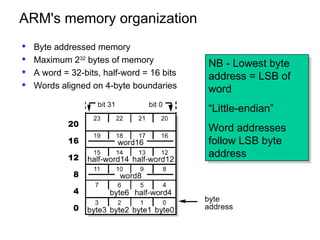

![ARM Assembly Quick Introduction

MOV ra, rb

MOV ra, #n

ra := rb

ra := n

n decimal in range -128 to 127

(other values possible, see later)

ADD ra, rb, rc

ADD ra, rb, #n

ra := rb + rc

ra := rb + n

SUB => – instead of +

CMP ra, rb

CMP ra, #n

set status bits on ra-rb

set status bits on ra-n

CMP is like SUB but has no destination

register ans sets status bits

B label branch to label BL label is branch & link

BEQ label

BNE label

BMI label

BPL label

branch to label if zero

branch if not zero

branch if negative

branch if zero or plus

Branch conditions apply to the

result of the last instruction to set

status bits

(ADDS/SUBS/MOVS/CMP etc).

LDR ra, label

STR ra, label

ADR ra, label

LDR ra, [rb]

STR ra, [rb]

ra := mem[label]

mem[label] := ra

ra :=address of label

ra := mem[rb]

mem[rb] := ra

LDRB/STRB => byte transfer

Other address modes:

[rb,#n] => mem[rb+n]

[rb,#n]! => mem[rb+n], rb := rb+n

[rb],#n => mem[rb], rb:=rb+n

[rb+ri] => mem[rb+ri]](https://image.slidesharecdn.com/lecture3-240922032005-2caab6bf/85/Embedded-Systems-ARM-Computer-Architecture-18-320.jpg)

![Introduction to ARM data processing

a := b+c-d

ADD R0, R1, R2

SUB R0, R0, R3

a: R0

b: R1

c: R2

d: R3

Machine Instructions:

ADD Rx,Ry,Rz ;Rx := Ry + Rz

SUB Rx,Ry,Rz ;Rx := Ry - Rz

ARM has 16 registers R0-R15

If a,b,c,d are in registers:

LDR R1, B

LDR R2, C

LDR R3, D

ADD R0, R1, R2

SUB R0, R0, R3

STR R0, A

a

b

c

d

mem[A]

mem[B]

mem[C]

mem[D]

LOAD data to reg

from memory

STORE result to

memory from reg](https://image.slidesharecdn.com/lecture3-240922032005-2caab6bf/85/Embedded-Systems-ARM-Computer-Architecture-19-320.jpg)

![AREA Example, CODE ;name a code block

TABSIZE EQU 10 ;defines a numeric constant

X DCW 3 ; X (initialised to 3)

Y DCW 11 ; Y (initialised to 11)

Z % 4 ; 4 bytes (1 word) space for Z, uninitialised

ENTRY ;mark start

LDR r0, X ;load multiplier from mem[X]

LDR r1, Y ;load number to be multiplied from mem[Y]

MOV r2, #0 ;initialise sum

LOOP

ADD R2, R2, R1 ;add Y to sum

SUB r0, r0, #1 ;decrement count

CMP r0, #0 ;compare & set codes on R0

BNE LOOP ;loop back if not finished (R0 ≠ 0)

STR r2, Z ;store product in mem[Z]

END

An ARM assembly module

opcode operands

comments

symbols

module

header

and end](https://image.slidesharecdn.com/lecture3-240922032005-2caab6bf/85/Embedded-Systems-ARM-Computer-Architecture-20-320.jpg)