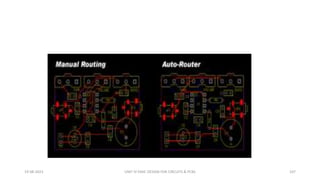

The document discusses electromagnetic compatibility (EMC) design considerations for circuits and printed circuit boards (PCBs). It covers topics like noise from relays and switches, nonlinearities in circuits, cross talk control, component selection and mounting, PCB trace impedance, routing, power distribution, decoupling, zoning, grounding, vias and terminations. It provides details on controlled impedance PCB trace design, factors that determine trace impedance, guidelines for board-level decoupling including capacitor placement based on plane spacing.