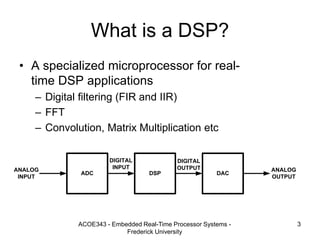

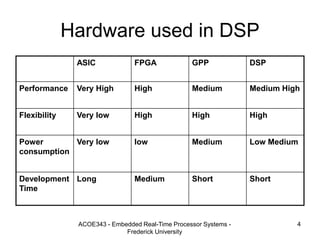

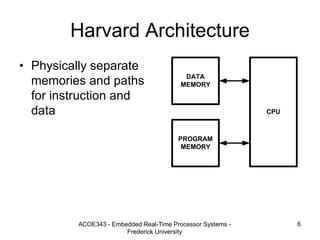

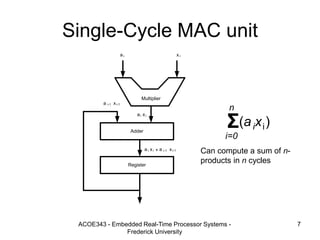

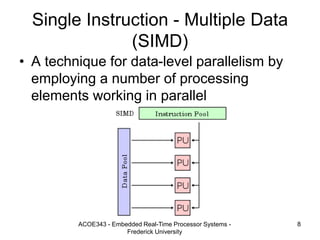

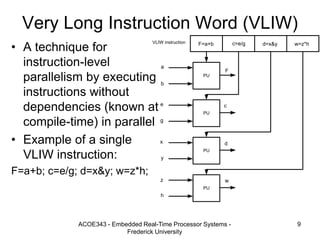

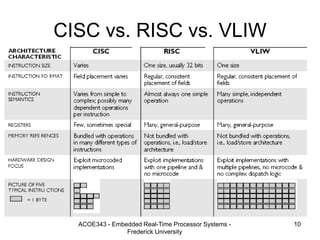

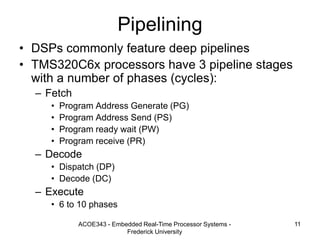

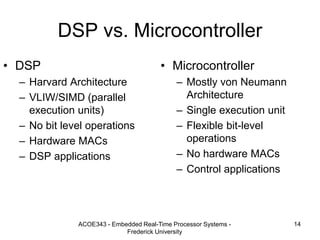

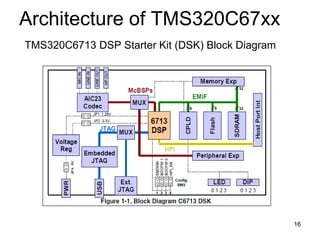

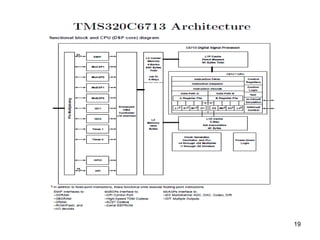

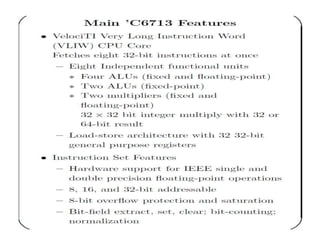

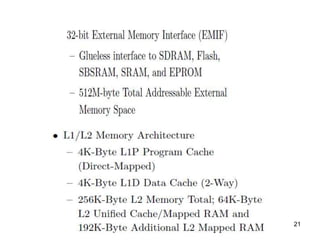

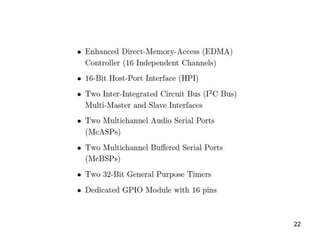

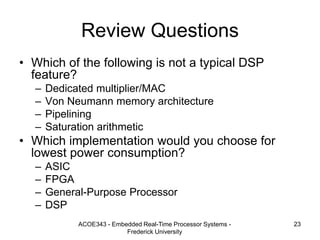

This document provides an introduction to digital signal processors (DSPs). It describes DSPs as specialized microprocessors for real-time signal processing applications like filtering and FFT. Key DSP features include a Harvard architecture, dedicated multiply-accumulate instructions, single-instruction multiple-data (SIMD) or very long instruction word (VLIW) architectures, pipelining, cache, and direct memory access. The document gives examples of the Texas Instruments TMS320C6713 DSP and its architecture.