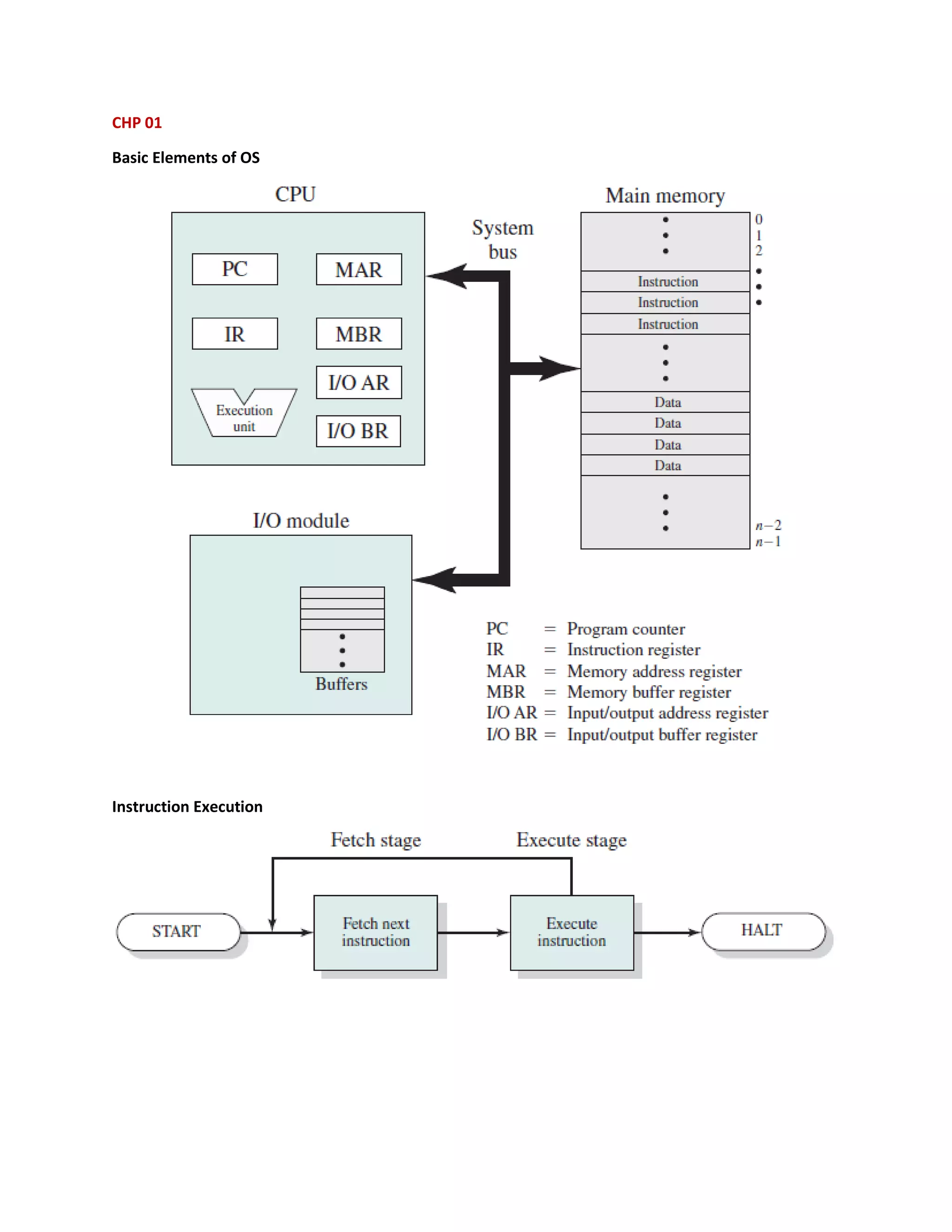

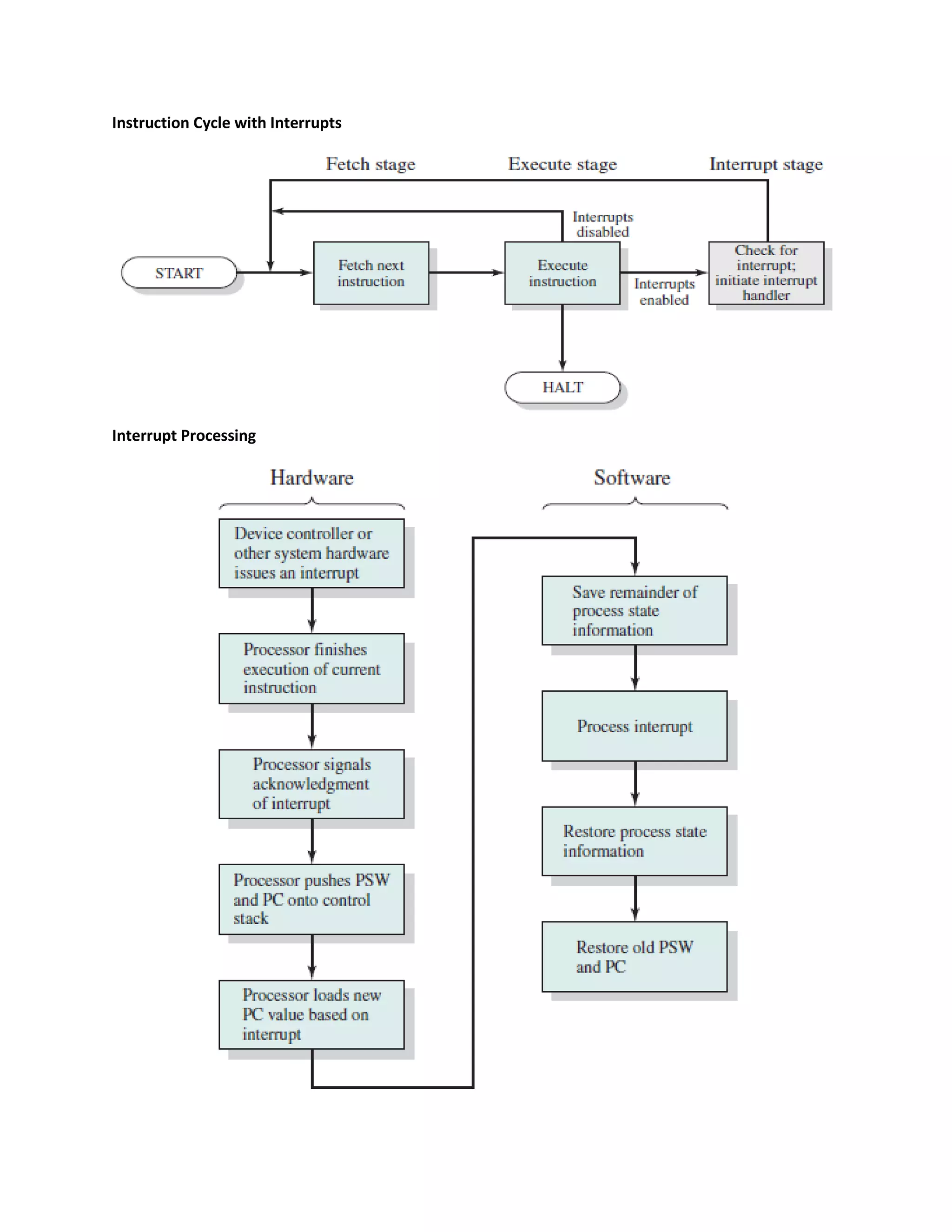

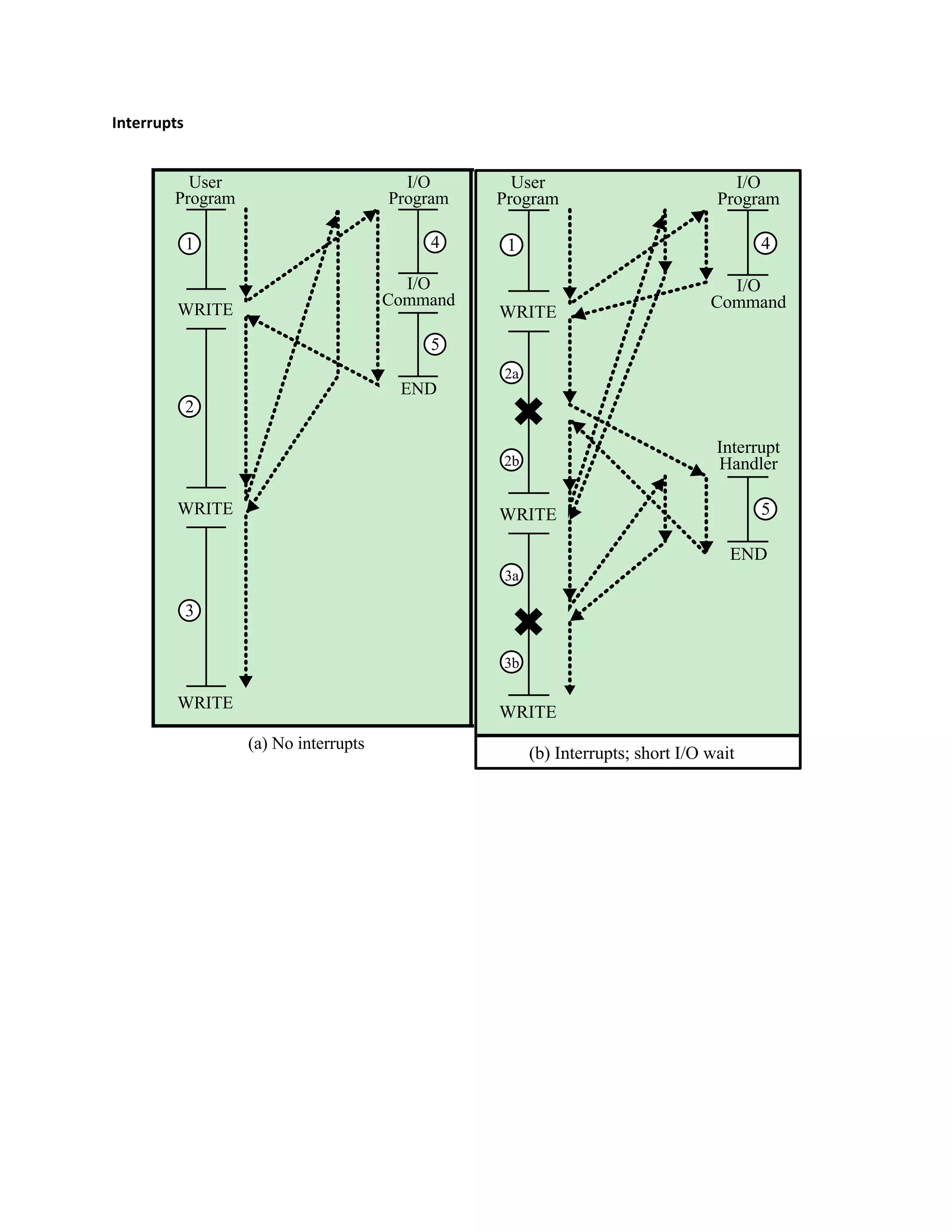

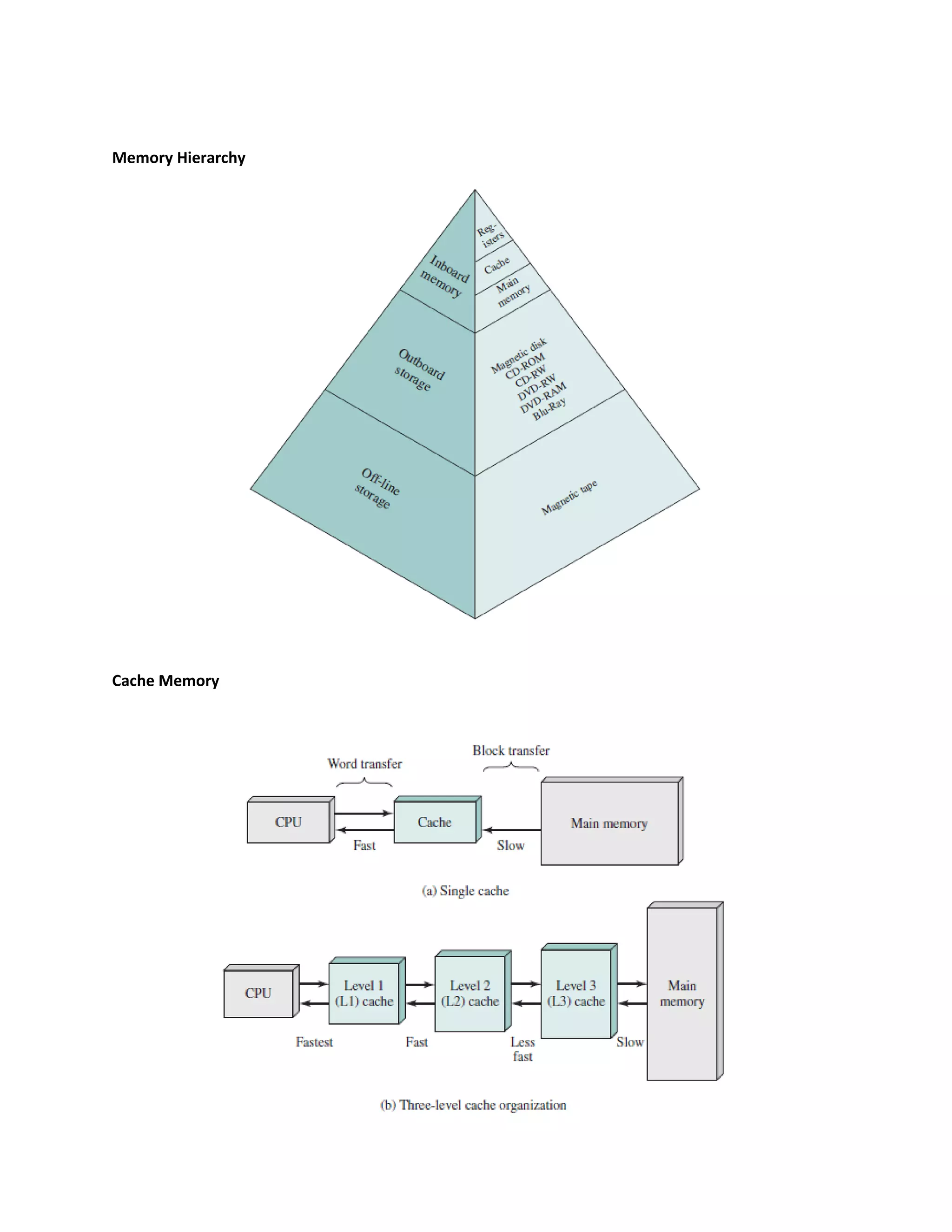

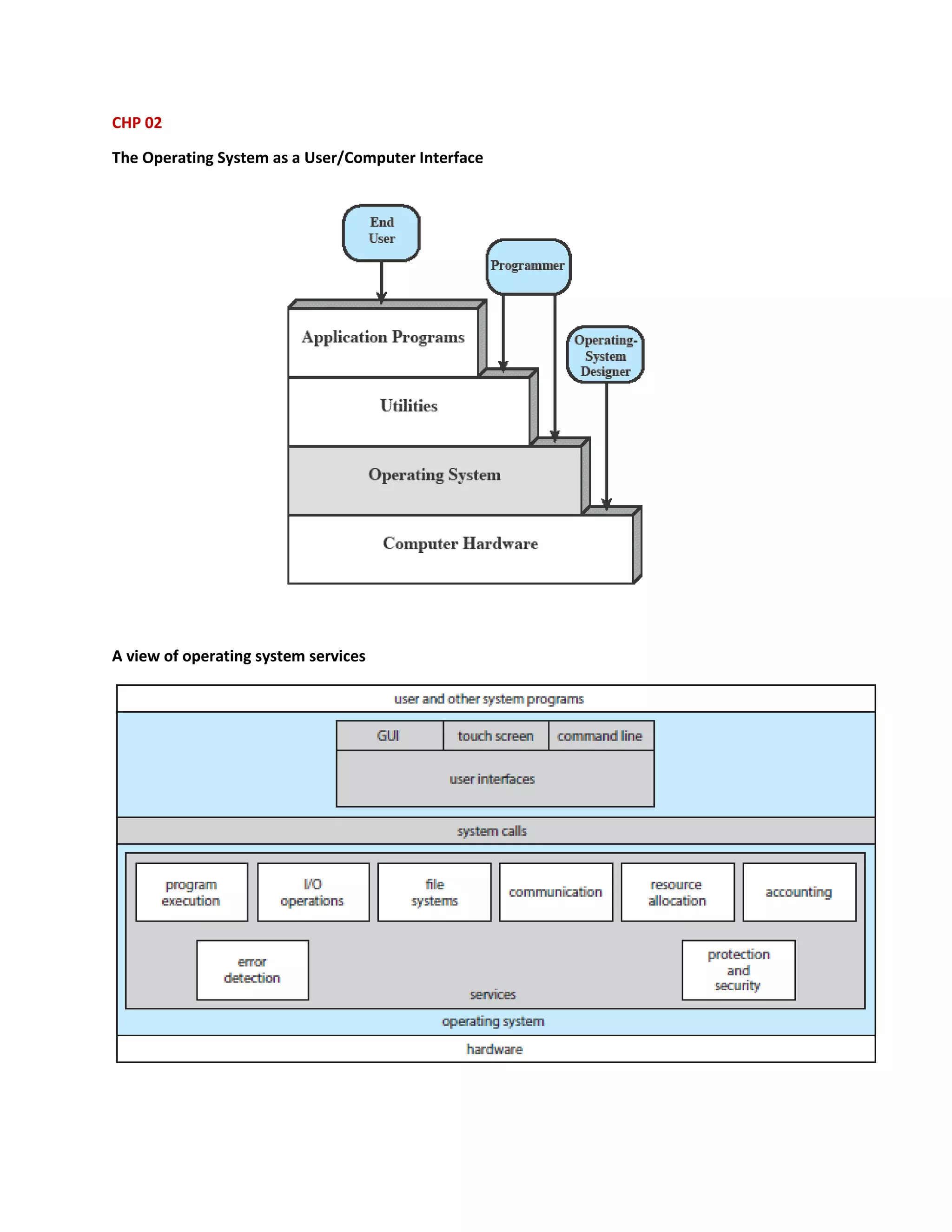

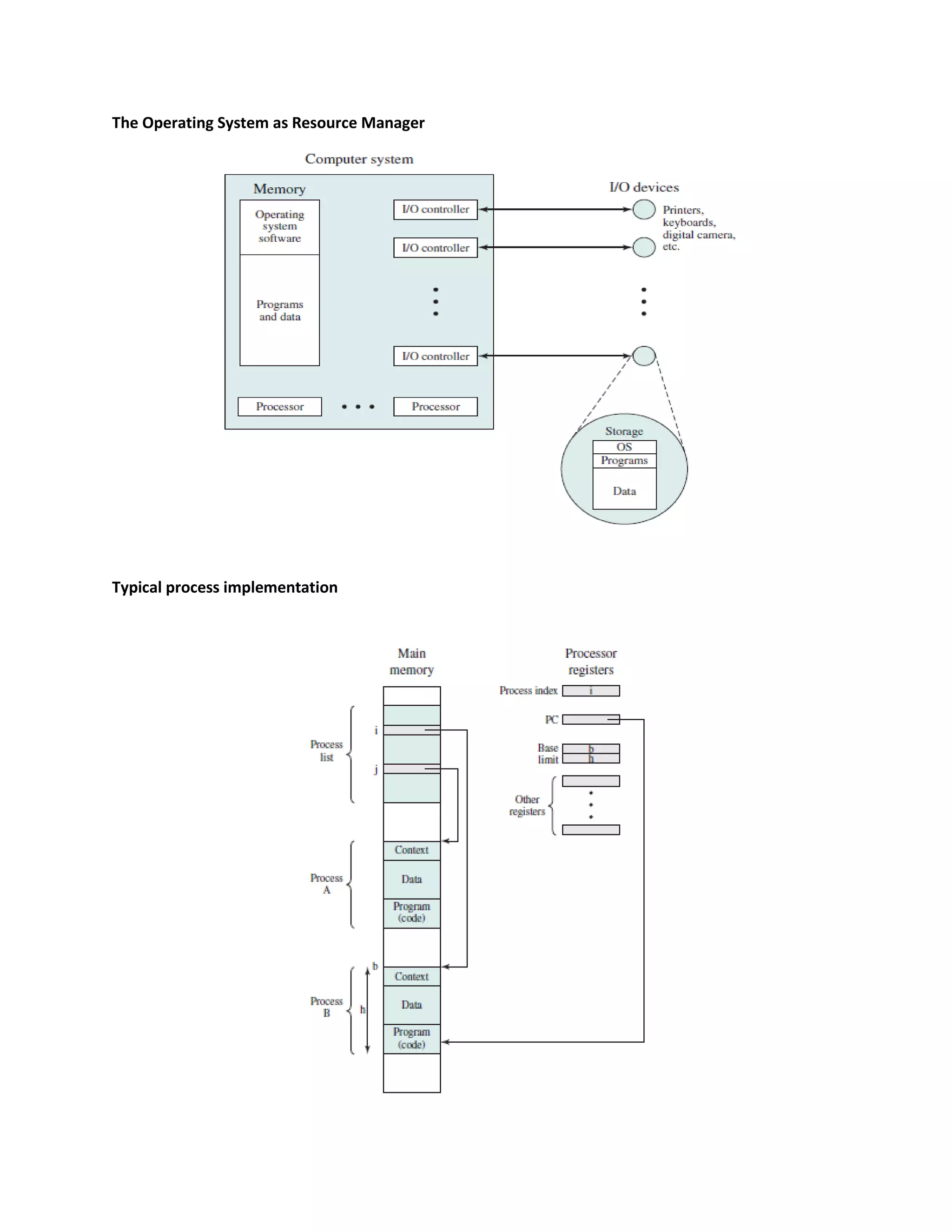

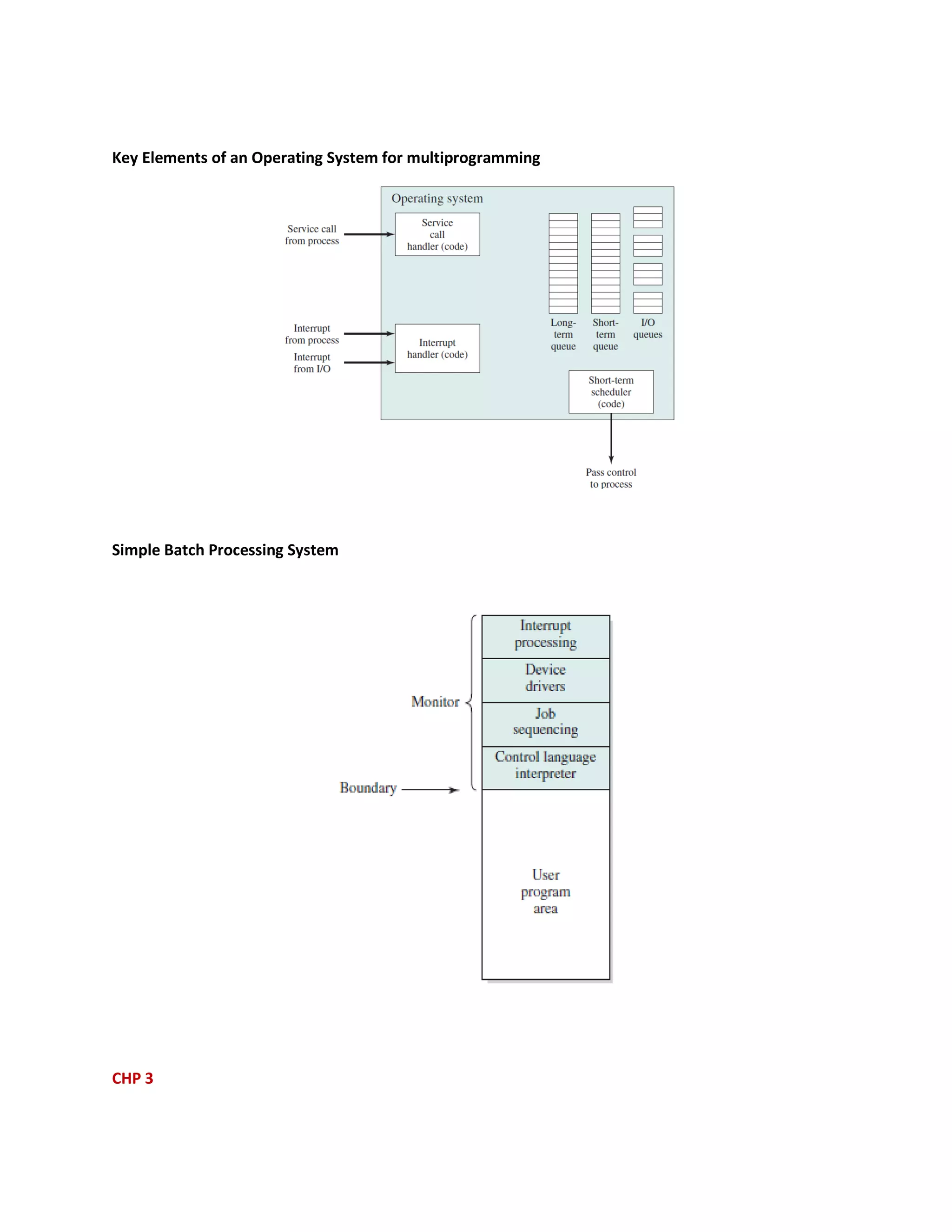

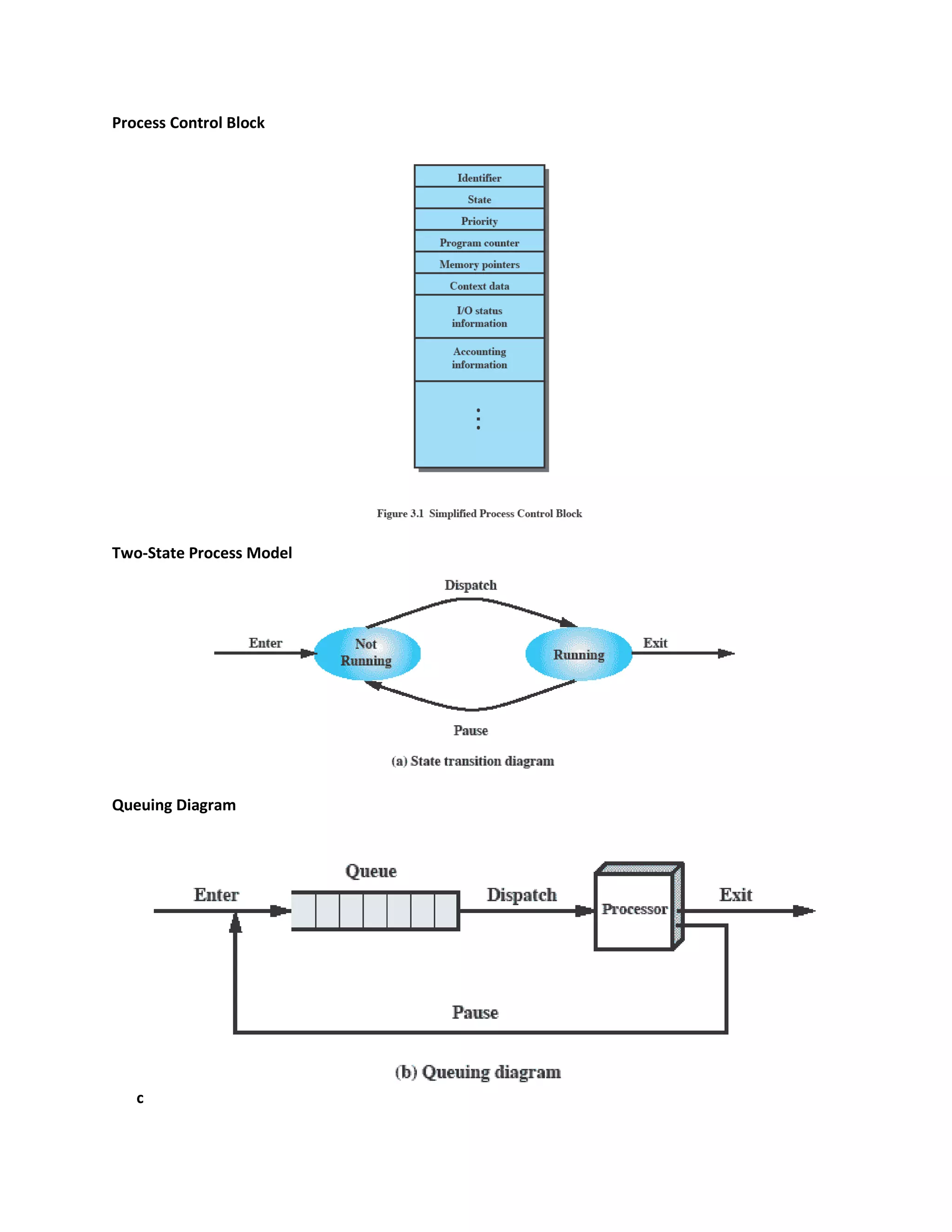

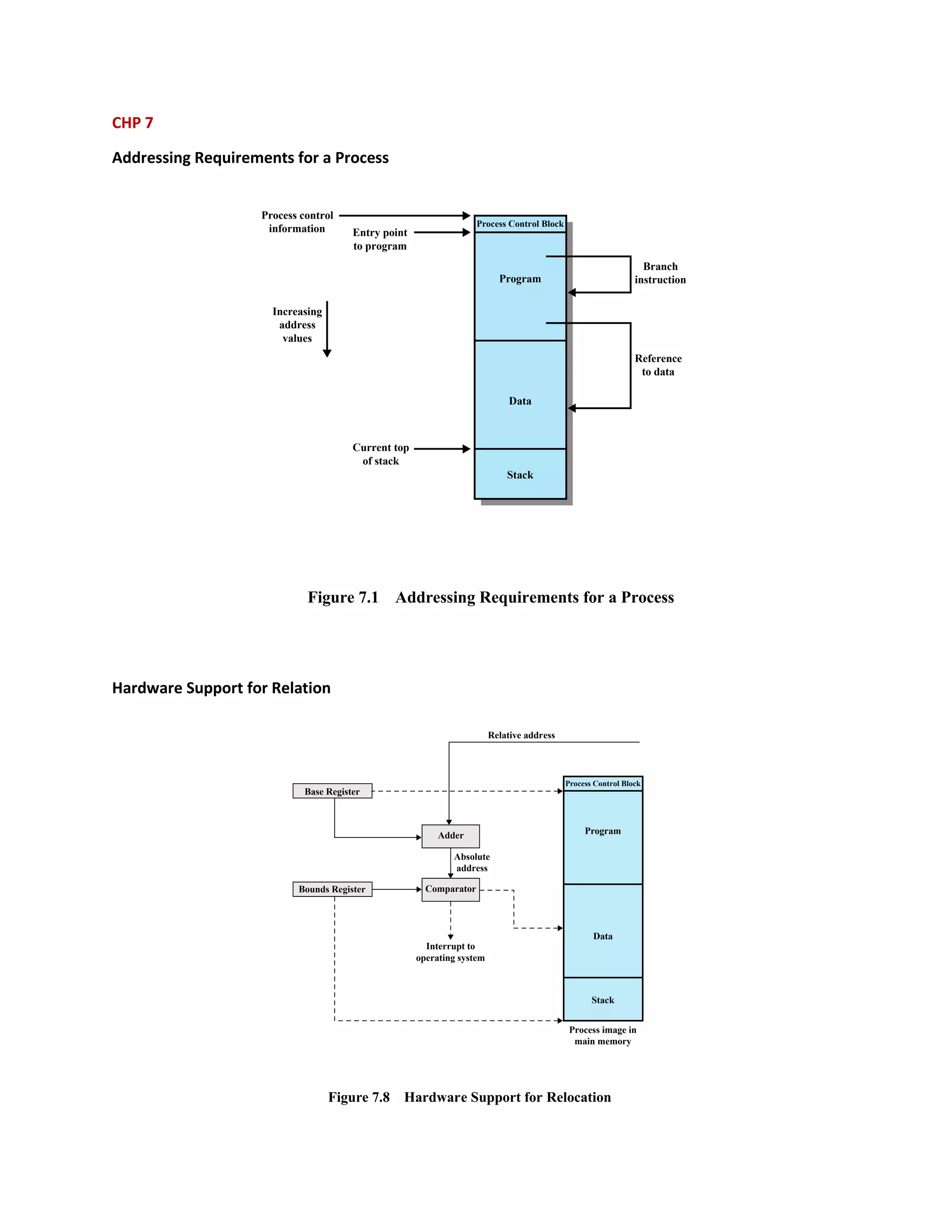

This document contains summaries of chapters from an operating systems textbook. Chapter 1 discusses instruction execution and interrupt processing, including how interrupts can cause a program's flow of control to change. Chapter 2 describes operating systems services and their role in resource management. Chapter 7 explains the addressing requirements for a process, including how processes are isolated through relocation using base and bounds registers.