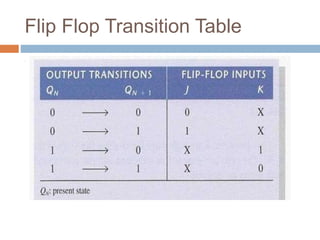

This document describes the design of a synchronous binary irregular counter with a counting sequence of 0011, 1100, 0000, 1000, 0100. It includes a state diagram, next-state table, Karnaugh maps to simplify the logic expressions, and a logic diagram for implementation. Specifically, it covers an introduction to counters, defines a synchronous counter, shows the state diagram and next-state table, uses K-maps to minimize the logic expressions for J0-J3 and K0-K3, and provides the final logic expressions and diagram for implementation.