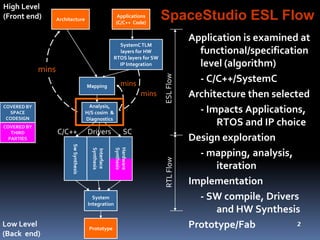

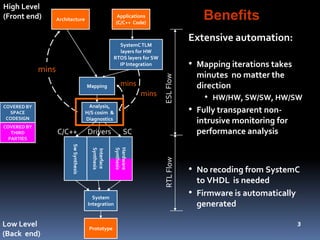

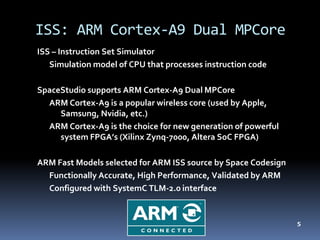

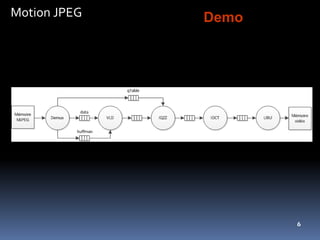

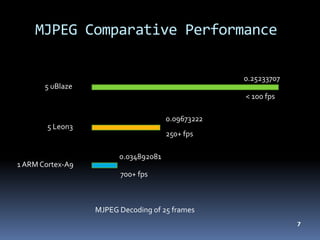

This document describes Space Codesign's ESL hardware/software co-design flow for ARM processor-based FPGAs. It allows designers to explore architecture and perform hardware/software partitioning, simulation and monitoring at a high level in SystemC before generating RTL and prototypes. Key benefits include extensive automation, transparent performance analysis, and no recoding needed between SystemC and VHDL. An example Motion JPEG demo shows the ARM Cortex-A9 core achieving over 700 fps compared to under 100 fps for a MicroBlaze and 250+ fps for a Leon3.