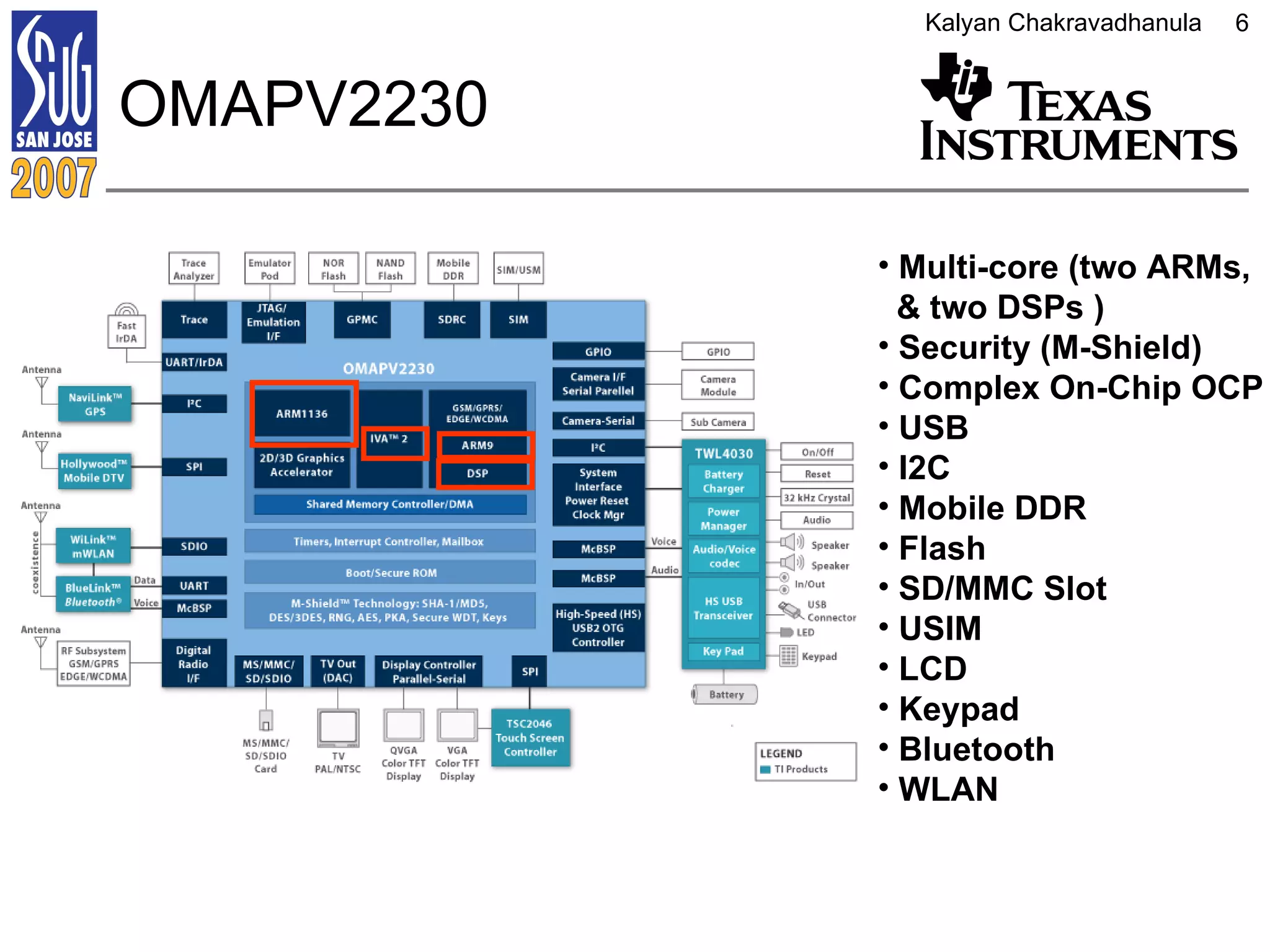

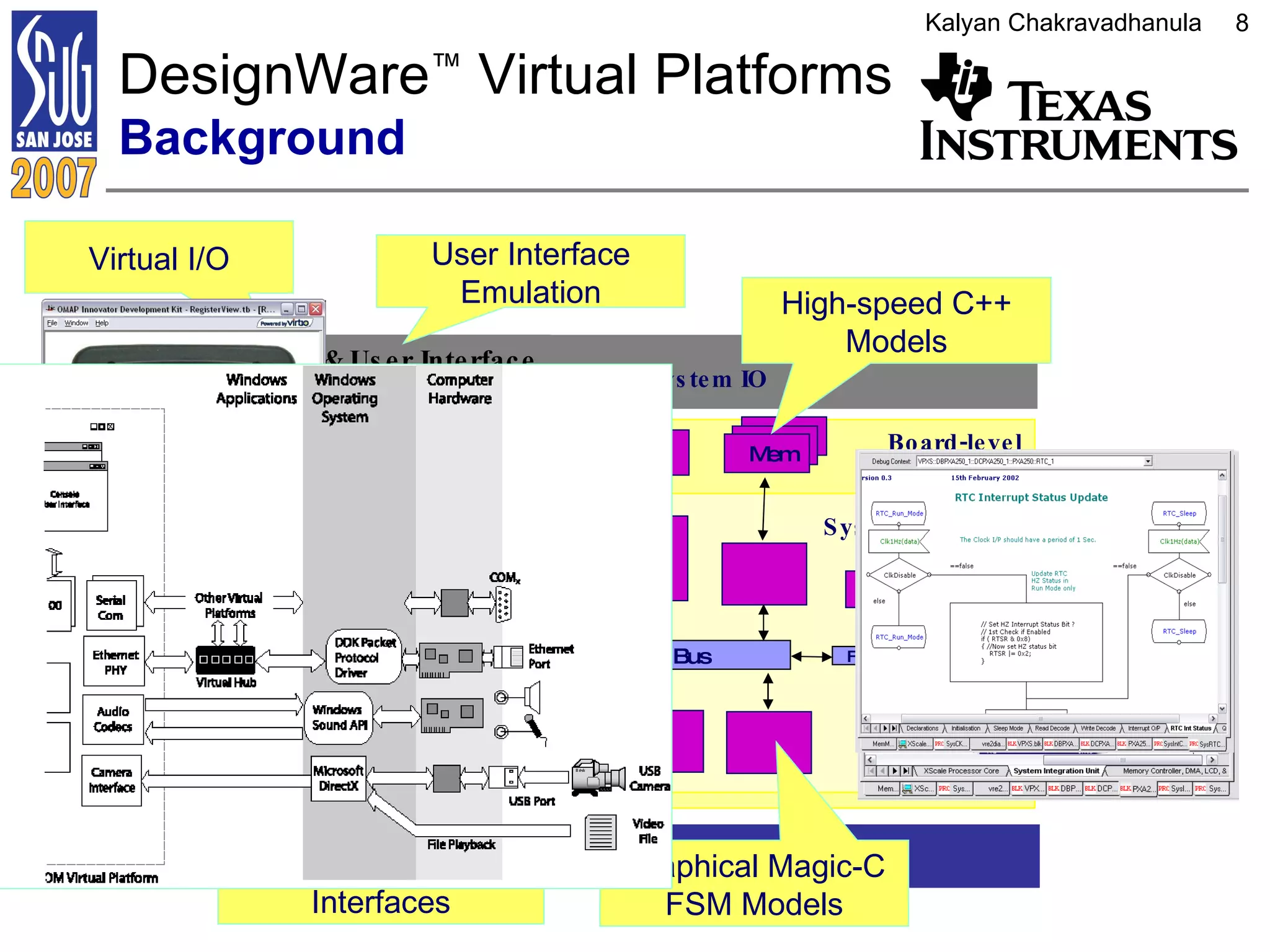

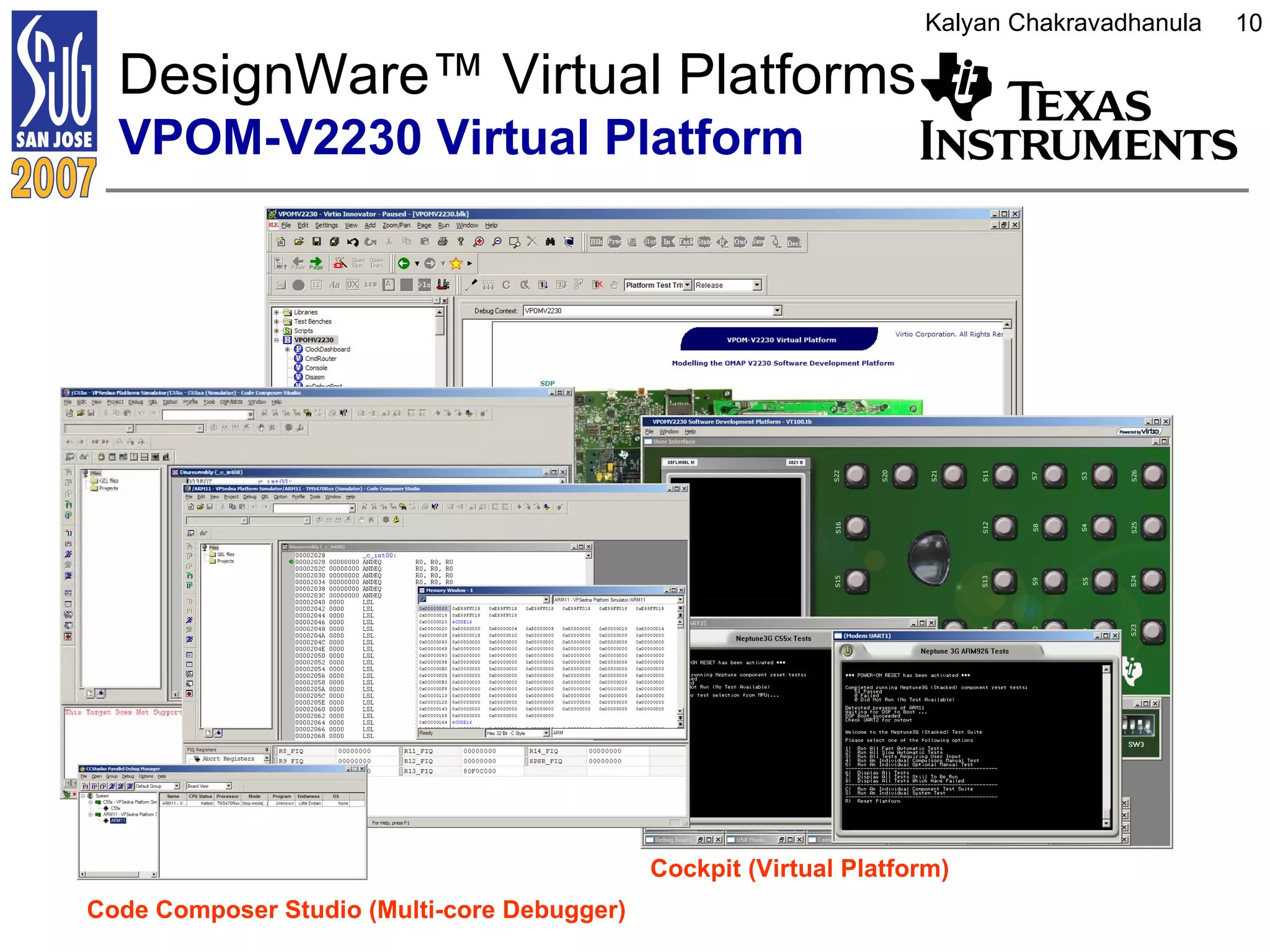

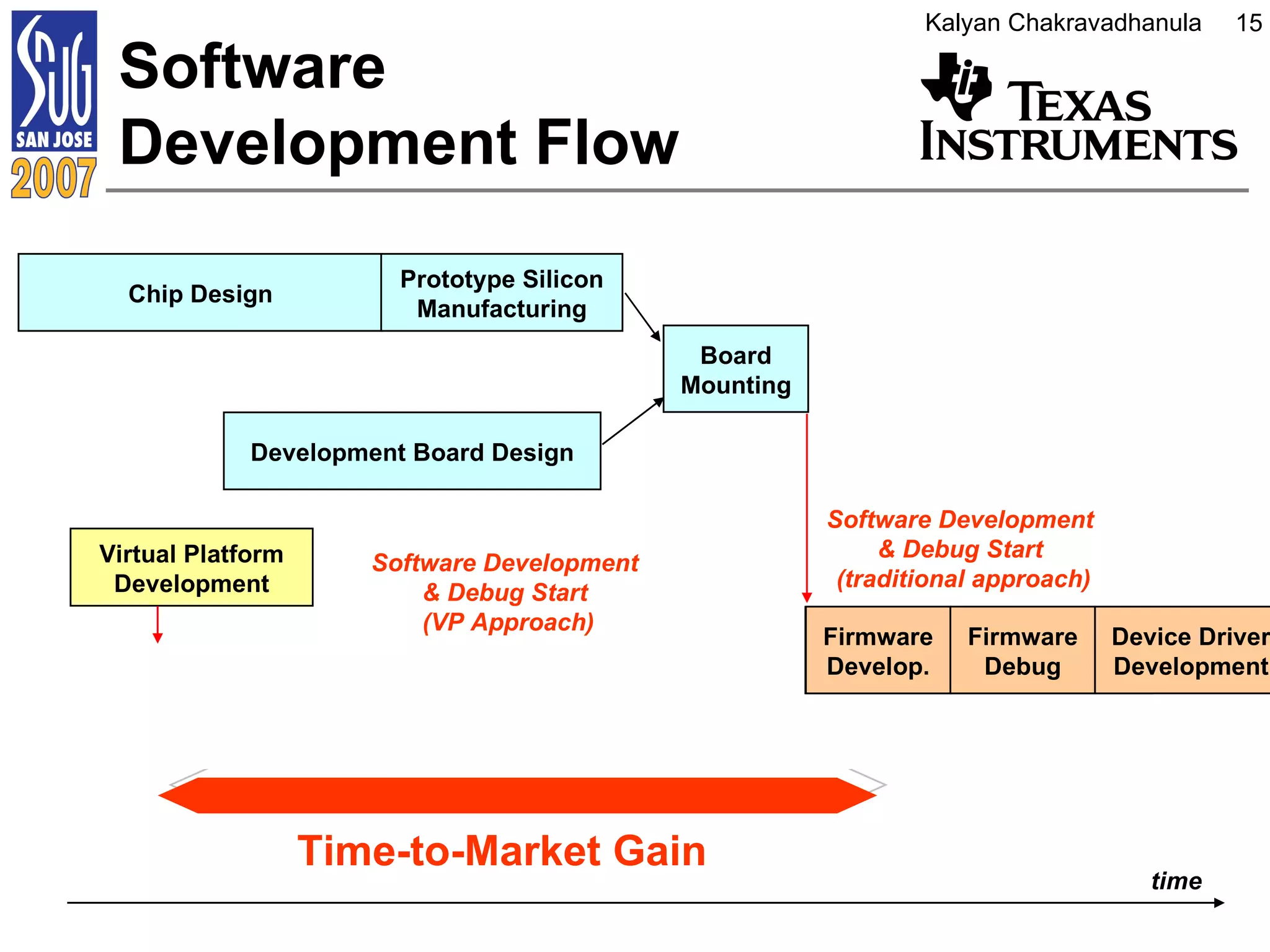

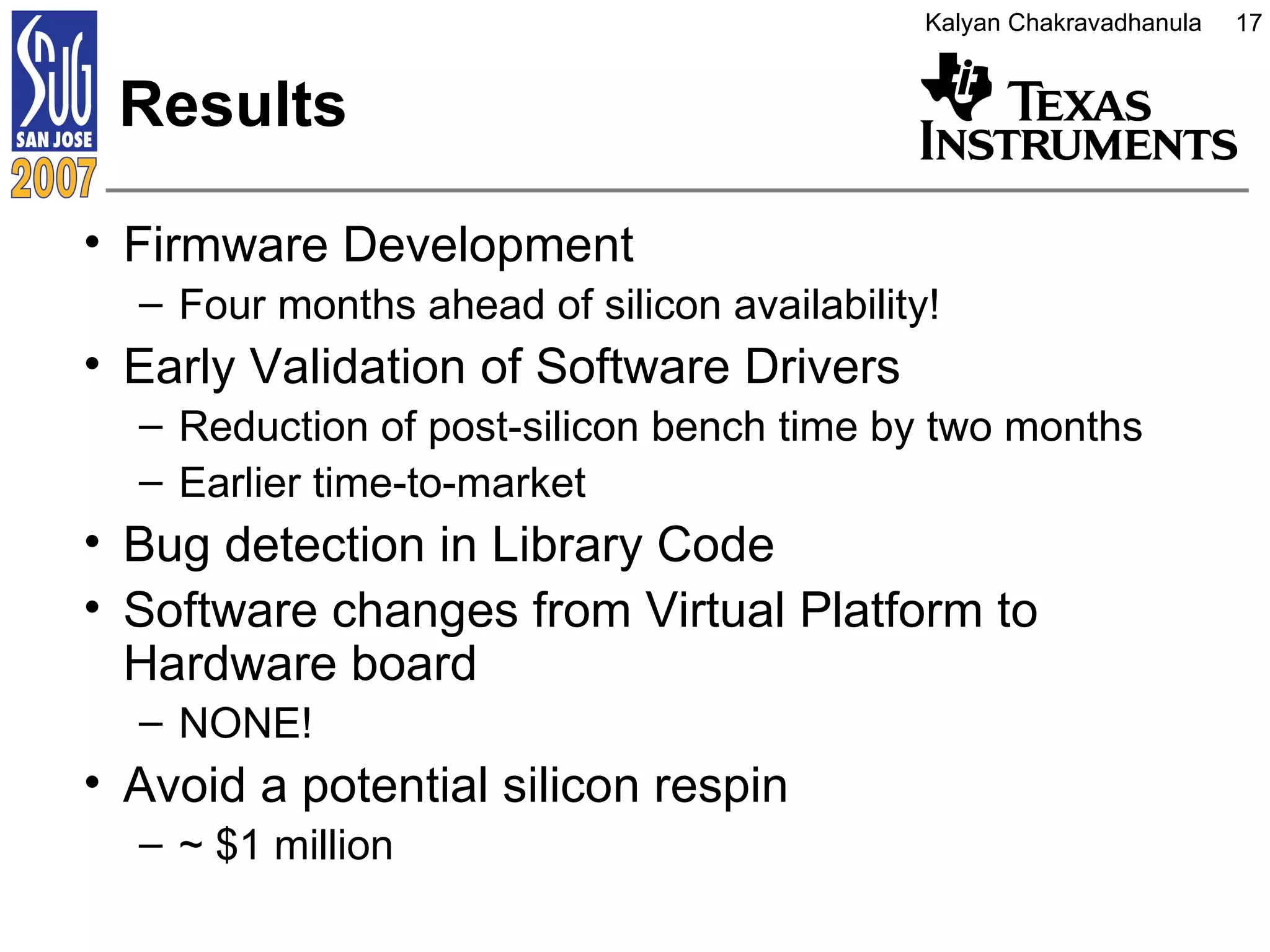

This document discusses using DesignWare Virtual Platforms for system level verification of a chip design through software development. It outlines how virtual platforms can model a complete embedded system to allow concurrent software development and hardware-software integration. The results shown indicate that using a virtual platform can accelerate firmware development, find bugs earlier, and reduce post-silicon debug time compared to traditional hardware-focused development.