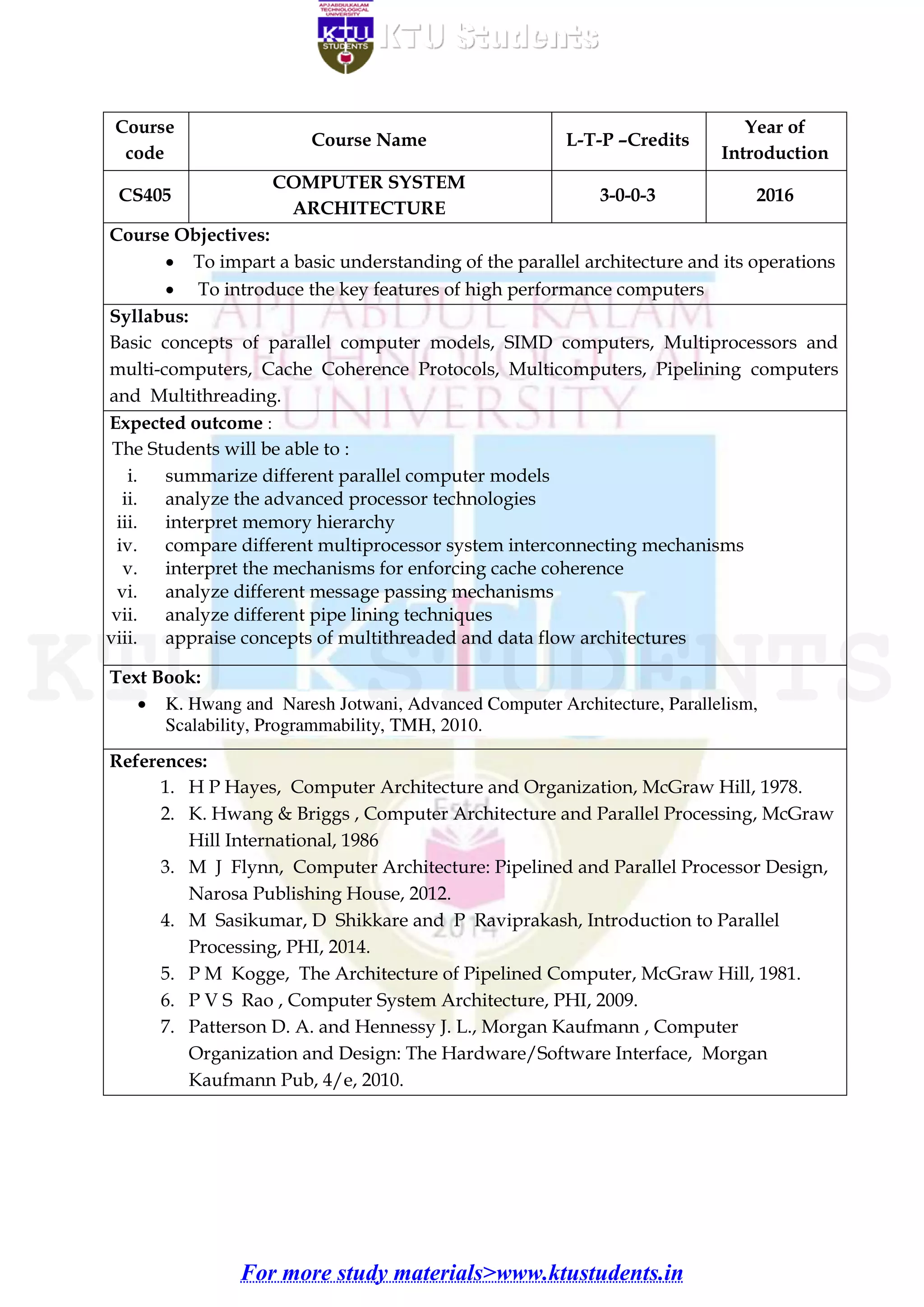

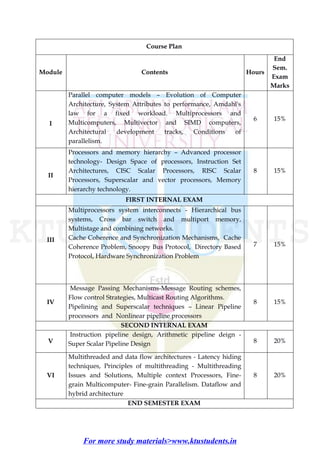

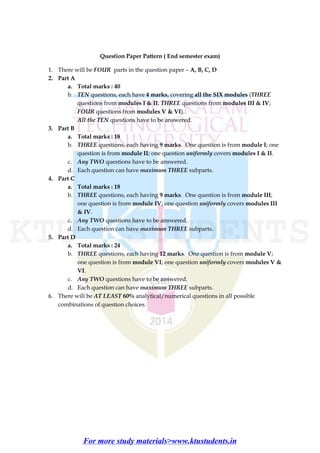

This document provides information about the course "Computer System Architecture". It is a 3 credit hour course introduced in 2016. The course aims to impart understanding of parallel architectures and high performance computers. The syllabus covers topics like parallel computer models, multiprocessors, cache coherence protocols, pipelining, and multithreading. The expected outcomes are that students will be able to summarize parallel models, analyze advanced processors and memory hierarchy, and appraise concepts of parallel architectures. The course is divided into 6 modules covering these topics, and assessed through internal exams, assignments, and an end semester exam.