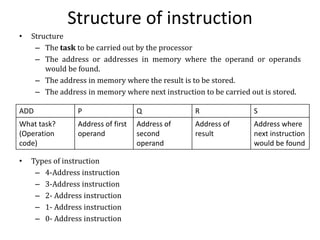

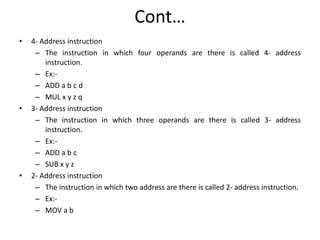

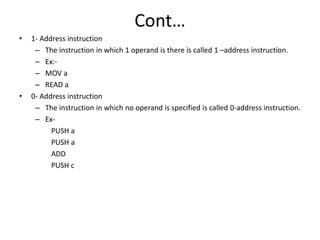

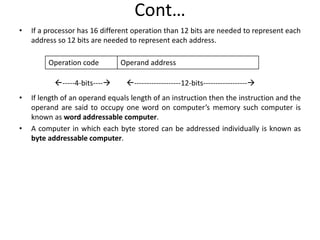

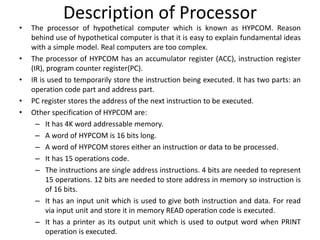

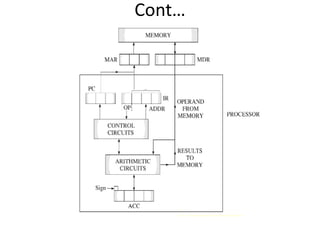

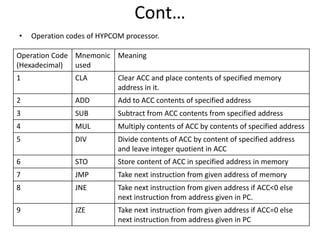

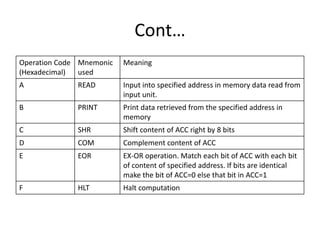

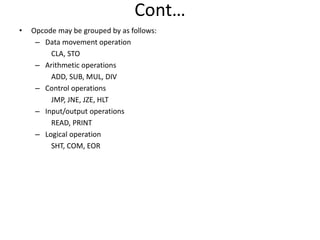

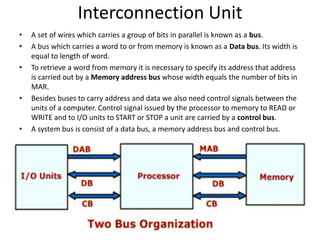

The document discusses the structure of computer instruction architecture, detailing various instruction types (4-, 3-, 2-, 1-, and 0-address instructions) and their respective examples. It introduces a hypothetical processor named 'hypcom', outlines its specifications, operation codes, and the interconnection system of buses for data communication. Additionally, it contrasts CISC (Complex Instruction Set Computer) and RISC (Reduced Instruction Set Computer) architectures, highlighting design choices that streamline instruction execution and optimize performance.