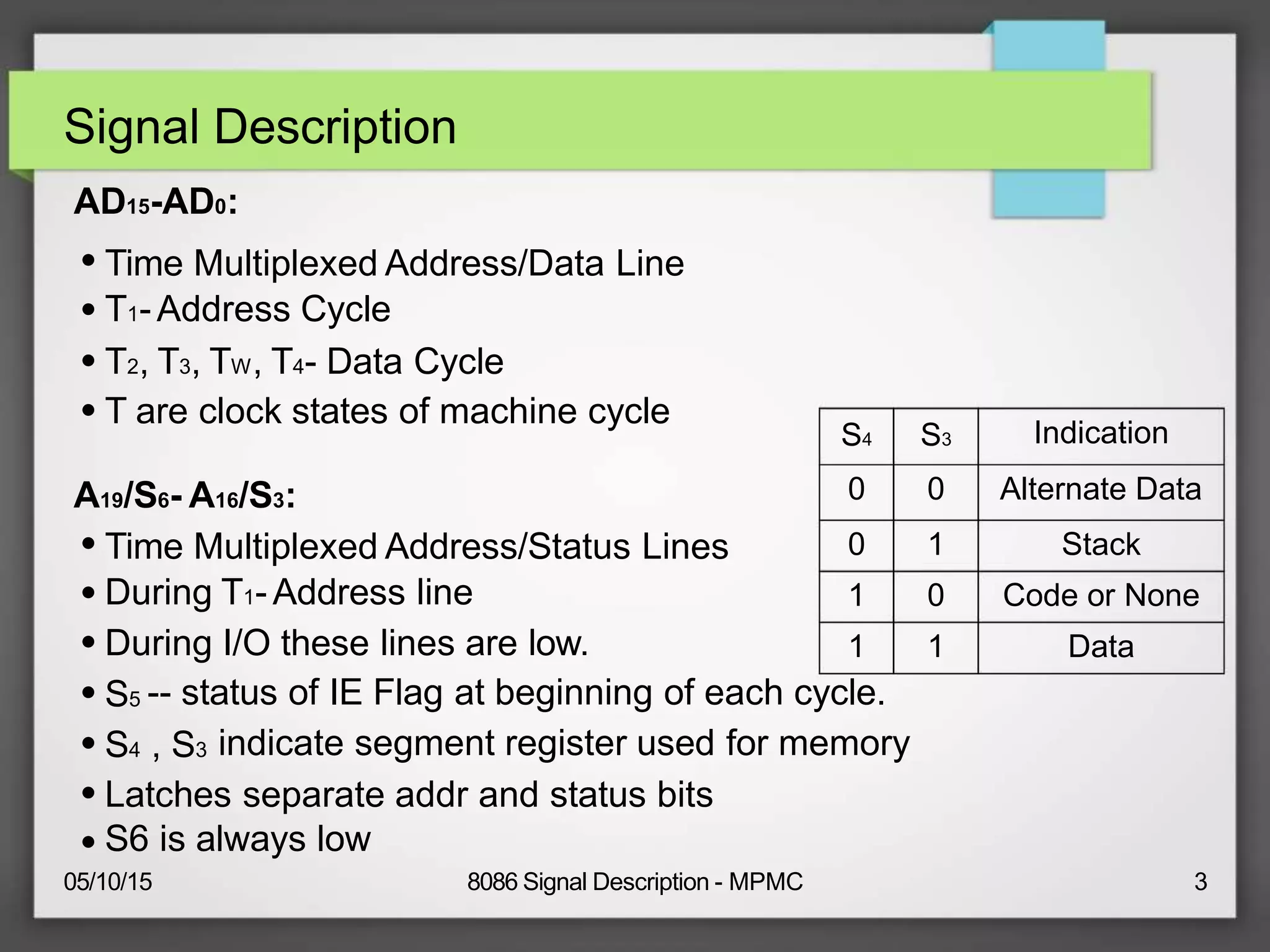

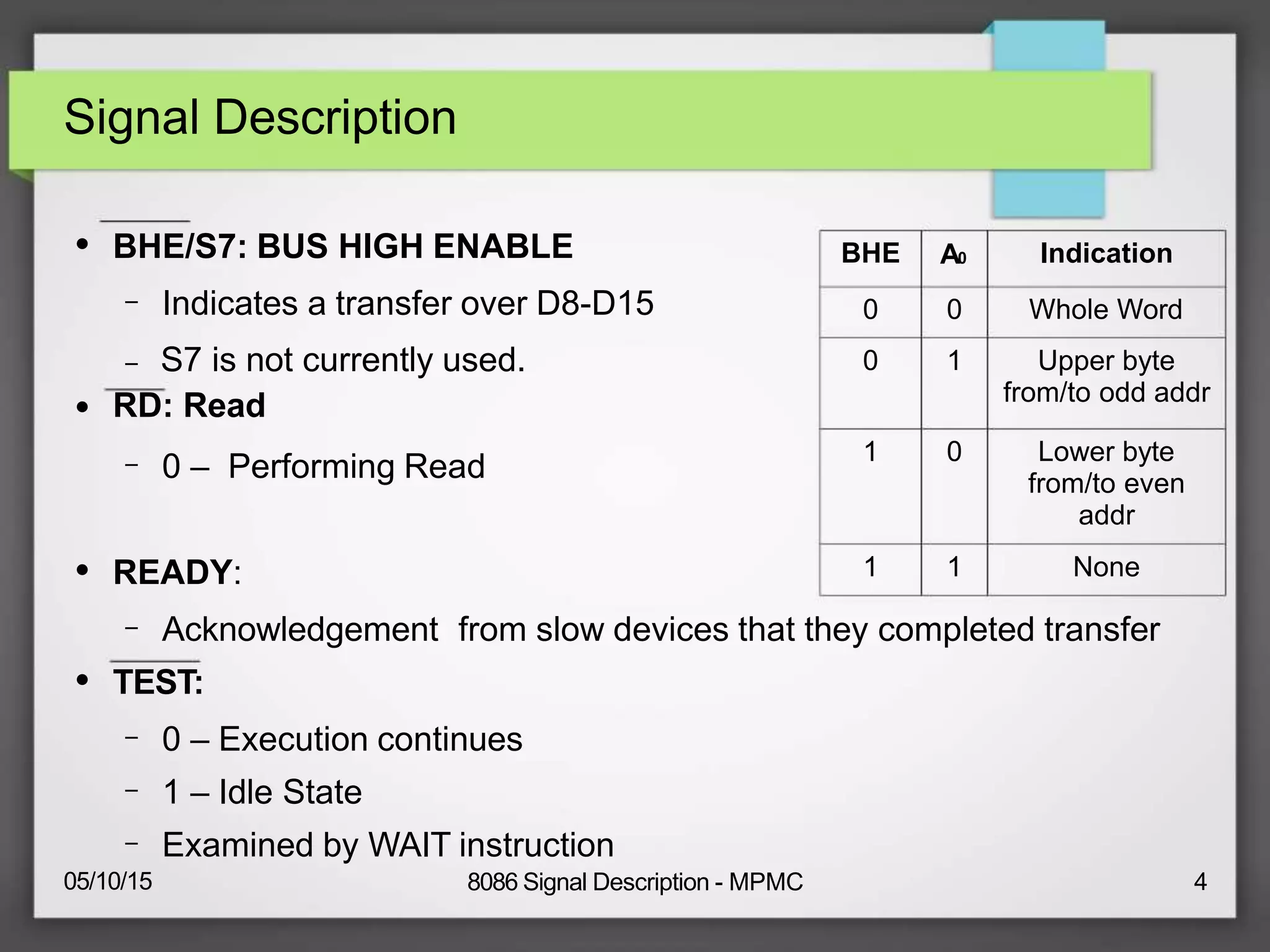

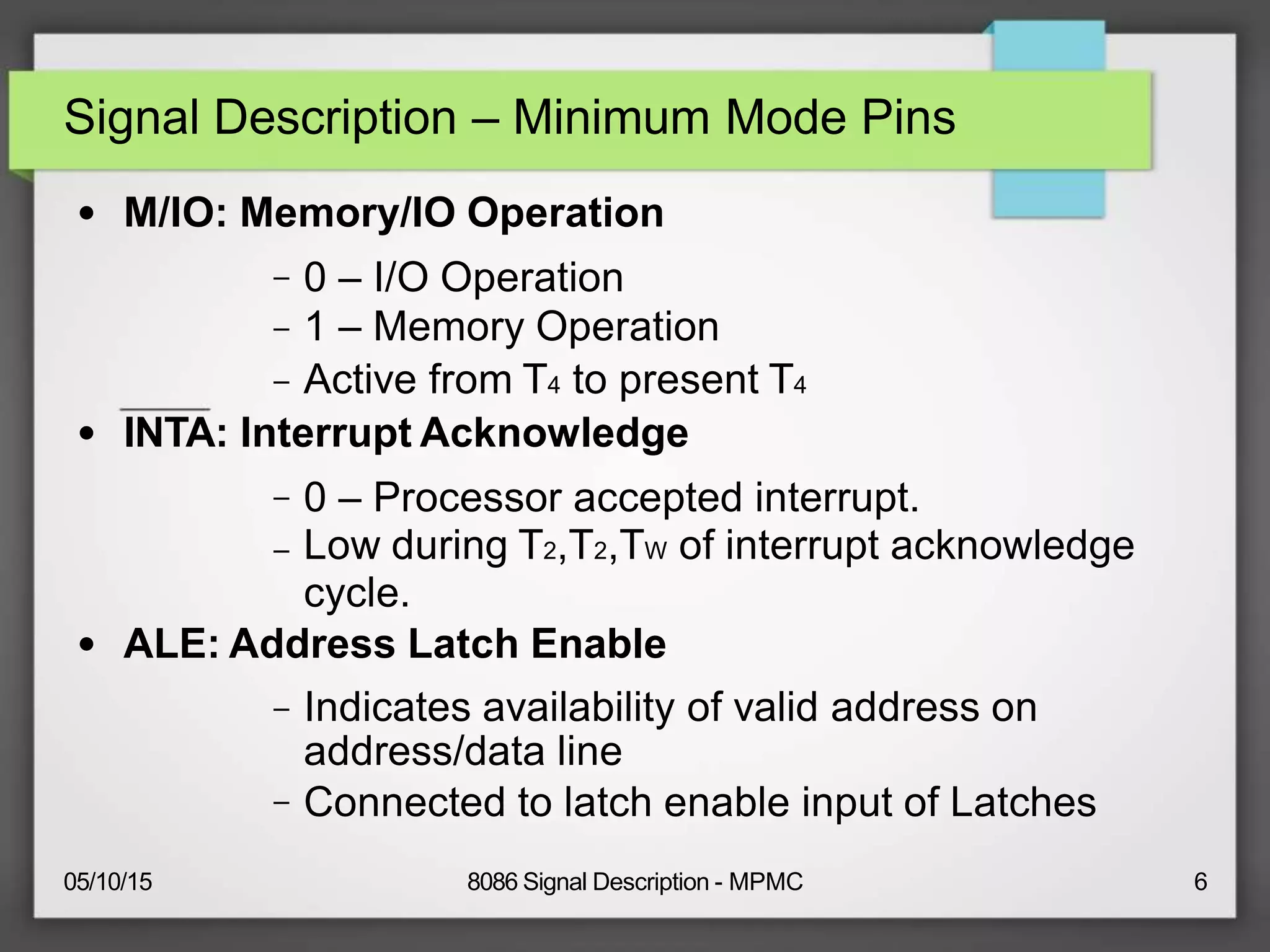

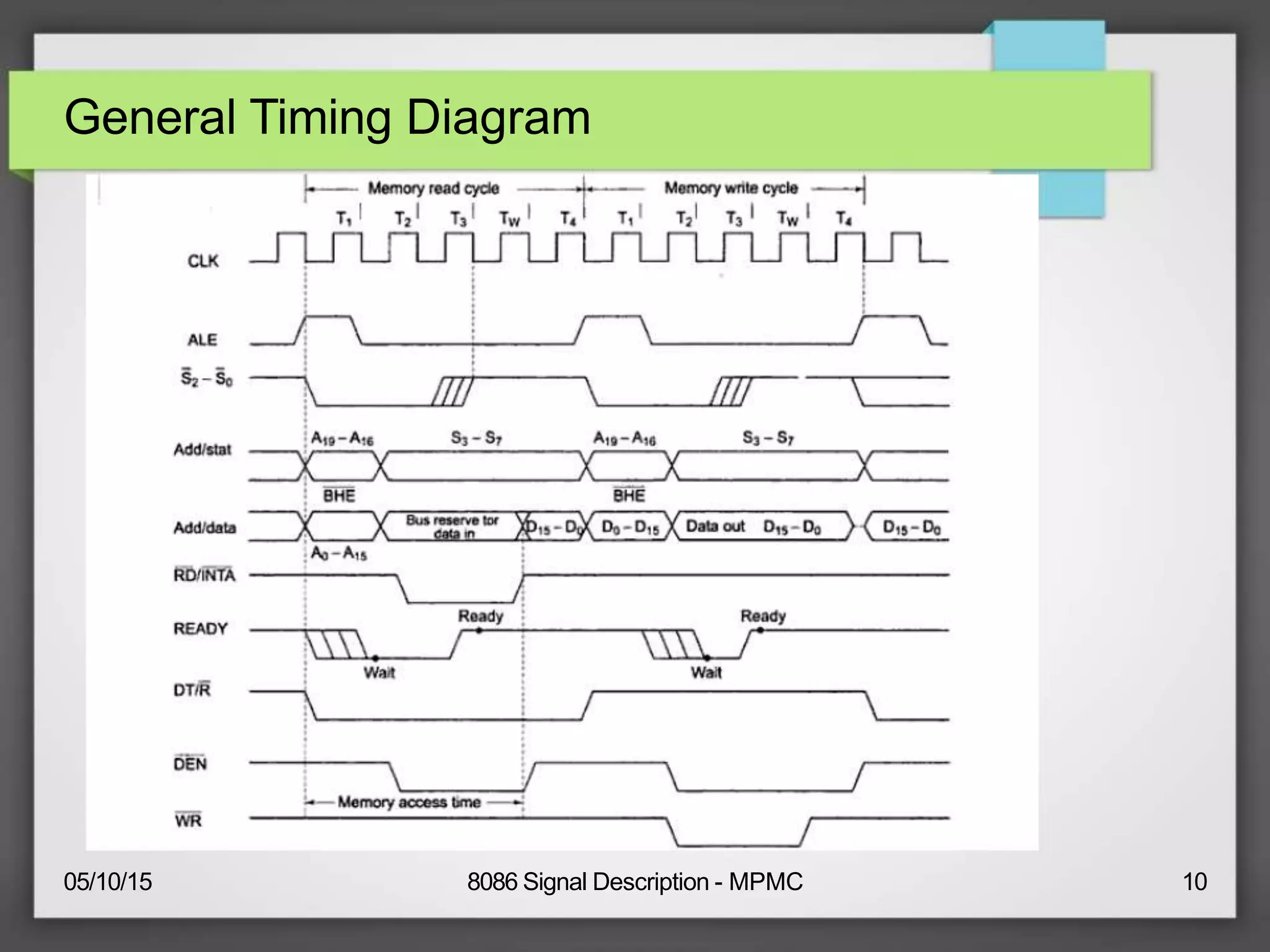

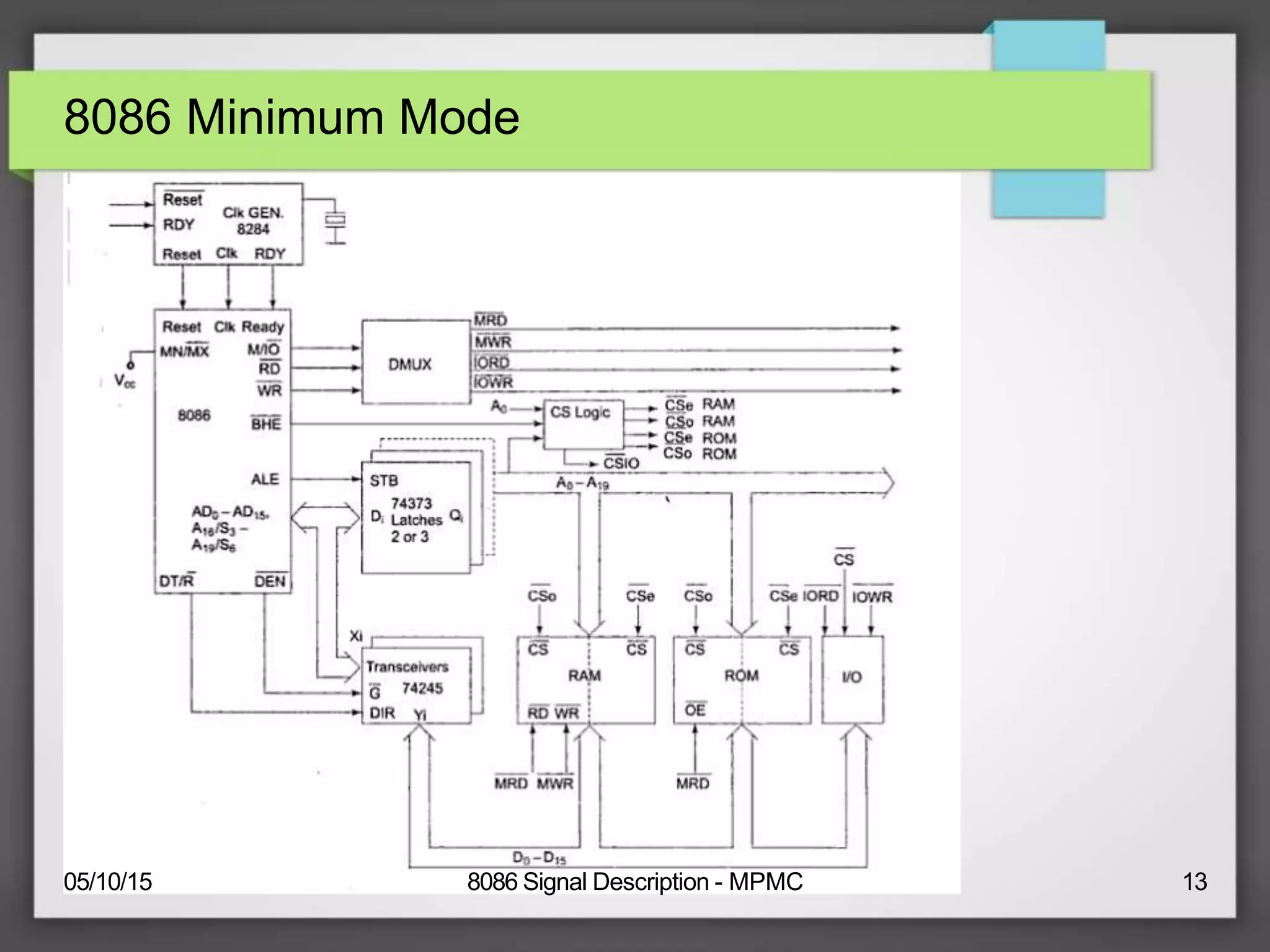

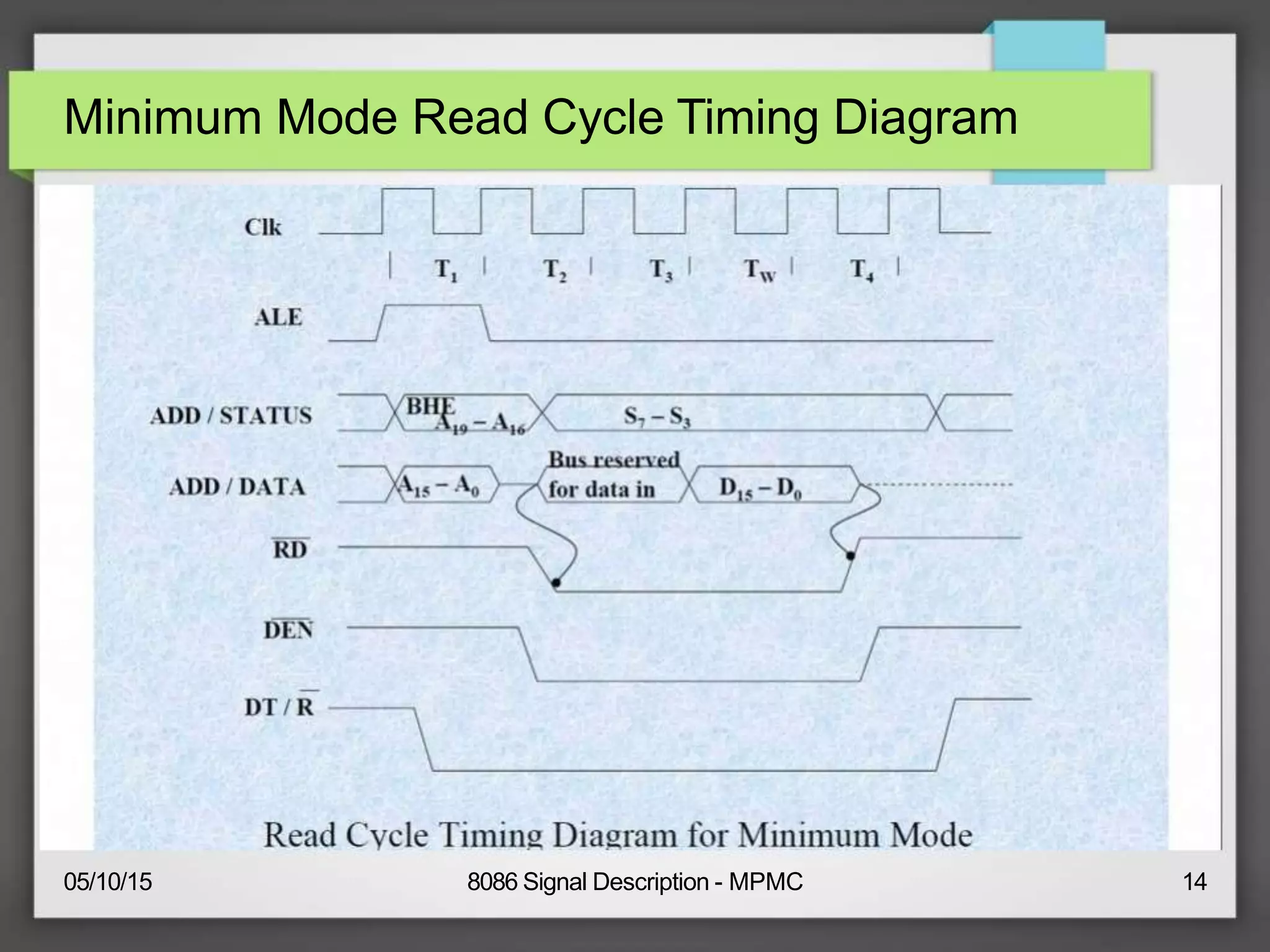

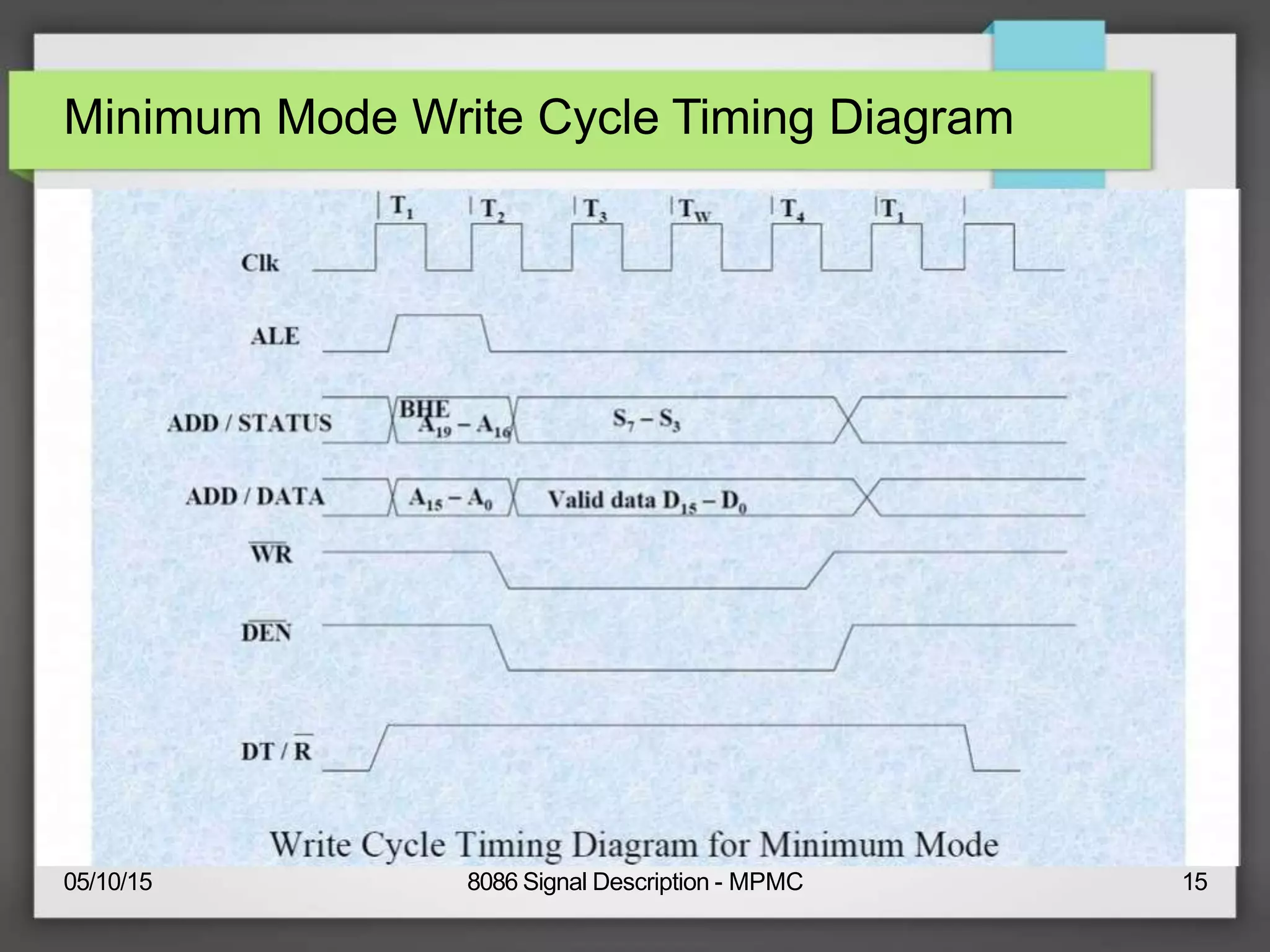

The document describes the signals of the 8086 microprocessor. It discusses the address/data and address/status lines that are time multiplexed. It explains the functions of signals like AD0-AD15, A16/S3-A19/S6, S4-S7, RD, READY, INTR, NMI, RESET, CLK and others. It provides timing diagrams for memory read and write cycles in minimum and maximum mode. It also discusses the different modes of operation like single processor mode and multi-processor mode.