Embed presentation

Download as PDF, PPTX

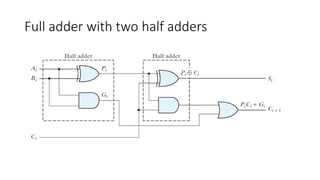

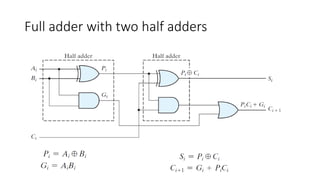

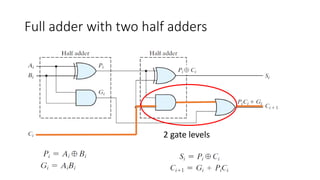

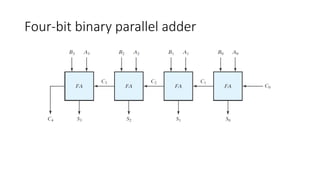

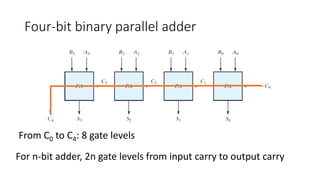

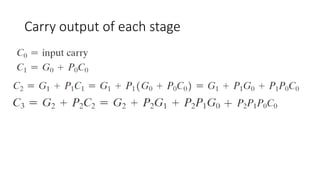

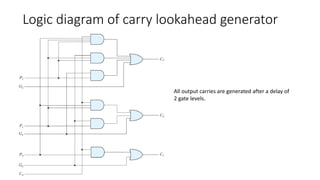

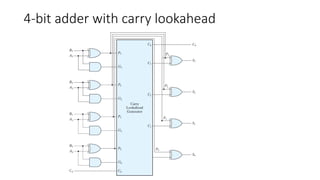

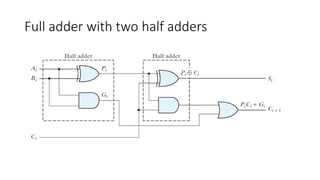

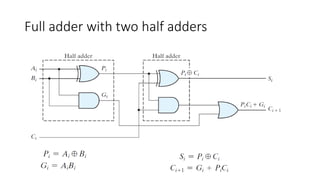

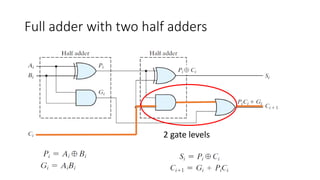

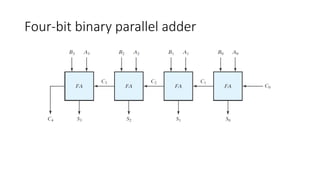

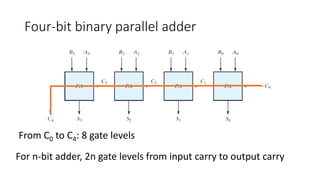

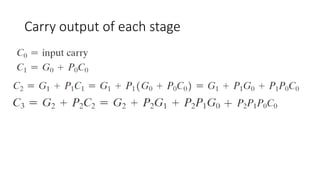

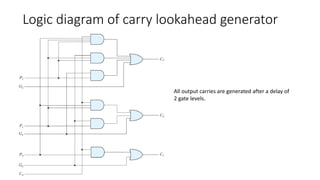

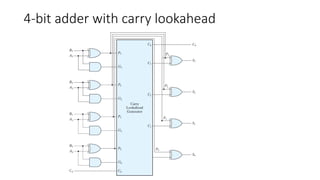

The document discusses the carry lookahead adder, which reduces carry propagation time in multi-bit addition. It does this through generating all carry outputs after just 2 gate delays, as opposed to the standard n gate delays of a ripple carry adder. Specifically, it mentions that a carry lookahead adder uses full adders with half adders to generate carries, and shows the logic diagram for a 4-bit adder with carry lookahead. The summary provided defines the carry lookahead adder and notes that its main advantage is improved speed over standard adders, though it has more complex circuits for larger bit sizes.