Cad for vlsi design june2013 (1)

•

2 likes•4,055 views

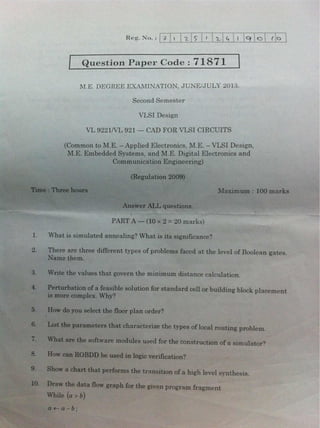

This document contains 10 questions related to VLSI design and CAD for VLSI circuits. The questions cover topics such as simulated annealing, Boolean gate problems, parameters for floor planning and local routing, software modules for simulation, use of ROBDD in logic verification, high level synthesis, and data flow graphs.

Report

Share

Report

Share

Download to read offline

Recommended

Assignment premier academic writing agency with industry

Hello Sir

We are a premier academic writing agency with industry partners in UK, Australia and Middle East and over 15 years of experience. We are looking to establish long-term relationships with industry partners and would love to discuss this opportunity further with you.

Thanks & Regards

visit our website.

www.onlineassignmenthelp.com.au

www.freeassignmenthelp.com

www.btechndassignment.cheapassignmenthelp.co.uk

www.cheapassignmenthelp.com

www.cheapassignmenthelp.co.uk/

http://www.cheapassignmenthelp.net/

Recommended

Assignment premier academic writing agency with industry

Hello Sir

We are a premier academic writing agency with industry partners in UK, Australia and Middle East and over 15 years of experience. We are looking to establish long-term relationships with industry partners and would love to discuss this opportunity further with you.

Thanks & Regards

visit our website.

www.onlineassignmenthelp.com.au

www.freeassignmenthelp.com

www.btechndassignment.cheapassignmenthelp.co.uk

www.cheapassignmenthelp.com

www.cheapassignmenthelp.co.uk/

http://www.cheapassignmenthelp.net/

Digital Signals and Systems (April – 2017) [Question Paper | CBSGS: 75:25 Pat...

Digital Signals and Systems (April – 2017) [Question Paper | CBSGS: 75:25 Pat...Mumbai B.Sc.IT Study

Digital Signals and Systems (April – 2017) [Question Paper | CBSGS: 75:25 Pattern]

april - 2017, april - 2016, april - 2015, april - 2014, april - 2013, october - 2017, october - 2016, october - 2015, october - 2014, may - 2016, may - 2017, december - 2017, 75:25 pattern, 60:40 pattern, revised course, old course, mumbai bscit study, mumbai university, bscit semester vi, bscit question paper, old question paper, previous year question paper, semester vi question paper, question paper, CBSGS, IDOL, kamal t, internet technology, digital signals and systems, data warehousing, ipr and cyber laws, project management, geographic information systemDigital Signals and Systems (October – 2016) [Question Paper | IDOL: Revised ...

Digital Signals and Systems (October – 2016) [Question Paper | IDOL: Revised ...Mumbai B.Sc.IT Study

Data Warehousing (April – 2016) [Question Paper | CBSGS: 75:25 Pattern]

april - 2017, april - 2016, april - 2015, april - 2014, april - 2013, october - 2017, october - 2016, october - 2015, october - 2014, may - 2016, may - 2017, december - 2017, 75:25 pattern, 60:40 pattern, revised course, old course, mumbai bscit study, mumbai university, bscit semester vi, bscit question paper, old question paper, previous year question paper, semester vi question paper, question paper, CBSGS, IDOL, kamal t, internet technology, digital signals and systems, data warehousing, ipr and cyber laws, project management, geographic information systemControl Systems

Introduction to Block Diagram Reduction Techniques

Block Diagram Reduction rules

Feed Back Control System

Examples

Directed Acyclic Graph Representation of basic blocks

Directed Acyclic Graph Representation of basic blocks is the most important topic of compiler design.This will help for student studying in master degree in computer science.

Webinar on Graph Neural Networks

We present Graph Convolutional Networks that, unlike classic DL models, allow supervised learning by exploiting both the single node features and its relationships with the others within the network.

Non Deterministic and Deterministic Problems

Few NP and P problems are discussed with good animation for better and faster understanding the algorithm

Design of Reversible Sequential Circuit Using Reversible Logic Synthesis

Reversible logic is one of the most vital issue at present time and it has different areas for its application, those are low power CMOS, quantum computing, nanotechnology, cryptography, optical computing, DNA computing, digital signal processing (DSP), quantum dot cellular automata, communication, computer graphics. It is not possible to realize quantum computing without implementation of reversible logic. The main purposes of designing reversible logic are to decrease quantum cost, depth of the circuits and the number of garbage outputs. In this paper, we have proposed a new reversible gate. And we have designed RS flip flop and D flip flop by using our proposed gate and Peres gate. The proposed designs are better than the existing proposed ones in terms of number of reversible gates and garbage outputs. So, this realization is more efficient and less costly than other realizations.

Deep single view 3 d object reconstruction with visual hull

The presentation slide of aaai'19 paper "Deep Single-View 3D Object Reconstruction with Visual Hull Embedding"

Computer Graphics and Multimedia Techniques Paper (RTU VI Semester)

FellowBuddy.com is an innovative platform that brings students together to share notes, exam papers, study guides, project reports and presentation for upcoming exams.

We connect Students who have an understanding of course material with Students who need help.

Benefits:-

# Students can catch up on notes they missed because of an absence.

# Underachievers can find peer developed notes that break down lecture and study material in a way that they can understand

# Students can earn better grades, save time and study effectively

Our Vision & Mission – Simplifying Students Life

Our Belief – “The great breakthrough in your life comes when you realize it, that you can learn anything you need to learn; to accomplish any goal that you have set for yourself. This means there are no limits on what you can be, have or do.”

Like Us - https://www.facebook.com/FellowBuddycom

Weakly supervised semantic segmentation of 3D point cloud

Slide for study session given by Dr. Daisuke Sato at Arithmer inc.

It is a summary of methods for semantic segmentation for 3D pointcloud using 2D weakly-supervised learning.

Arithmer株式会社は東京大学大学院数理科学研究科発の数学の会社です。私達は現代数学を応用して、様々な分野のソリューションに、新しい高度AIシステムを導入しています。AIをいかに上手に使って仕事を効率化するか、そして人々の役に立つ結果を生み出すのか、それを考えるのが私たちの仕事です。

Arithmer began at the University of Tokyo Graduate School of Mathematical Sciences. Today, our research of modern mathematics and AI systems has the capability of providing solutions when dealing with tough complex issues. At Arithmer we believe it is our job to realize the functions of AI through improving work efficiency and producing more useful results for society.

Dijkstra algorithm a dynammic programming approach

A presentation on Dijkstra Algorithm for my Algorithm class

Application of Dijkstra Algorithm in Robot path planning

Application of Dijkstra Algorithm in Robot path planning

More Related Content

What's hot

Digital Signals and Systems (April – 2017) [Question Paper | CBSGS: 75:25 Pat...

Digital Signals and Systems (April – 2017) [Question Paper | CBSGS: 75:25 Pat...Mumbai B.Sc.IT Study

Digital Signals and Systems (April – 2017) [Question Paper | CBSGS: 75:25 Pattern]

april - 2017, april - 2016, april - 2015, april - 2014, april - 2013, october - 2017, october - 2016, october - 2015, october - 2014, may - 2016, may - 2017, december - 2017, 75:25 pattern, 60:40 pattern, revised course, old course, mumbai bscit study, mumbai university, bscit semester vi, bscit question paper, old question paper, previous year question paper, semester vi question paper, question paper, CBSGS, IDOL, kamal t, internet technology, digital signals and systems, data warehousing, ipr and cyber laws, project management, geographic information systemDigital Signals and Systems (October – 2016) [Question Paper | IDOL: Revised ...

Digital Signals and Systems (October – 2016) [Question Paper | IDOL: Revised ...Mumbai B.Sc.IT Study

Data Warehousing (April – 2016) [Question Paper | CBSGS: 75:25 Pattern]

april - 2017, april - 2016, april - 2015, april - 2014, april - 2013, october - 2017, october - 2016, october - 2015, october - 2014, may - 2016, may - 2017, december - 2017, 75:25 pattern, 60:40 pattern, revised course, old course, mumbai bscit study, mumbai university, bscit semester vi, bscit question paper, old question paper, previous year question paper, semester vi question paper, question paper, CBSGS, IDOL, kamal t, internet technology, digital signals and systems, data warehousing, ipr and cyber laws, project management, geographic information systemControl Systems

Introduction to Block Diagram Reduction Techniques

Block Diagram Reduction rules

Feed Back Control System

Examples

Directed Acyclic Graph Representation of basic blocks

Directed Acyclic Graph Representation of basic blocks is the most important topic of compiler design.This will help for student studying in master degree in computer science.

Webinar on Graph Neural Networks

We present Graph Convolutional Networks that, unlike classic DL models, allow supervised learning by exploiting both the single node features and its relationships with the others within the network.

Non Deterministic and Deterministic Problems

Few NP and P problems are discussed with good animation for better and faster understanding the algorithm

Design of Reversible Sequential Circuit Using Reversible Logic Synthesis

Reversible logic is one of the most vital issue at present time and it has different areas for its application, those are low power CMOS, quantum computing, nanotechnology, cryptography, optical computing, DNA computing, digital signal processing (DSP), quantum dot cellular automata, communication, computer graphics. It is not possible to realize quantum computing without implementation of reversible logic. The main purposes of designing reversible logic are to decrease quantum cost, depth of the circuits and the number of garbage outputs. In this paper, we have proposed a new reversible gate. And we have designed RS flip flop and D flip flop by using our proposed gate and Peres gate. The proposed designs are better than the existing proposed ones in terms of number of reversible gates and garbage outputs. So, this realization is more efficient and less costly than other realizations.

Deep single view 3 d object reconstruction with visual hull

The presentation slide of aaai'19 paper "Deep Single-View 3D Object Reconstruction with Visual Hull Embedding"

Computer Graphics and Multimedia Techniques Paper (RTU VI Semester)

FellowBuddy.com is an innovative platform that brings students together to share notes, exam papers, study guides, project reports and presentation for upcoming exams.

We connect Students who have an understanding of course material with Students who need help.

Benefits:-

# Students can catch up on notes they missed because of an absence.

# Underachievers can find peer developed notes that break down lecture and study material in a way that they can understand

# Students can earn better grades, save time and study effectively

Our Vision & Mission – Simplifying Students Life

Our Belief – “The great breakthrough in your life comes when you realize it, that you can learn anything you need to learn; to accomplish any goal that you have set for yourself. This means there are no limits on what you can be, have or do.”

Like Us - https://www.facebook.com/FellowBuddycom

Weakly supervised semantic segmentation of 3D point cloud

Slide for study session given by Dr. Daisuke Sato at Arithmer inc.

It is a summary of methods for semantic segmentation for 3D pointcloud using 2D weakly-supervised learning.

Arithmer株式会社は東京大学大学院数理科学研究科発の数学の会社です。私達は現代数学を応用して、様々な分野のソリューションに、新しい高度AIシステムを導入しています。AIをいかに上手に使って仕事を効率化するか、そして人々の役に立つ結果を生み出すのか、それを考えるのが私たちの仕事です。

Arithmer began at the University of Tokyo Graduate School of Mathematical Sciences. Today, our research of modern mathematics and AI systems has the capability of providing solutions when dealing with tough complex issues. At Arithmer we believe it is our job to realize the functions of AI through improving work efficiency and producing more useful results for society.

Dijkstra algorithm a dynammic programming approach

A presentation on Dijkstra Algorithm for my Algorithm class

Application of Dijkstra Algorithm in Robot path planning

Application of Dijkstra Algorithm in Robot path planning

What's hot (20)

Digital Signals and Systems (April – 2017) [Question Paper | CBSGS: 75:25 Pat...

Digital Signals and Systems (April – 2017) [Question Paper | CBSGS: 75:25 Pat...

Digital Signals and Systems (October – 2016) [Question Paper | IDOL: Revised ...

Digital Signals and Systems (October – 2016) [Question Paper | IDOL: Revised ...

Directed Acyclic Graph Representation of basic blocks

Directed Acyclic Graph Representation of basic blocks

Design of Reversible Sequential Circuit Using Reversible Logic Synthesis

Design of Reversible Sequential Circuit Using Reversible Logic Synthesis

Deep single view 3 d object reconstruction with visual hull

Deep single view 3 d object reconstruction with visual hull

Computer Graphics and Multimedia Techniques Paper (RTU VI Semester)

Computer Graphics and Multimedia Techniques Paper (RTU VI Semester)

Weakly supervised semantic segmentation of 3D point cloud

Weakly supervised semantic segmentation of 3D point cloud

Dijkstra algorithm a dynammic programming approach

Dijkstra algorithm a dynammic programming approach

Application of Dijkstra Algorithm in Robot path planning

Application of Dijkstra Algorithm in Robot path planning

Similar to Cad for vlsi design june2013 (1)

Functional Verification of Large-integers Circuits using a Cosimulation-base...

Cryptography and computational algebra designs are complex systems based on modular arithmetic and build on multi-level modules where bit-width is generally larger than 64-bit. Because of their particularity, such designs pose a real challenge for verification, in part because large-integer‘s functions are not supported in actual hardware description languages (HDLs), therefore limiting the HDL testbench utility. In another hand, high-level verification approach proved its efficiency in the last decade over HDL testbench technique by raising the latter at a higher abstraction level. In this work, we propose a high-level platform to verify such designs, by leveraging the capabilities of a popular tool (Matlab/Simulink) to meet the requirements of a cycle accurate verification without bit-size restrictions and in multi-level inside the design architecture. The proposed high-level platform is augmented by an assertion-based verification to complete the verification coverage. The platform experimental results of the testcase provided good evidence of its performance and re-usability.

IRJET- Advanced Control Strategies for Mold Level Process

https://www.irjet.net/archives/V6/i3/IRJET-V6I3327.pdf

Anticipating Implementation-Level Timing Analysis for Driving Design-Level De...

Presentation of the speech for the 1st International Workshop on

Modelling in Automotive Software Engineering at Models 2015 held in Ottawa, Canada

Similar to Cad for vlsi design june2013 (1) (20)

Solid state device modeling and simulation jan2013 (1)

Solid state device modeling and simulation jan2013 (1)

Functional Verification of Large-integers Circuits using a Cosimulation-base...

Functional Verification of Large-integers Circuits using a Cosimulation-base...

IRJET- Advanced Control Strategies for Mold Level Process

IRJET- Advanced Control Strategies for Mold Level Process

Anticipating Implementation-Level Timing Analysis for Driving Design-Level De...

Anticipating Implementation-Level Timing Analysis for Driving Design-Level De...

More from SRI TECHNOLOGICAL SOLUTIONS

More from SRI TECHNOLOGICAL SOLUTIONS (20)

Request for-new-pan-card-or-and-changes-or-correction-in-pan-data-form

Request for-new-pan-card-or-and-changes-or-correction-in-pan-data-form

Cad for vlsi design june2013 (1)

- 1. I Question Paper Code; 71871 M.E. DEGREE EXAMINATION, JUNE/JULY 2013. Second Semester VLSI Design VL 9221/VL 921- CAD FOR VLSI CIRCUITS (Common to M.E. - Applied Electronics, M.E. - VLSI Design, l1.E. Embedded Systems, and M.E. Digital Electronics and Comm unication Engineering) (Regulation 2009) Time : Three hours Maximum: 100 marks Answer ALL questions. PART A - (10 x 2 = 20 marks) 1. What is simulated annealing? What is its significance? 2. There are three different types of problems faced at the level of Boolean gates. Name them. 3. Write the values that govern the minimum distance calculation. 4. Perturbation of a feasible solution for standard cell or building block placement is more complex. Why? 5. How do you select the floor plan order? 6. List the parameters that characterize the types of local routing problem.' 7. What are the software modules used for the construction of a simulator? 8. How can ROBDD be used in logic verification? 9. Show a chart that performs the transition of a high level synthesis. 10. Draw the data flow graph for the given program fragment While (a >b) a,.......a-b;