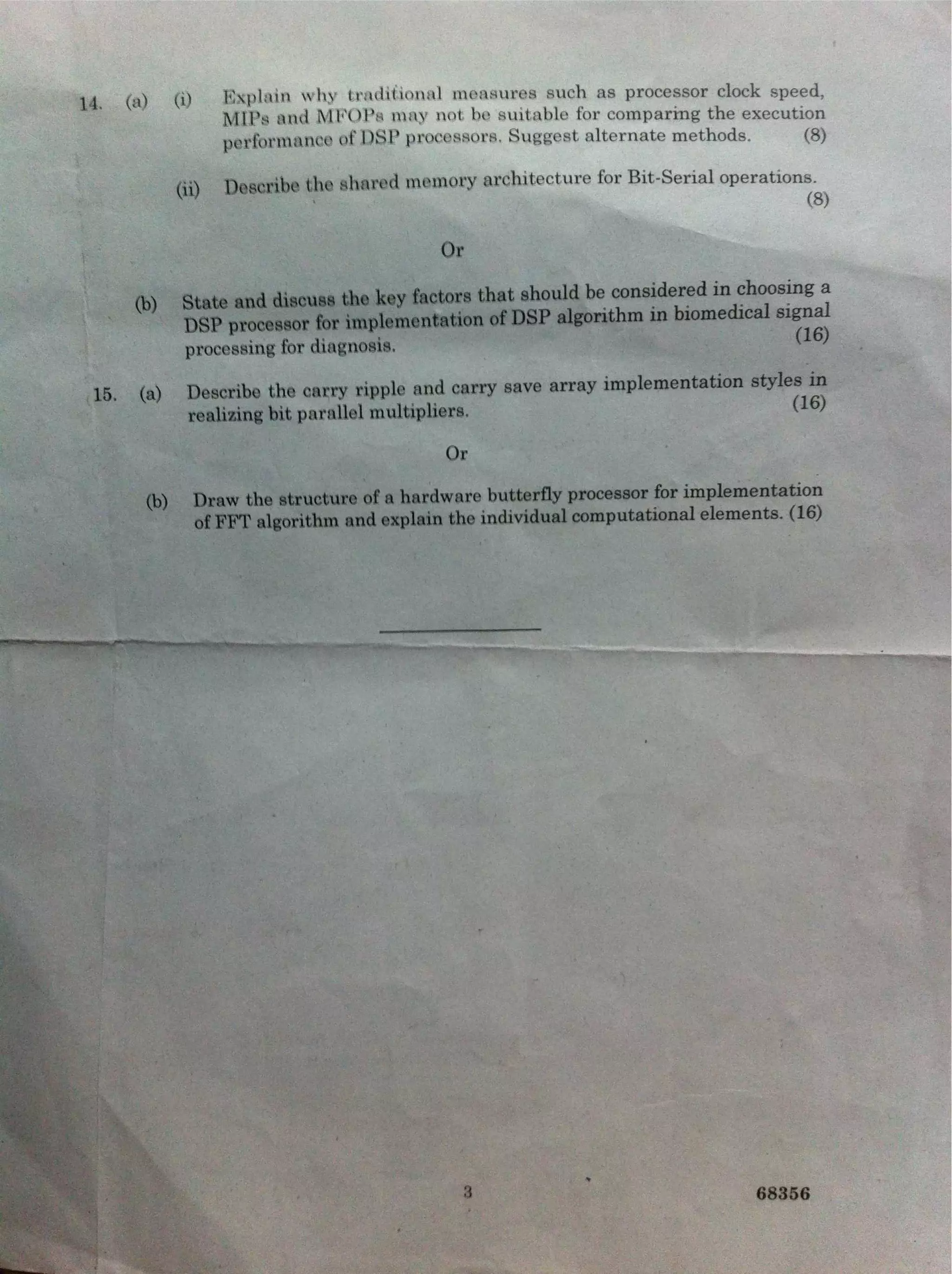

This document contains two questions about digital signal processing. The first question asks to explain why traditional measures like clock speed and MOPS may not be suitable for comparing ASP processors, and to suggest alternative methods. It also asks to describe the shared memory architecture for bit-serial operations. The second question asks to state and discuss the key factors to consider when choosing a DSP processor for implementing DSP algorithms in biomedical signal processing for diagnosis.