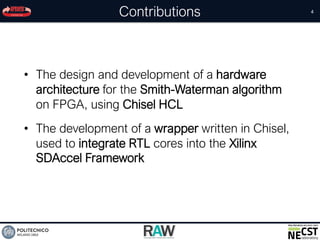

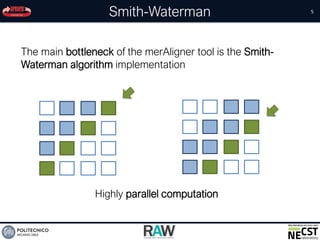

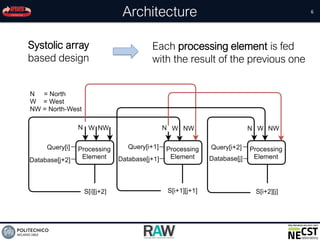

The document presents a hardware architecture for the Smith-Waterman algorithm implemented on FPGA using Chisel HCL, aimed at improving performance and power efficiency for genomic sequence alignment. It discusses the limitations of software solutions and introduces the Meraligner tool that achieves high performance and low power consumption. Key performance metrics demonstrate significant speedup and efficiency improvements compared to traditional implementations.

![Results 7

Read Reference

Frequency

[MHz]

Performance

[GCUPS]

Speed up

Performance

Efficiency

[GCUPS/W]

Speed up

Power efficiency

128[*] 1024 - 3.87 - 0.0165 -

128 1024 150 3.542 0.91X 0.141 8.54X

128 2048 140 5.616 1.45X 0.224 14.35X

128 4096 180 6.529 1.68X 0.261 15.81X

128 16384 110 11.443 2.84X 0.457 27.69X

256 1024 160 6.123 1.58X 0.244 14.78X

256 2048 160 8.393 2.16X 0.335 20.30X

256 4096 130 15.225 3.93X 0.609 36.90X

256 16384 140 27.312 7.05X 1.092 66.18X

[*] State of the Art Smith-Waterman software implementation](https://image.slidesharecdn.com/swraw-180522012152/85/A-Parallel-Energy-Efficient-Hardware-Architecture-for-the-merAligner-on-FPGA-using-Chisel-HCL-8-320.jpg)

![Concluding Remarks 8

Read Reference

Frequency

[MHz]

Performance

[GCUPS]

Speed up

Performance

Efficiency

[GCUPS/W]

Speed up

Power efficiency

128[*] 1024 - 3.87 - 0.0165 -

128 1024 150 3.542 0.91X 0.141 8.54X

128 2048 140 5.616 1.45X 0.224 14.35X

128 4096 180 6.529 1.68X 0.261 15.81X

128 16384 110 11.443 2.84X 0.457 27.69X

256 1024 160 6.123 1.58X 0.244 14.78X

256 2048 160 8.393 2.16X 0.335 20.30X

256 4096 130 15.225 3.93X 0.609 36.90X

256 16384 140 27.312 7.05X 1.092 66.18X

[*] State of the Art Smith-Waterman software implementation

Thank you for your attention!

Lorenzo Di Tucci, Marco Santambrogio {lorenzo.ditucci, marco.santambrogio}@polimi.it

Alessandro Comodi, Davide Conficconi {alessandro.comodi,davide.conficconi}@mail.polimi.it

Steven Hofmeyr, David Donofrio {shofmeyr, ddonofrio}@lbl.gov

speaker: Alessandro Comodi

Hardware architecture for the acceleration of the

Smith-Waterman step of the merAligner on FPGA

using Chisel HCL](https://image.slidesharecdn.com/swraw-180522012152/85/A-Parallel-Energy-Efficient-Hardware-Architecture-for-the-merAligner-on-FPGA-using-Chisel-HCL-9-320.jpg)