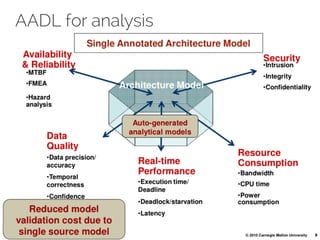

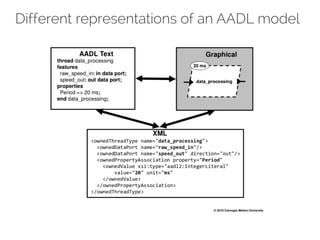

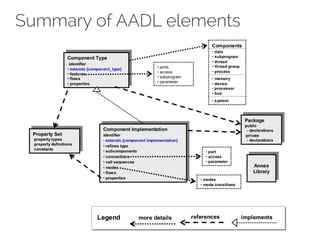

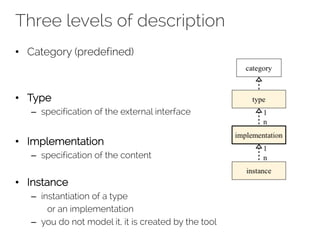

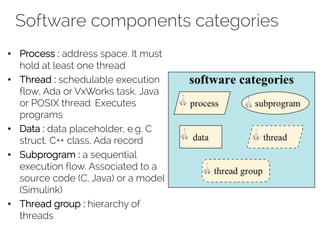

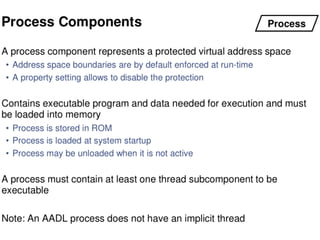

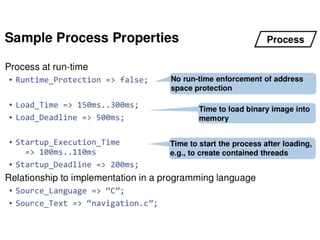

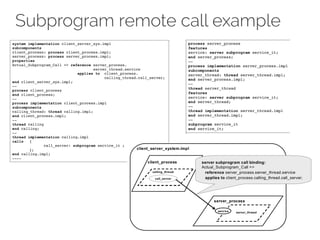

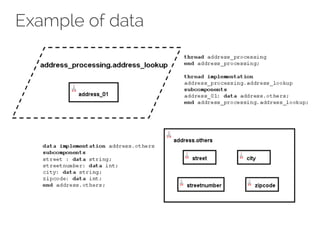

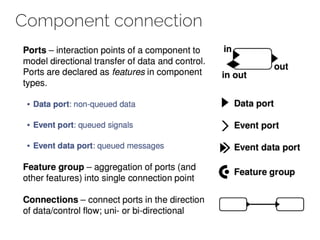

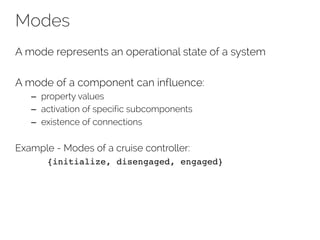

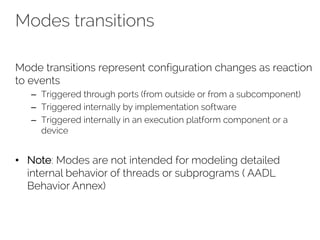

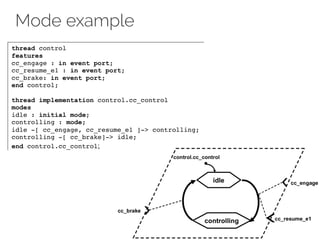

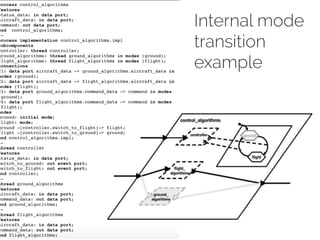

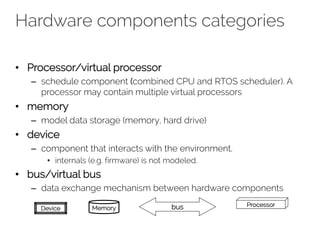

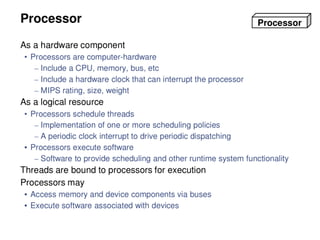

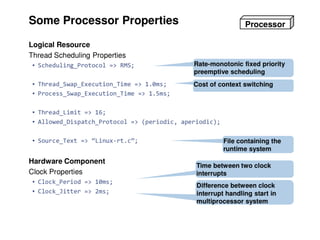

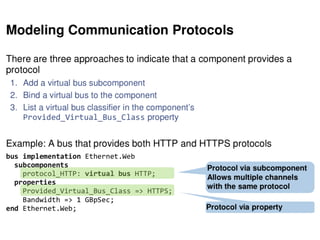

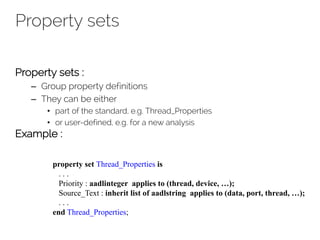

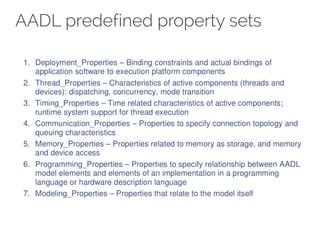

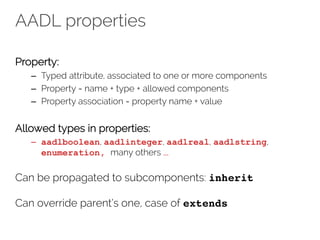

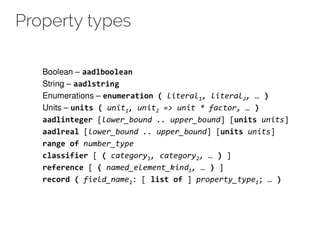

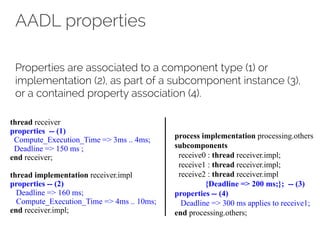

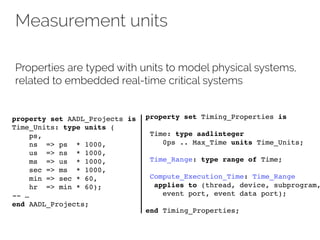

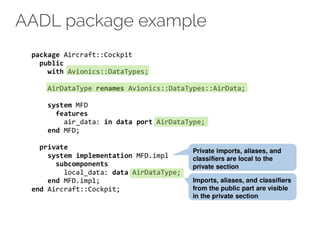

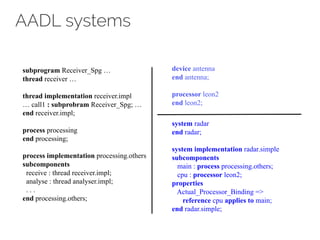

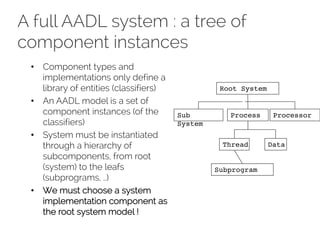

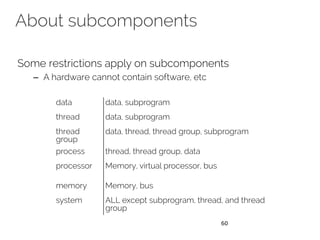

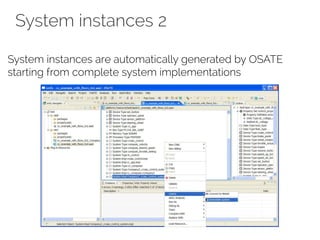

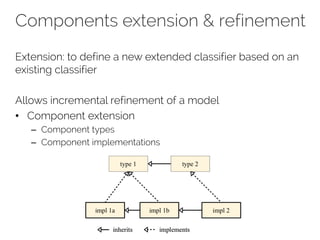

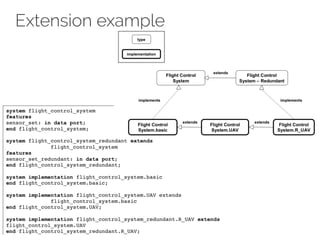

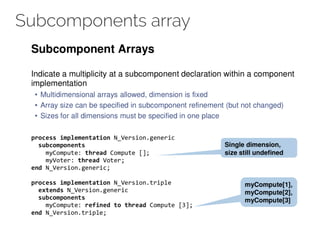

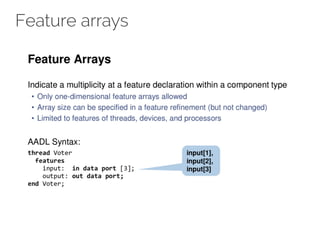

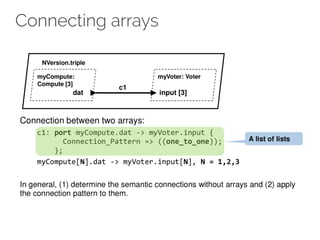

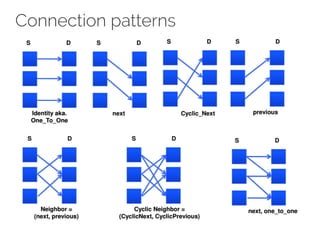

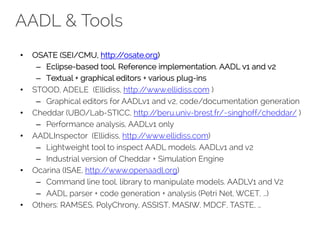

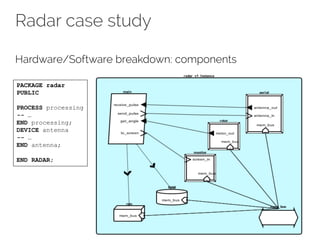

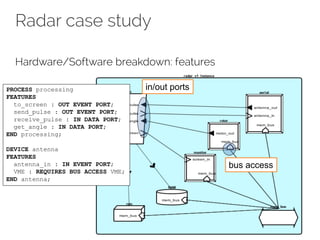

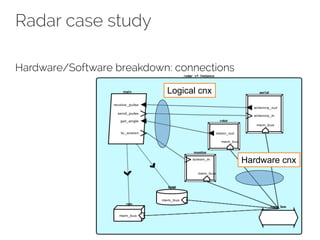

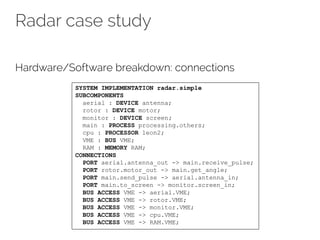

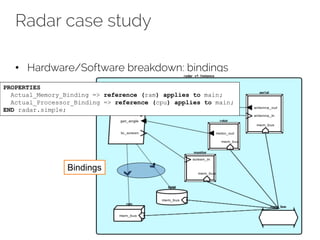

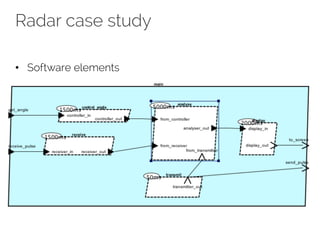

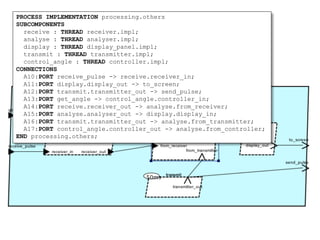

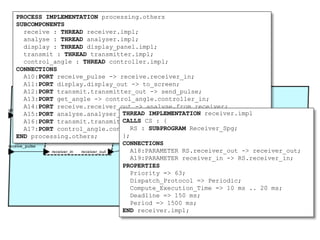

The document outlines a lecture on the Architecture Analysis & Design Language (AADL), focusing on its core syntax, semantics, and modeling constructs, including software and execution platform components. It presents detailed examples of AADL models, particularly relating to a radar system, discussing components like processes, threads, data, and modes of operation. The document emphasizes AADL's utility for architectural descriptions of large-scale systems and references various tools available for AADL modeling and analysis.

![Suggested readings

1. The SAE Architecture Analysis & Design Language (AADL) Standard.

Peter H. Feiler, January 2008. [Introduction to the language]

2. The Architecture Analysis & Design Language (AADL): An

Introduction, Peter H. Feiler David P. Gluch John J. Hudak, February

2006. [Use this as reference manual]

3. OSATE plugin: SEI validation plugins. SEI. [AADL analysis in general]

4. Developing AADL Models for Control Systems: A Practitioner’s

Guide. John Hudak Peter Feiler. July 2007. [Flow latency analysis]

5. http://www.informit.com/articles/article.aspx?p=1959953

[Simple running example]](https://image.slidesharecdn.com/ivano04saaadl-171122165132/85/2017-2018-AADL-Architecture-Analysis-and-Design-Language-82-320.jpg)