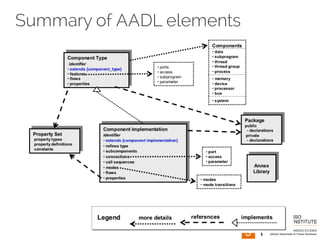

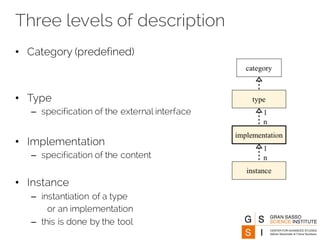

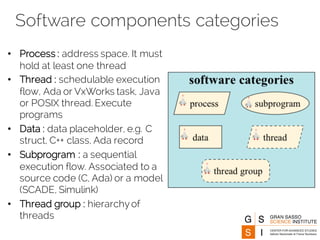

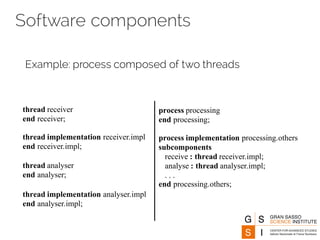

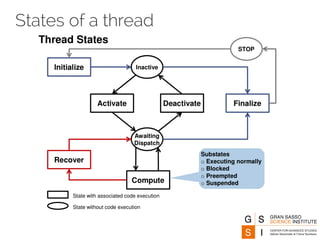

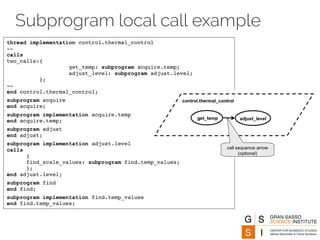

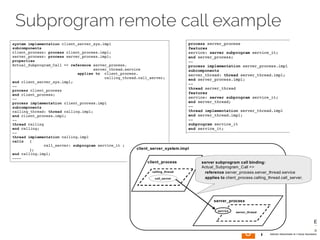

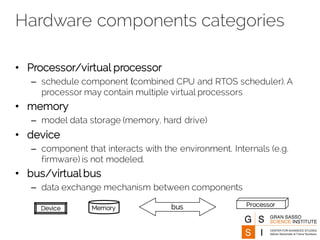

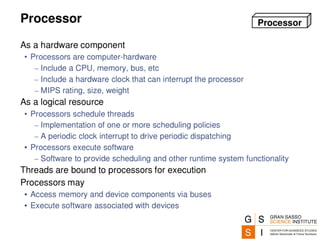

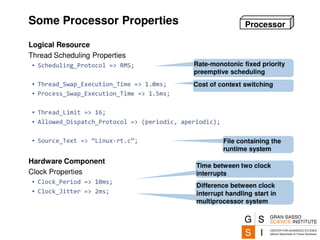

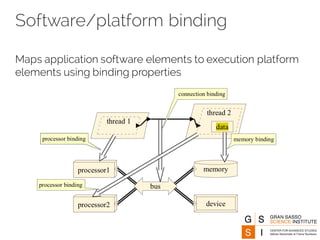

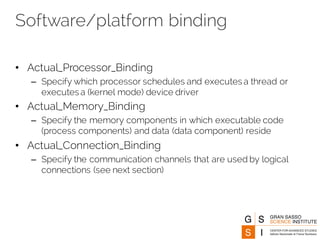

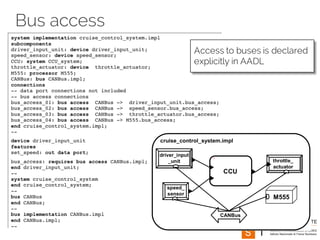

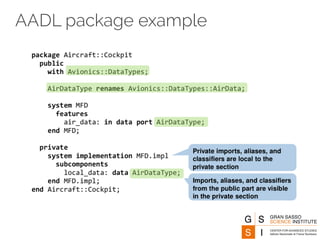

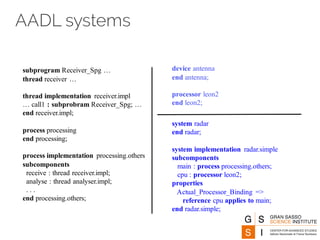

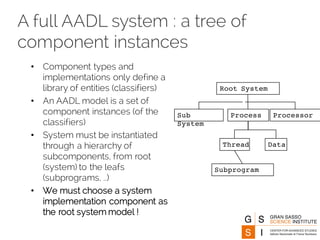

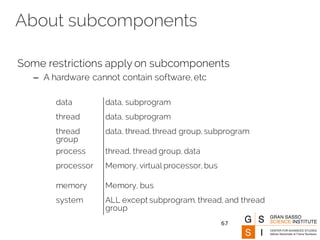

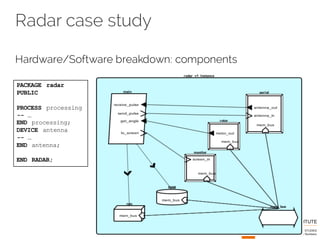

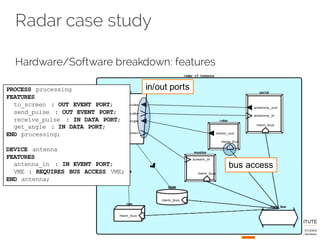

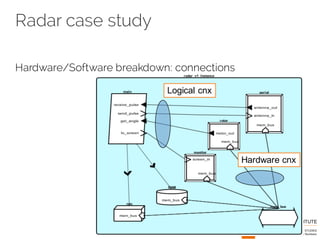

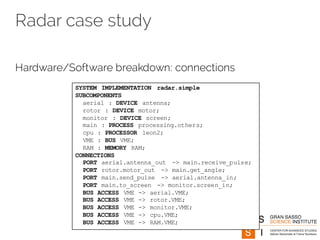

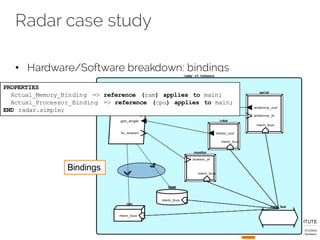

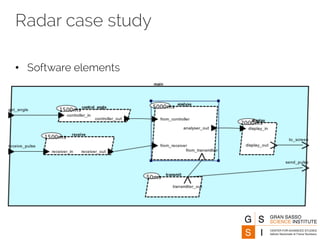

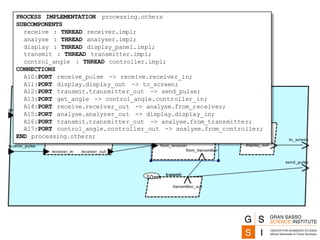

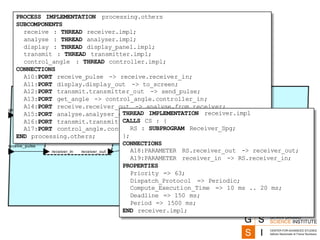

This document introduces the Architecture Analysis and Design Language (AADL) and uses a radar system as an example to demonstrate AADL modeling concepts. It breaks down the radar system into hardware and software components, showing how to model processes, threads, devices, and connections between them. It also models the deployment of software processes onto hardware processors and memories. The example illustrates key AADL concepts like components, features, connections, bindings, and properties.

![Suggested readings

1. The SAE Architecture Analysis & Design Language (AADL) Standard.

Peter H. Feiler, January 2008. [Introduction to the language]

2. The Architecture Analysis & Design Language (AADL): An

Introduction, Peter H. Feiler David P. Gluch John J. Hudak, February

2006. [Use this as reference manual]

3. OSATE plugin: SEI validation plugins. SEI. [Analysis in general]

4. Developing AADL Models for Control Systems: A Practitioner’s

Guide. John Hudak Peter Feiler. July 2007. [Flowlatency analysis]

5. http://www.informit.com/articles/article.aspx?p=1959953

[Simple running example]](https://image.slidesharecdn.com/07saaadl-151204104852-lva1-app6891/85/2015-2016-AADL-Architecture-Analysis-and-Design-Language-90-320.jpg)