CO&A_Modulektyukkhghhkkkkkkkjg_1 PPT.pdf

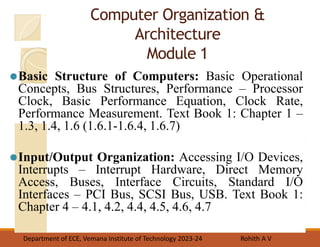

- 1. Computer Organization & Architecture Module 1 ⚫Basic Structure of Computers: Basic Operational Concepts, Bus Structures, Performance – Processor Clock, Basic Performance Equation, Clock Rate, Performance Measurement. Text Book 1: Chapter 1 – 1.3, 1.4, 1.6 (1.6.1-1.6.4, 1.6.7) ⚫Input/Output Organization: Accessing I/O Devices, Interrupts – Interrupt Hardware, Direct Memory Access, Buses, Interface Circuits, Standard I/O Interfaces – PCI Bus, SCSI Bus, USB. Text Book 1: Chapter 4 – 4.1, 4.2, 4.4, 4.5, 4.6, 4.7 Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 2. BasicTerminology ◦ A Electronic calculating device that accepts digitized input, processes data , stores data, and produces output, all according to a series of stored instructions. ⚫ Computer ⚫ Software ◦ A computer program that tells the computer how to perform particular tasks. ⚫ Hardware ◦ Includes the electronic and mechanical devices that process the data; refers to the computer as well as peripheral devices. ⚫ Peripheral devices ◦ Used to expand the computer’s input, output and storage capabilities. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 3. FUNCTIONAL UNITS of 5 functionally ⚫ A computer consists independent main parts: 1) Input 2) Memory 3) Arithmetic & Logic Unit 4) Output 5) Control units. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 4. FUNCTIONAL UNITS Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 5. 1.3 Basic operational concepts ⚫ Computer is governed (be in control) by instructions. ⚫ To perform a given task an appropriate list of instructions (program) has to be stored in the memory. ⚫ Individual instructions are brought from the memory into the processor, which executes the specified operations. ⚫ Data to be used as operands (Inputs) are also stored in the memory. ⚫ Examples: - Add LOCA, R0 ⚫ This instruction adds the operand at memory location LOCA, to operand in register R0 & places the sum into register R0. ⚫ If LOCA value is 10 and R0 value is 05, then 10+5=15 is stored in register R0. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 6. Basic operational concepts This instruction requires the performance of several steps, 1. First the instruction is fetched from the memory into the processor. 2. The operand (value) at LOCA is fetched and added to the contents of R0. 3. Finally the resulting sum is stored in the register R0. Note: The value at LOCA is preserved where the value at R0 is overwritten. • The above instruction can be realized by the two- instruction sequence as • Note: The value at LOCA is only preserved where the value at R0 and R1 is overwritten. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V Load LOCA, R1 Add R1, R0

- 7. • Fig shows how the memory and processor can be connected. • It also contains ALU & Control circuitry along with that processor contains number of registers used for several different purpose. Connections between the processor & the memory Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 8. ⚫ The Instruction Register (IR):- ⚫ Holds the instructions that is currently being executed. ⚫ Its output is available for the control circuits which generates the timing signals that control the various processing elements in one execution of instruction. ⚫ The Program Counter (PC):- This is another specialized register that keeps track of execution of a program. ⚫ It contains the memory address of the next instruction to be fetched and executed. ⚫ Along with IR and PC, there are n-General Purpose Registers R0 through Rn-1. ⚫ The othertwo registers which facilitate communication with memory are: - 1. MAR – (Memory Address Register):- It holds the address of the location to be accessed. 2. MDR – (Memory Data Register):- It contains the data to be written into or read out of the address location. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 9. Basic operational concepts Typical Operating steps are 1. Programs reside in the memory & usually get these through the I/P unit. 2. Execution of the program starts when the PC is set to point at the first instruction of the program. 3. Contents of PC are transferred to MAR and a Read Control Signal is sent to the memory. 4. After the time required to access the memory elapses, the address word is read out of the memory and loaded into the MDR. 5. Now contents of MDR are transferred to the IR & now the instruction is ready to be decoded and executed. 6. If the instruction involves an operation by the ALU, it is necessary to obtain the required operands. 7. An operand in the memory is fetched by sendingits address to MAR & Initiating a read cycle. 8. When the operand has been read from the memory to the MDR, it is transferred from MDR to the ALU. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 10. Basic operational concepts 9. After one or two such repeated cycles, the ALU can perform the desired operation. 10. If the result of this operation is to be stored in the memory, the result is sent to MDR. 11. Address of location where the result is stored is sent to MAR & a write cycle is initiated. 12. The contents of PC are incremented so that PC points to the next instruction that is to be executed. ⚫ Normal execution of a program may be preempted (temporarily interrupted) if some devices require urgent servicing, to do this one device raises an Interrupt signal. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 11. Basic operational concepts ⚫ An Interrupt is a request signal from an I/O device for service by the processor. ⚫ The processor provides the requested service by executing an appropriate interrupt service routine. ⚫ The Diversion may change the internal stage of the processor its state must be saved in the memory location before interruption. ⚫ When the interrupt-routine service is completed the state of the processor is restored so that the interrupted program may continue. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 12. 1.4 Bus Structure ⚫ The simplest and most common way of interconnecting various parts of the computer is through wires. ⚫ To achieve a good speed of operation, a computer must be organized so that all its units can handle one full word of data at a given time. ⚫ A group of lines (wires) that serve as a connecting port for several devices is called a bus. ⚫ Buses can carry data, address as well as for control purpose also. ⚫ Simplest way to interconnect functional units to use the single bus as shown in the fig. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 13. Bus Structure Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 14. Bus Structure ⚫ Bus can be used for only one transfer at a time, only two units can actively use the bus at any given time. ⚫ Bus control lines determines the multiple requests for the bus usage. ⚫ Single bus structure is ⚫ Low cost ⚫ Very flexible for attaching peripheral devices ⚫ Multiple bus structure increases the performance but also increases the cost significantly. ⚫ All the interconnected devices will not work with same speed & time. This can be avoided using cache registers (ie buffer registers). ⚫ Eg: Buffer Printer: Which stores the data to be printed and allows user to do other works in the PC. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 15. 1.6 Performance ⚫ The most important measure of the performance of a computer is how quickly it can execute programs. ⚫ The speed is directly related to the design of its hardware. ⚫ Since programs are written in high level language, that has to be converted into machine language instructions. ⚫ Program will execute faster, if the movement of instructions & data between main memory & the processor is minimized, which is achieved by using the cache memory. ⚫ Suppose a number of instructions are executed repeatedly for a short period of time as in a programming loop. ⚫ So these instructions are kept/made to be in the cache memory so that they can be fetched quicker to reduce the time. ⚫ Cache memory is a small sized type of memory that provide high speed data access to processor and stores frequently used data. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 16. Performance ⚫ Typically integrated onto the motherboard along with the processor. ⚫ Clock cycle is an important parameter that affects the processor performance. ⚫ This hardware comprises the processor and the memory (which includes the cache memory as part of the processor unit) which are usually connected by the bus as shown in the fig Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 17. Performance ⚫ Let us examine the flow of program instructions and data between the memory and the processor. ⚫ At the start of execution, all program instructions and the required data are stored in the main memory. ⚫ As the execution proceeds, instructions are fetched one by one over the bus into the processor, and a copy is placed in the cache . ⚫ Later if the same instruction or data item is needed a second time, it is read directly accessed from the cache. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 18. Performance Processor clock & Basic performance Equation: - ⚫ Processor circuits are controlled by a timing signal called clock. ⚫ The clock defines the regular time intervals called clock cycles. ⚫ To execute a machine instruction the processor divides its into several steps, each of which computed in one clock cycle. ⚫ The basic performance equation can be measured as where T=> processor time required to execute a program. N=> Program contain N machine level language instruction. S=> Average no. of basic steps needed to execute one instruction. R=> Clock rate == R=1/P where P is the Clock. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 19. Performance • To achieve high performance, T value has to be reduced which means reducing N & S and increasing R. • N can be reduced if the source program is completed with a fewer machine instruction. • S is reduced if the instruction have smaller no. of basic steps to perform. • Using a higher frequency clock increases the value of R. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 20. Performance PIPELINING & SUPERSCALAR OPERATION • Computer executes the instruction in sequence i,e. one by one. • Improvement in performance can be achieved by overlapping the execution of successive instructions • This technique is called as pipelining. • Consider the instruction Add R1,R2,R3 ;instruction 1 Move R4,R5 ;instruction 2 Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 21. Performance Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V Without Pipeline With Pipeline

- 22. Performance • 6 clock cycles are required to complete two operations without pipeline. • If we use pipelining & prefetching, only 4 cycles are required to complete same two operations. • While executing the Add instruction, the processor can read the Move instruction from memory. • If multiple instruction pipelines are implemented in the processor, multiple functional units can be used to execute different instructions parallelly. • This mode of operation is known as superscalar execution. Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 23. PERFORMANCE MEASUREMENT • Performance Measure is the time taken by a computer to execute a given benchmark. • SPEC selects & publishes the standard programs along with their test results for different application domains. (SPEC = System Performance Evaluation Corporation). • SPEC Rating is given by Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V

- 24. • If SPEC rating = 50, Then the computer under test is said to be 50 times as fast as reference-computer. • The test is repeated for all the programs in the SPEC suite. • Then, the geometric mean of the results is computed and given as Department of ECE, Vemana Institute of Technology 2023-24 Rohith A V PERFORMANCE MEASUREMENT