Tutorial10 solution

•

1 like•4,574 views

ESC201A Tutorials IIT KANPUR

Report

Share

Report

Share

Download to read offline

Recommended

Recommended

More Related Content

What's hot

What's hot (20)

Control Modelo de Referencia y Linealizacion po Realimentacion

Control Modelo de Referencia y Linealizacion po Realimentacion

Viewers also liked

Viewers also liked (9)

Hso201 a solutions to practice problem set 3-2015-16-ii

Hso201 a solutions to practice problem set 3-2015-16-ii

Similar to Tutorial10 solution

FSM, finite state machineLec16 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Fi...

Lec16 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Fi...Hsien-Hsin Sean Lee, Ph.D.

Similar to Tutorial10 solution (20)

Sequential Circuitsdddddddddddddddddsssssssssss-ppt.pptx

Sequential Circuitsdddddddddddddddddsssssssssss-ppt.pptx

ELN Presentation Add more information to your upload.pptx

ELN Presentation Add more information to your upload.pptx

Lec16 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Fi...

Lec16 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Fi...

Recently uploaded

Call girls in delhi ✔️✔️🔝 9953056974 🔝✔️✔️Welcome To Vip Escort Services In Delhi [ ]Noida Gurgaon 24/7 Open Sex Escort Services With Happy Ending ServiCe Done By Most Attractive Charming Soft Spoken Bold Beautiful Full Cooperative Independent Escort Girls ServiCe In All-Star Hotel And Home Service In All Over Delhi, Noida, Gurgaon, Faridabad, Ghaziabad, Greater Noida,

• IN CALL AND OUT CALL SERVICE IN DELHI NCR

• 3* 5* 7* HOTELS SERVICE IN DELHI NCR

• 24 HOURS AVAILABLE IN DELHI NCR

• INDIAN, RUSSIAN, PUNJABI, KASHMIRI ESCORTS

• REAL MODELS, COLLEGE GIRLS, HOUSE WIFE, ALSO AVAILABLE

• SHORT TIME AND FULL TIME SERVICE AVAILABLE

• HYGIENIC FULL AC NEAT AND CLEAN ROOMS AVAIL. IN HOTEL 24 HOURS

• DAILY NEW ESCORTS STAFF AVAILABLE

• MINIMUM TO MAXIMUM RANGE AVAILABLE.

Call Girls in Delhi & Independent Escort Service –

CALL GIRLS SERVICE DELHI NCR

Vip call girls in Delhi

Call Girls in Delhi, Call Girl Service 24×7 open

Call Girls in Delhi Best Delhi Escorts in Delhi

Low Rate Call Girls In Saket Delhi

X~CALL GIRLS IN Ramesh Nagar Metro

best Delhi call girls and Delhi escort service.

CALL GIRLS SERVICE IN ALL DELHI …

(Delhi) Call Girls in (Chanakyapuri)

Hot And Sexy Independent Model Escort Service In Delhi Unlimited Enjoy Genuine 100% Profiles And Trusted Door Step Call Girls Feel Free To Call Us Female Service Hot Busty & Sexy Party Girls Available For Complete Enjoyment. We Guarantee Full Satisfaction & In Case Of Any Unhappy Experience, We Would Refund Your Fees, Without Any Questions Asked. Feel Free To Call Us Female Service Provider Hours Opens Thanks.

Delhi Escorts Services 100% secure Services.Incall_OutCall Available and outcall Services provide.

We are available 24*7 for Full Night and short Time Escort Services all over Delhi NCR.

Delhi All Hotel Services available 3* 4* 5* Call Call

Delhi Escorts Services And Delhi Call Girl Agency 100% secure Services in my agency. Incall and outcall Services provide.

We are available 24*7 for Full Night and short Time Escort Services my agency in all over New Delhi

Delhi All Hotel Services available my agency

SERVICES [✓✓✓]

Housewife

College Girl

VIP Escort

Independent Girl

Aunty

Without a Condom sucking )?

Sexy Aunty.DSL (Dick Sucking Lips)?

DT (Dining at the Toes English Spanking)

Doggie (Sex style from no behind)??

OutCall- All Over Delhi Noida Gurgaon 24/7

FOR APPOINTMENT Call/Whatsop / 9953056974Call Girls in Ramesh Nagar Delhi 💯 Call Us 🔝9953056974 🔝 Escort Service

Call Girls in Ramesh Nagar Delhi 💯 Call Us 🔝9953056974 🔝 Escort Service9953056974 Low Rate Call Girls In Saket, Delhi NCR

Top Rated Pune Call Girls Budhwar Peth ⟟ 6297143586 ⟟ Call Me For Genuine Sex Service At Affordable Rate

Booking Contact Details

WhatsApp Chat: +91-6297143586

pune Escort Service includes providing maximum physical satisfaction to their clients as well as engaging conversation that keeps your time enjoyable and entertaining. Plus they look fabulously elegant; making an impressionable.

Independent Escorts pune understands the value of confidentiality and discretion - they will go the extra mile to meet your needs. Simply contact them via text messaging or through their online profiles; they'd be more than delighted to accommodate any request or arrange a romantic date or fun-filled night together.

We provide -

01-may-2024(v.n)

Top Rated Pune Call Girls Budhwar Peth ⟟ 6297143586 ⟟ Call Me For Genuine Se...

Top Rated Pune Call Girls Budhwar Peth ⟟ 6297143586 ⟟ Call Me For Genuine Se...Call Girls in Nagpur High Profile

Recently uploaded (20)

Coefficient of Thermal Expansion and their Importance.pptx

Coefficient of Thermal Expansion and their Importance.pptx

UNIT-V FMM.HYDRAULIC TURBINE - Construction and working

UNIT-V FMM.HYDRAULIC TURBINE - Construction and working

Intze Overhead Water Tank Design by Working Stress - IS Method.pdf

Intze Overhead Water Tank Design by Working Stress - IS Method.pdf

Call Girls in Ramesh Nagar Delhi 💯 Call Us 🔝9953056974 🔝 Escort Service

Call Girls in Ramesh Nagar Delhi 💯 Call Us 🔝9953056974 🔝 Escort Service

result management system report for college project

result management system report for college project

Top Rated Pune Call Girls Budhwar Peth ⟟ 6297143586 ⟟ Call Me For Genuine Se...

Top Rated Pune Call Girls Budhwar Peth ⟟ 6297143586 ⟟ Call Me For Genuine Se...

Call for Papers - African Journal of Biological Sciences, E-ISSN: 2663-2187, ...

Call for Papers - African Journal of Biological Sciences, E-ISSN: 2663-2187, ...

CCS335 _ Neural Networks and Deep Learning Laboratory_Lab Complete Record

CCS335 _ Neural Networks and Deep Learning Laboratory_Lab Complete Record

Call for Papers - Educational Administration: Theory and Practice, E-ISSN: 21...

Call for Papers - Educational Administration: Theory and Practice, E-ISSN: 21...

chapter 5.pptx: drainage and irrigation engineering

chapter 5.pptx: drainage and irrigation engineering

VIP Call Girls Ankleshwar 7001035870 Whatsapp Number, 24/07 Booking

VIP Call Girls Ankleshwar 7001035870 Whatsapp Number, 24/07 Booking

Tutorial10 solution

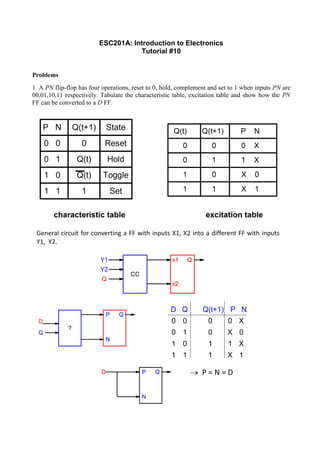

- 1. ESC201A: Introduction to Electronics Tutorial #10 Problems 1. A PN flip-flop has four operations, reset to 0, hold, complement and set to 1 when inputs PN are 00,01,10,11 respectively. Tabulate the characteristic table, excitation table and show how the PN FF can be converted to a D FF.

- 2. 2. A sequential circuit with two flip-flops A and B, two inputs x, y and a output z has the following behavior: ( 1) . . ; ( 1) . . ;A t x y x B B t x A x B z A . Draw the logic diagram of the circuit, list the state table and draw the state transition graph.

- 3. 3. Design a sequential circuit with two D flip-flops A and B and one input x such that when x = 0, the state of the circuit remains the same. When x = 1, the circuit goes through the state transitions from 00 to 01, to 11, to 10 and back to 00, and repeats. Present State Input Next State A B x 0 1 0 1 0 1 1 0 1 0 1 1 1 1 0 1 0 1 0 1 A B 0 0 0 0 DA DB 0 0 0 1 0 0 0 1 0 1 1 1 0 1 1 1 1 0 0 0 1 0 0 0 1 1 1 0 1 1 1 0 00 01 11 0 1 10 1 0 1 A Bx 1 1 00 01 11 0 1 10 1 A Bx 1 1 1 QD Ax B A Q BD A B

- 4. 4. Give a circuit realization of the combinational logic block shown in Fig. 1(a) to obtain the truth table shown in Fig. 1(b). Fig. 1(a) Fig. 1(b)

- 7. 5. The waveform of the clock as shown in Fig. 2(a) excites the circuit shown in Fig. 2(b). Sketch the output waveform. Fig. 2(a) Fig. 2(b)