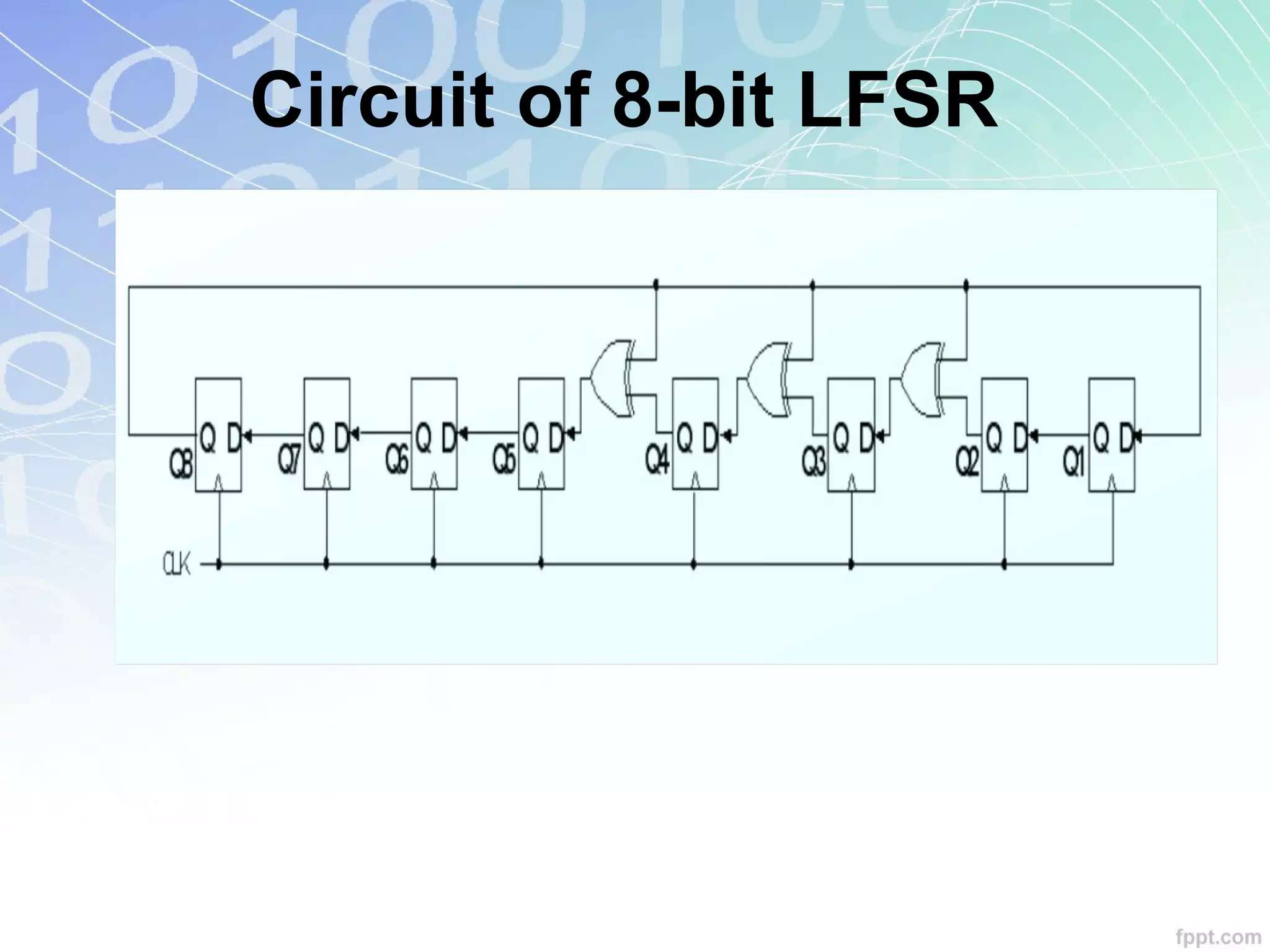

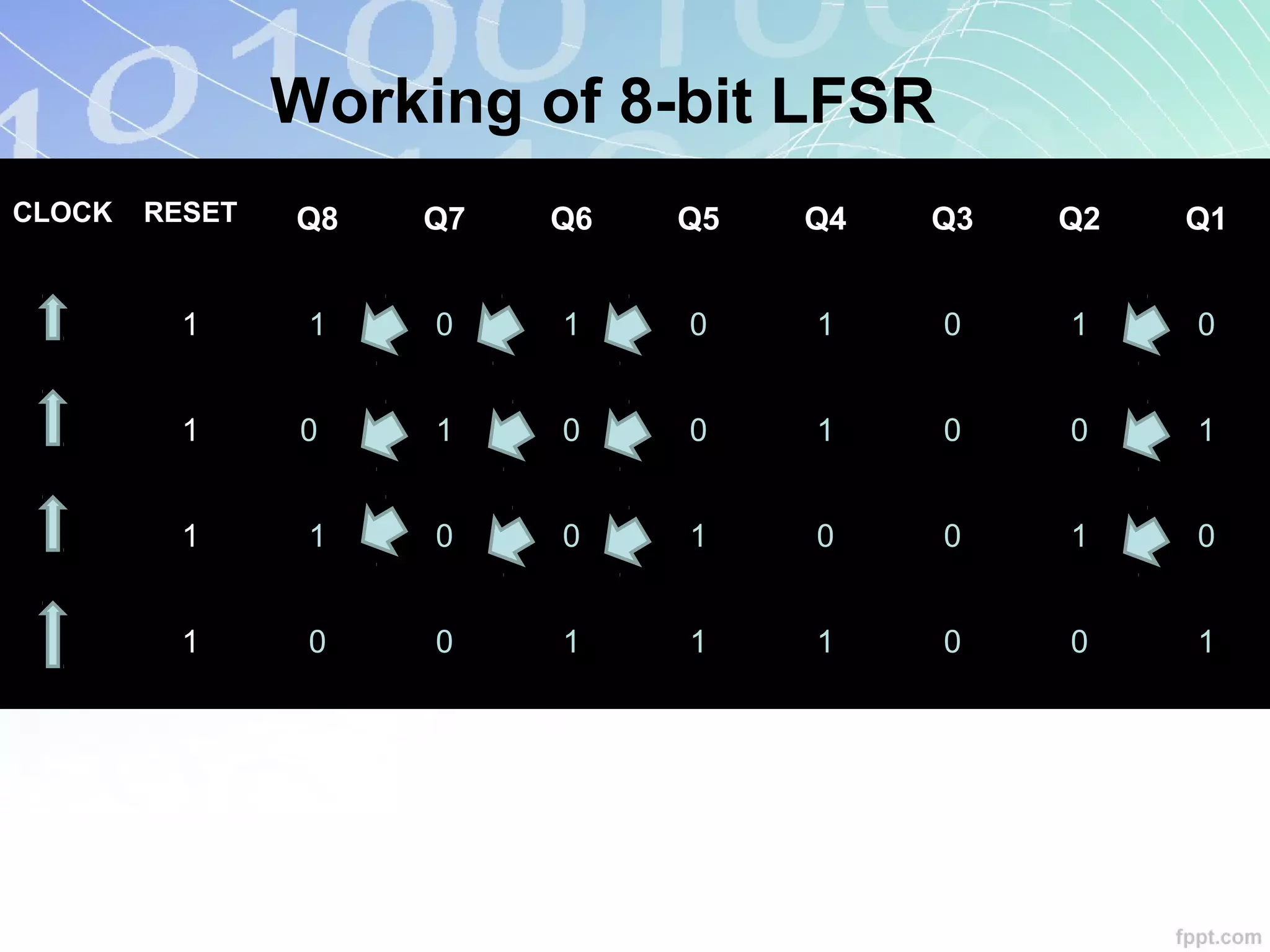

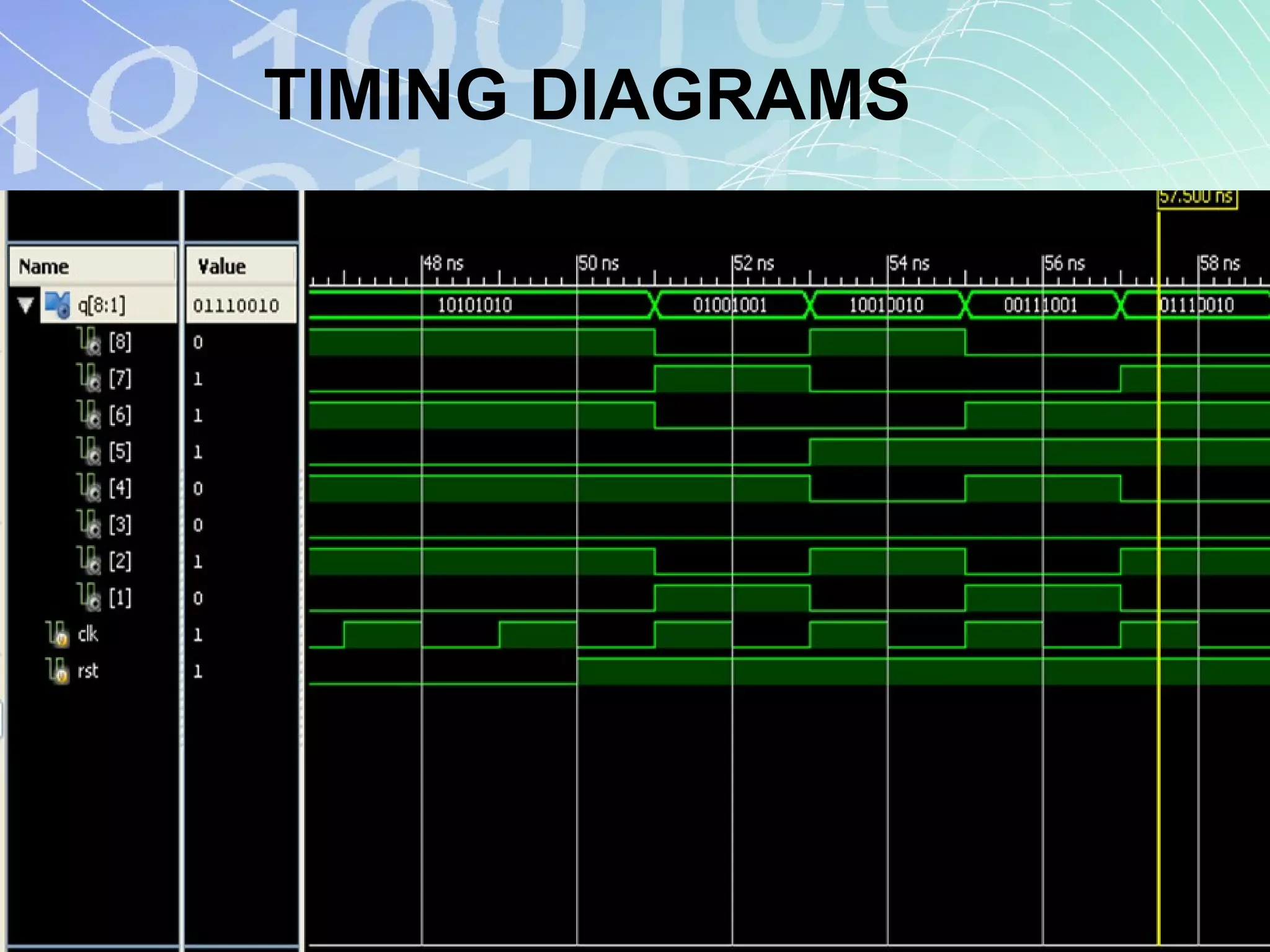

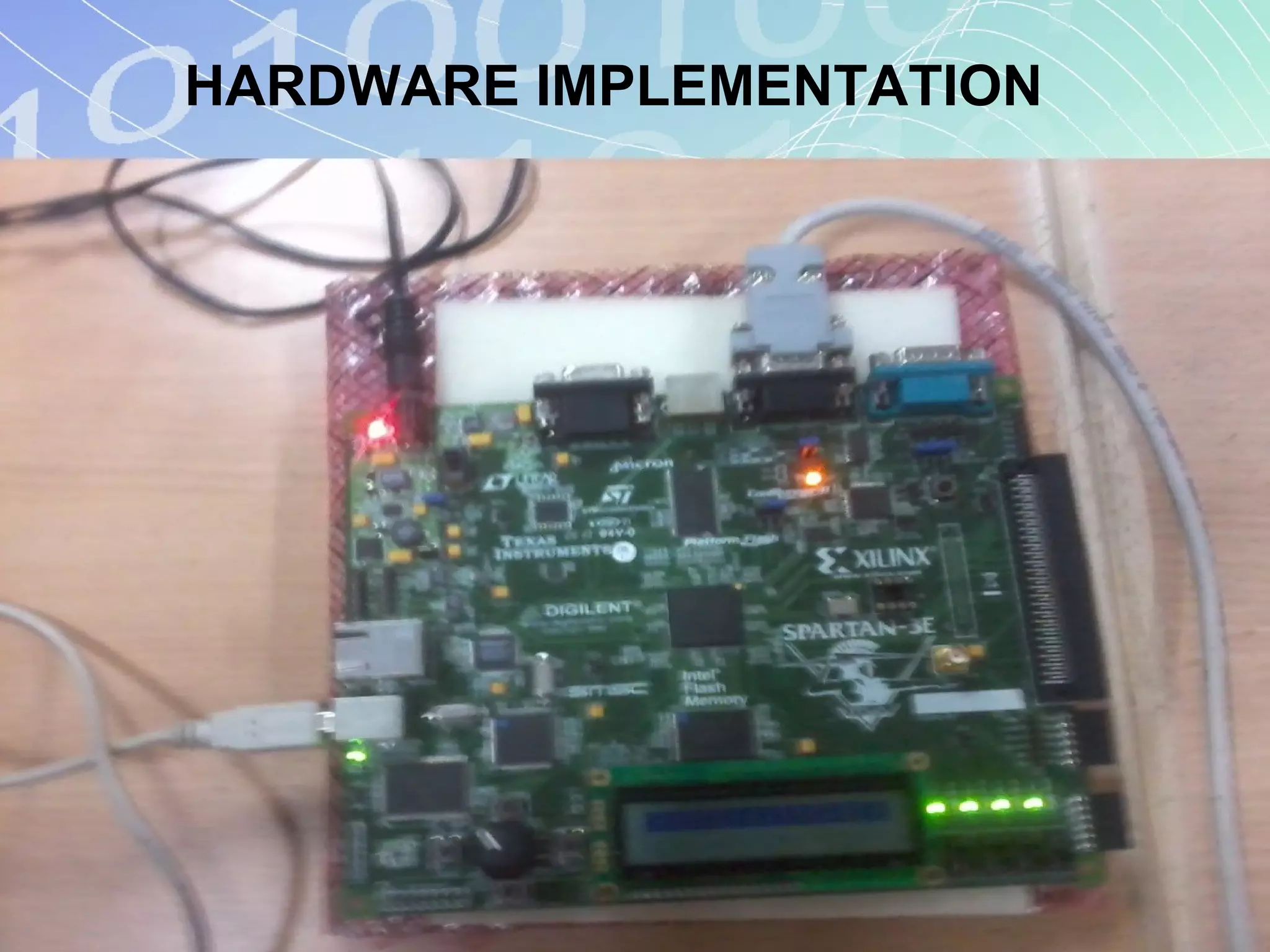

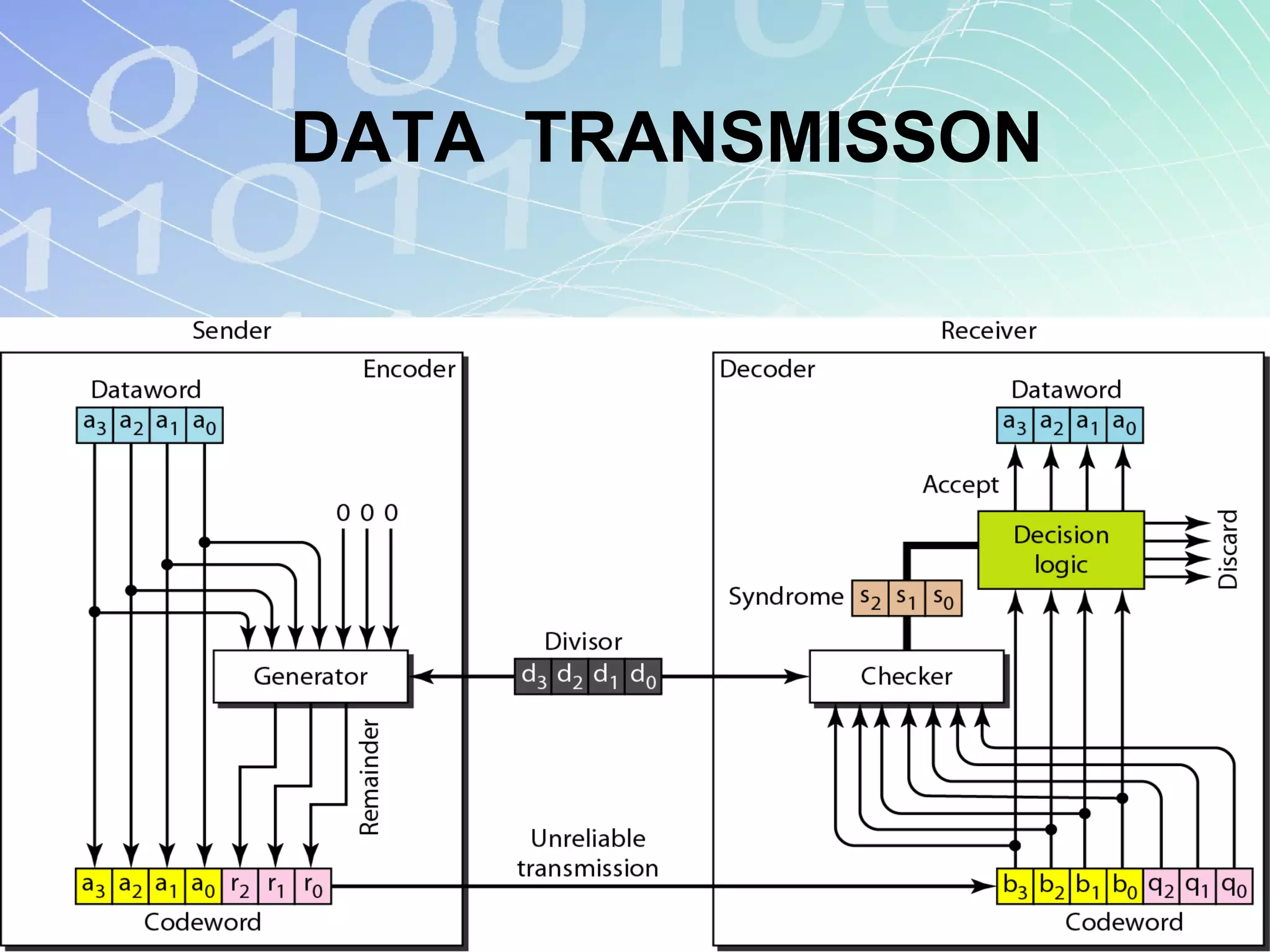

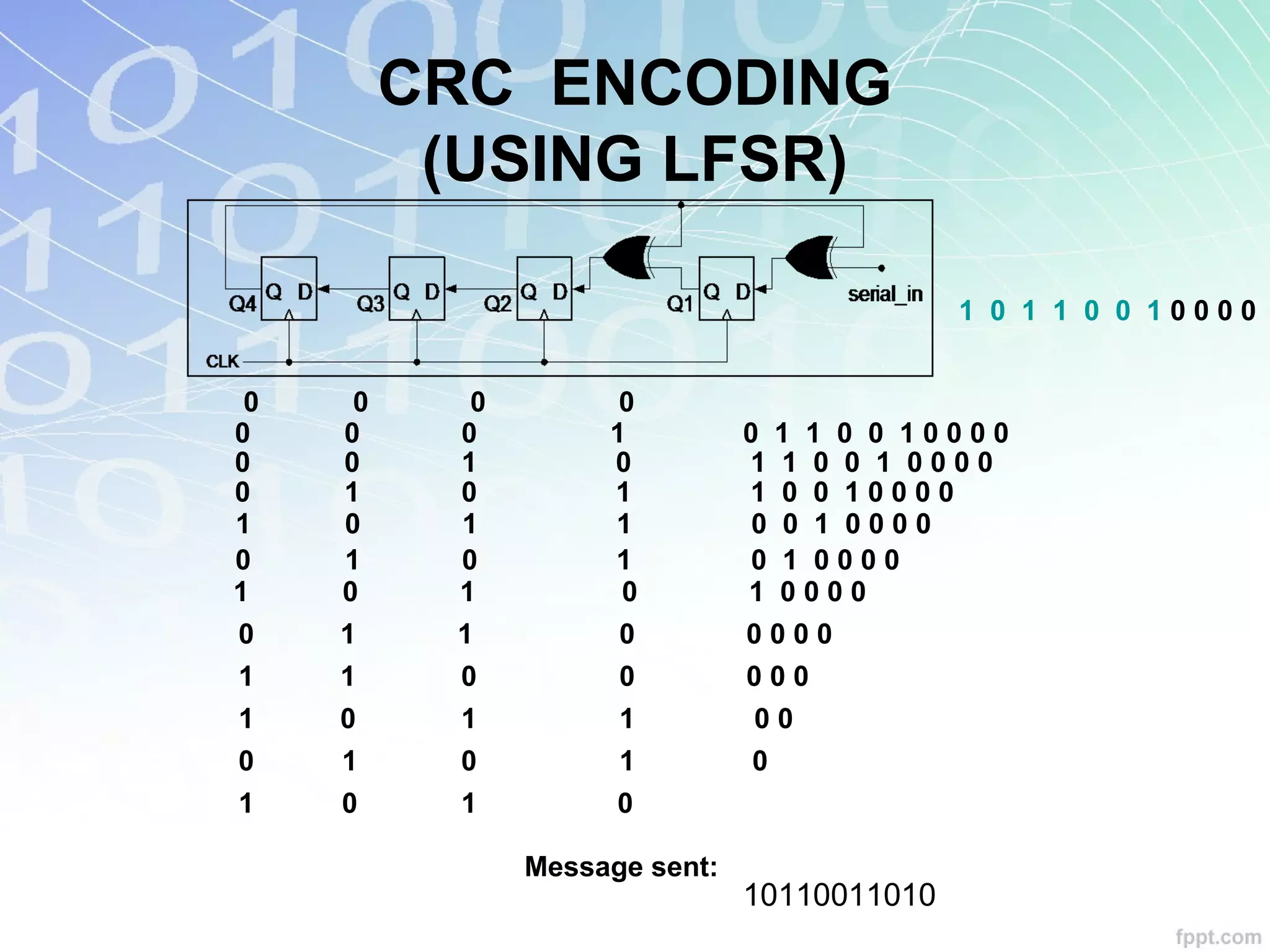

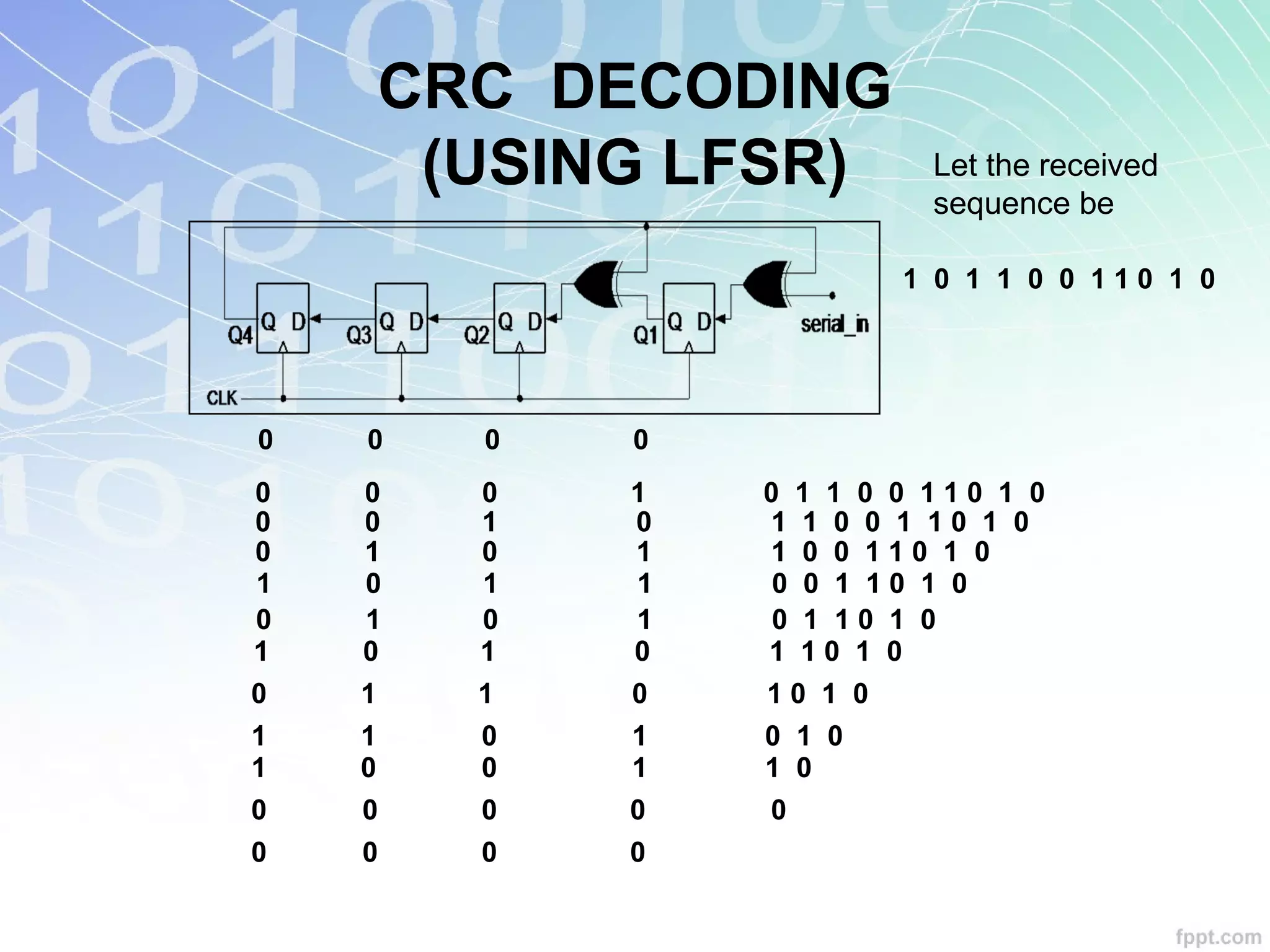

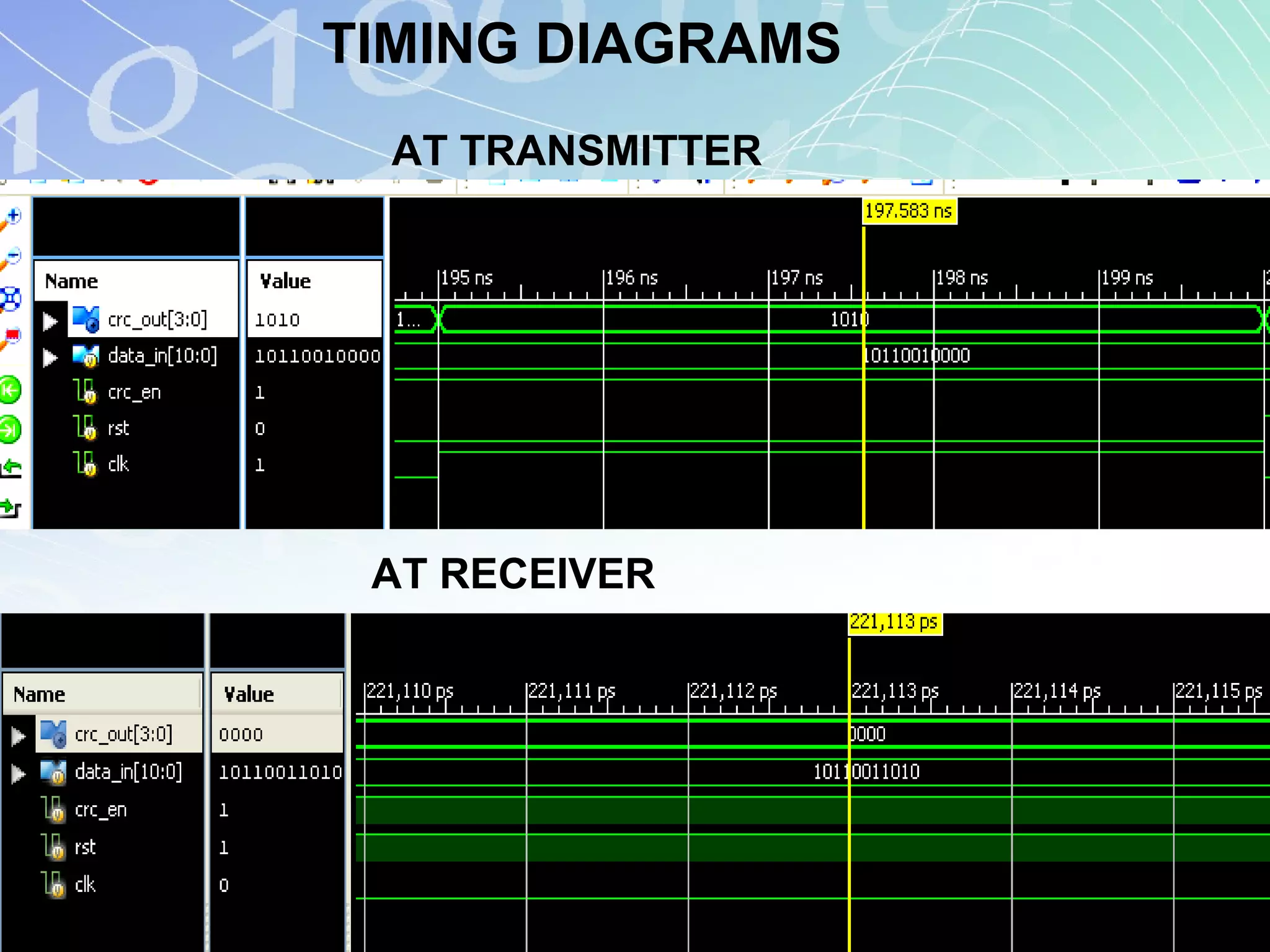

This document presents a mini project on linear feedback shift registers (LFSRs). It describes how an 8-bit LFSR works using 8 D-flip flops connected in a chain with outputs XORed together. The LFSR generates a pseudo-random sequence that repeats after 255 cycles. It discusses the circuit, working, and timing diagrams of the 8-bit LFSR. Applications mentioned include random number generation, error detection/correction, and implementing cyclic redundancy checks for data transmission.