chirag_patel

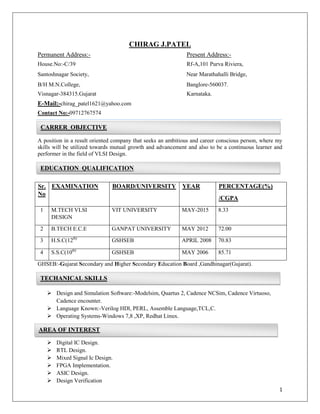

- 1. 1 CHIRAG J.PATEL Permanent Address:- Present Address:- House.No:-C/39 Rf-A,101 Purva Riviera, Santoshnagar Society, Near Marathahalli Bridge, B/H M.N.College, Banglore-560037. Visnagar-384315.Gujarat Karnataka. E-Mail:-chirag_patel1621@yahoo.com Contact No:-09712767574 A position in a result oriented company that seeks an ambitious and career conscious person, where my skills will be utilized towards mutual growth and advancement and also to be a continuous learner and performer in the field of VLSI Design. Sr. No EXAMINATION BOARD/UNIVERSITY YEAR PERCENTAGE(%) /CGPA 1 M.TECH VLSI DESIGN VIT UNIVERSITY MAY-2015 8.33 2 B.TECH E.C.E GANPAT UNIVERSITY MAY 2012 72.00 3 H.S.C(12th) GSHSEB APRIL 2008 70.83 4 S.S.C(10th) GSHSEB MAY 2006 85.71 GHSEB:-Gujarat Secondary and Higher Secondary Education Board ,Gandhinagar(Gujarat). Design and Simulation Software:-Modelsim, Quartus 2, Cadence NCSim, Cadence Virtuoso, Cadence encounter. Language Known:-Verilog HDl, PERL, Assemble Language,TCL,C. Operating Systems-Windows 7,8 ,XP, Redhat Linux. Digital IC Design. RTL Design. Mixed Signal Ic Design. FPGA Implementation. ASIC Design. Design Verification CARRER OBJECTIVE EDUCATION QUALIFICATION AREA OF INTEREST TECHANICAL SKILLS

- 2. 2 1.Title : Quasi T-coil CMOS power detector with self-bias embedded amplifier. Platform : Analog Design (Cadence Virtuoso)(4 Months) Description : Power detector (PD) using quasi T-coil matching network is designed. Further for Low Power detection Embedded amplifier is used with power detector circuit.The detector works on the nonlinear characteristics of short-channel MOS devices operating in either a saturation or subthreshold regime to generate a dc current that is proportional to the input RF signal power. The operating region of MOS devices depends on input RF power levels. 2.Title : Implementation of UART on FPGA.(4 Months) Platform : FPGA Design (Modelsim and Quartus 2) Description : Universal Asynchronous Receiver Transmitter (UART) is core of serial communication. At Transmitter side it convert parallel data into serial data and transmit it and at receiver side reverse process is done. Here we implement 9 bit UART 3.Title : VLSI Implementation of Efficient Lossless ECG Encoder Design Platform : ASIC Design(Cadence Tool)(4 Months) Description : VLSI implementation of low power area efficient electrocardiogram (ECG) signal encoder which can be used for wireless healthcare monitoring application. It also gives very high compression ratio. By studying Electrocardiogram signal simple adaptive predictor is designed which chooses one among two type of predictor as per the difference signal. 4.Title : Discrete Time Low Pass Filter Based Sigma Delta ADC. Platform : Mixed Signal (Cadence Virtuoso).(6 Month) Description : Sigma Delta Modulator based ADC Design with 5 Bit VCO based Quantizer and 1 bit DAC. VCO based Quantizer achieve first order noise shaping of its Quantization noise. The sigma Delta structure implemented with first order loop filter. “Quasi T-coil CMOS power detector with self-bias embedded amplifier” paper has been published in ‘IJSRD’ Volume 2, Issue 10, December 2014 Edition (ISSN 2321-0613). Father’s Name:-Jitendrakumar G.Patel. Mother’s Name:-Kalaben J.Patel. Date of Birth-5th October,1990. Marital Status-Single. Gender:-Male. Known Language-English, Hindi, Gujarati. Hobbies:-Watching Movie, Listening Songs. I here by declare that above mention information are true in the best of my knowledge. Chirag J.Patel PROJECT UNDERTAKEN PERSONAL INFORMATION DECLARATION PUBLICATION