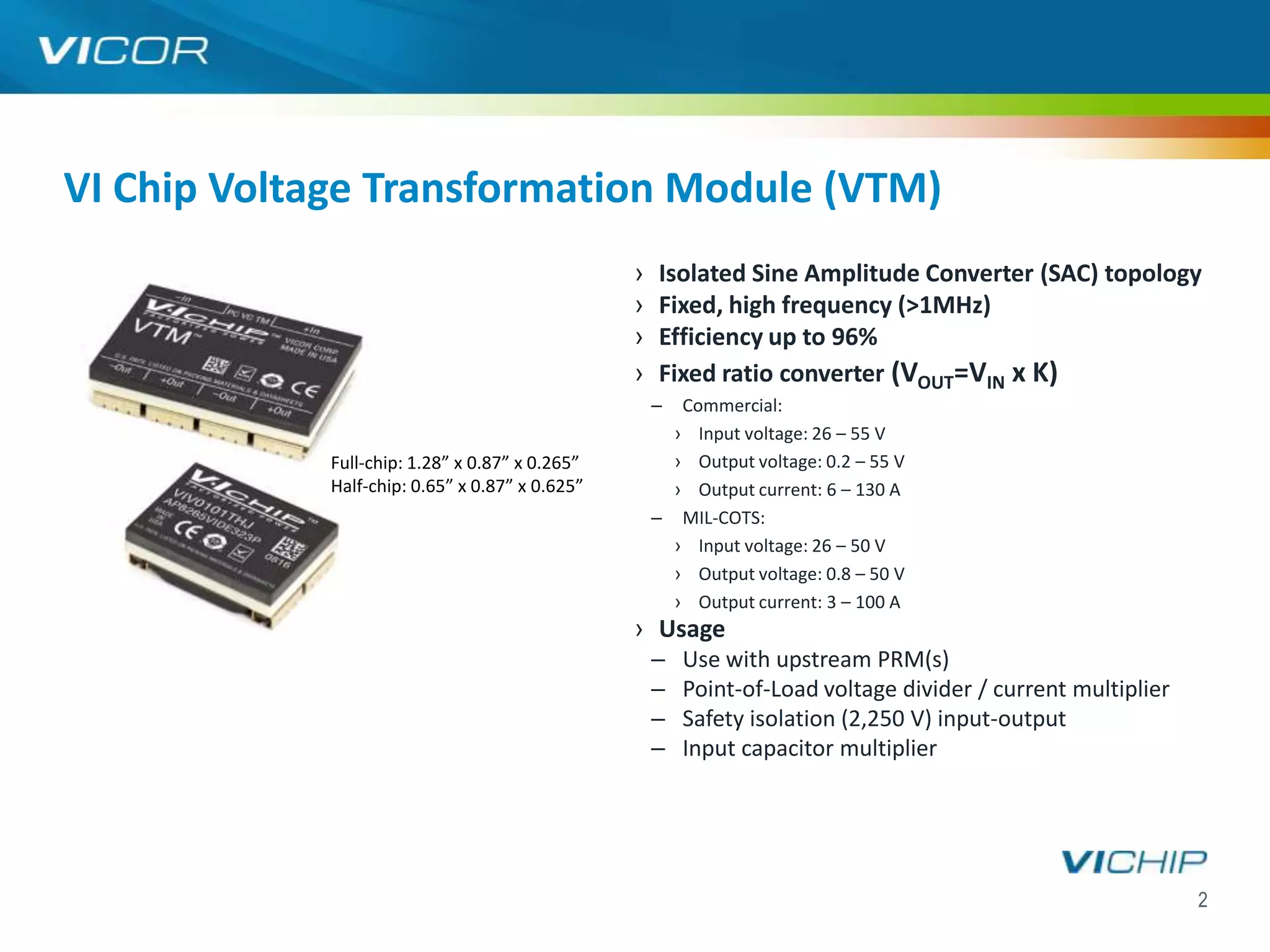

The VI Chip VTM® is an advanced voltage transformation module designed for high efficiency and power density, operating at a frequency greater than 1 MHz with efficiencies up to 96%. It supports a wide range of input and output voltages and currents, making it suitable for various applications, including point-of-load voltage conversion and safety isolation. Additionally, VI Chip technology offers flexibility and minimal power loss improvements, positioning it for future advancements in power conversion systems.