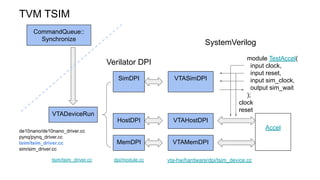

TVM uses Verilator and DPI to connect Verilog/Chisel accelerator models written in SystemVerilog/Chisel to Python code. It initializes the hardware model and controls simulation using methods like SimLaunch, SimWait, SimResume. The Python code loads the accelerator module, allocates memory, runs the accelerator by calling driver functions that interface with the DPI to initialize, launch and wait for completion of the accelerator. This allows accelerators developed in Verilog/Chisel to be tested from Python.

{

Module m = args[0];

DPILoader::Global()->Init(m);

});](https://image.slidesharecdn.com/tvmtsimveriloghdlchisel-200315081844/85/TVM-VTA-TSIM-6-320.jpg)

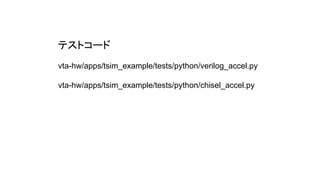

![TVM TSIM : apps/python (verilog_accel)

vta-hw/apps/tsim_example/tests/python/verilog_accel.py

def test_accel():

rmax = 64

dtype = "uint64"

n = np.random.randint(1, rmax)

c = np.random.randint(0, rmax)

ctx = tvm.cpu(0)

a = tvm.nd.array(np.random.randint(rmax, size=n).astype(dtype), ctx)

b = tvm.nd.array(np.zeros(n).astype(dtype), ctx)

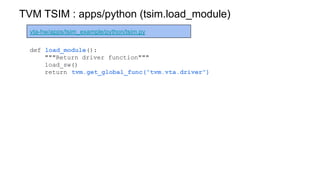

f = tsim.load_module() => 関数の獲得

cycles = f(a, b, c) => 関数の実行

msg = "cycles:{0:4} n:{1:2} c:{2:2}".format(cycles, n, c)

np.testing.assert_equal( b.asnumpy(), a.asnumpy() + c, err_msg = "[FAIL] " +

msg)

print("[PASS] " + msg)](https://image.slidesharecdn.com/tvmtsimveriloghdlchisel-200315081844/85/TVM-VTA-TSIM-12-320.jpg)

![TVM TSIM : apps/python (chisel_accel)

vta-hw/apps/tsim_example/tests/python/chisel_accel.py

def test_accel():

rmax = 64

dtype = "uint64"

n = np.random.randint(1, rmax)

c = np.random.randint(0, rmax)

ctx = tvm.cpu(0)

a = tvm.nd.array(np.random.randint(rmax, size=n).astype(dtype), ctx)

b = tvm.nd.array(np.zeros(n).astype(dtype), ctx)

f = tsim.load_module() => 関数の獲得

cycles = f(a, b, c) => 関数の実行

msg = "cycles:{0:4} n:{1:2} c:{2:2}".format(cycles, n, c)

np.testing.assert_equal( b.asnumpy(), a.asnumpy() + c, err_msg = "[FAIL] " +

msg)

print("[PASS] " + msg)](https://image.slidesharecdn.com/tvmtsimveriloghdlchisel-200315081844/85/TVM-VTA-TSIM-13-320.jpg)

{

Device dev_;

DLTensor* A = args[0];

DLTensor* B = args[1];

uint32_t c = static_cast<int>(args[2]);

uint32_t cycles = dev_.Run(c, A, B);

*rv = static_cast<int>(cycles);

});](https://image.slidesharecdn.com/tvmtsimveriloghdlchisel-200315081844/85/TVM-VTA-TSIM-15-320.jpg)

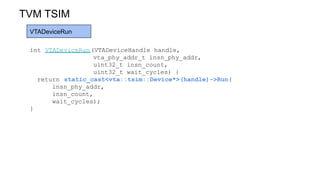

![TVM TSIM : dev_.Run

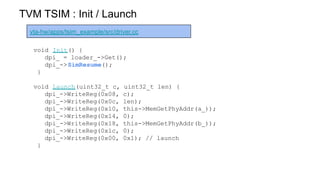

vta-hw/apps/tsim_example/src/driver.cc

uint32_t Run(uint32_t c, DLTensor* a, DLTensor* b) {

uint32_t cycles;

uint32_t len = a->shape[0];

size_t size = (a->dtype.bits >> 3) * len;

a_ = this->MemAlloc(size);

b_ = this->MemAlloc(size);

this->MemCopyFromHost(a_, a->data, size);

this->Init();

this->Launch(c, len);

cycles = this->WaitForCompletion();

this->MemCopyToHost(b->data, b_, size);

this->MemFree(a_);

this->MemFree(b_);

return cycles;

}](https://image.slidesharecdn.com/tvmtsimveriloghdlchisel-200315081844/85/TVM-VTA-TSIM-16-320.jpg)

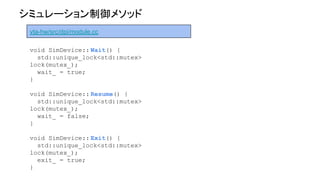

![シミュレーション制御メソッド

vta-hw/src/dpi/module.cc

void SimLaunch() {

auto frun = [this]() {

(*ftsim_)();

};

tsim_thread_ = std::thread(frun);

}

void SimFinish() {

sim_device_. Exit();

tsim_thread_.join();

}

void SimWait() {

sim_device_. Wait();

}

void SimResume() {

sim_device_. Resume();

}

~DPILoader() {

dpi_->SimResume();

dpi_->SimFinish();

}}

class DPILoader {

void Init(Module module)

{

mod_ = module;

dpi_ = this->Get();

dpi_->SimLaunch();

dpi_->SimWait();

}](https://image.slidesharecdn.com/tvmtsimveriloghdlchisel-200315081844/85/TVM-VTA-TSIM-20-320.jpg)

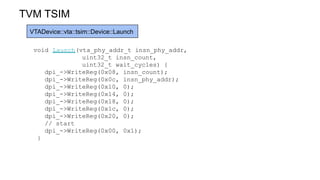

{

Module m = args[0];

DPILoader::Global()-> Init(m);

});

class DPILoader {

void Init(Module module)

{

mod_ = module;

dpi_ = this->Get();

dpi_->SimLaunch();

dpi_->SimWait();

}](https://image.slidesharecdn.com/tvmtsimveriloghdlchisel-200315081844/85/TVM-VTA-TSIM-21-320.jpg)